(54) ПРОЦЕССОР УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ

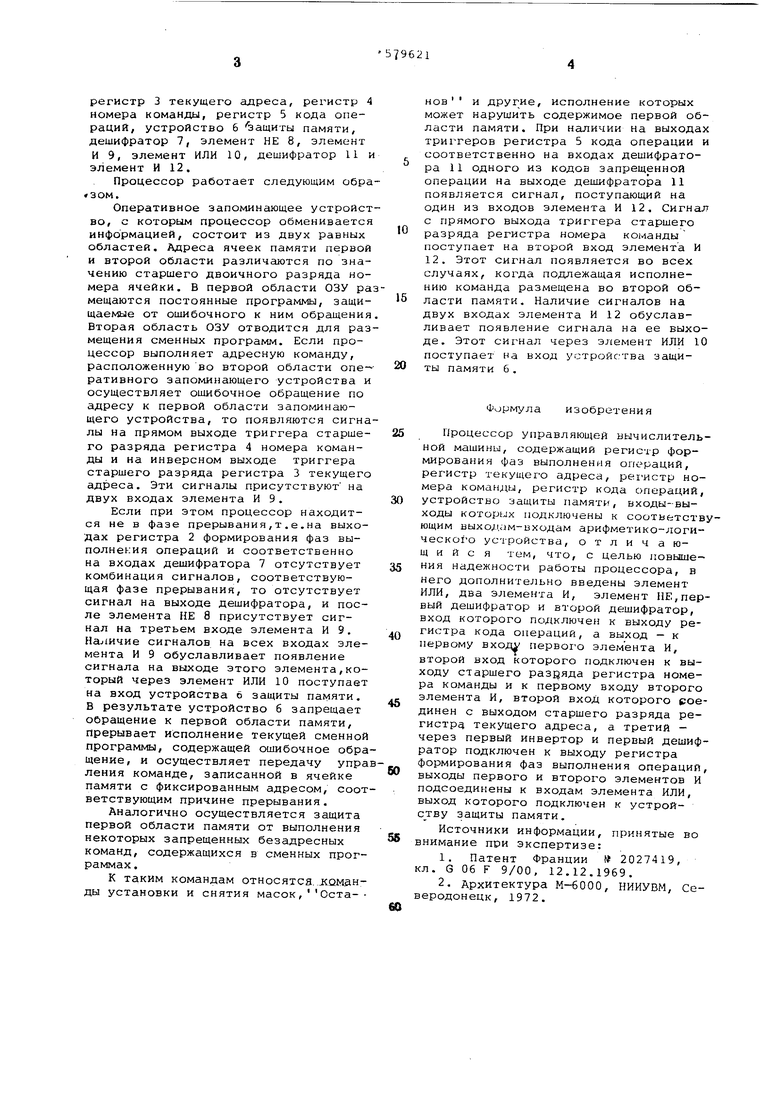

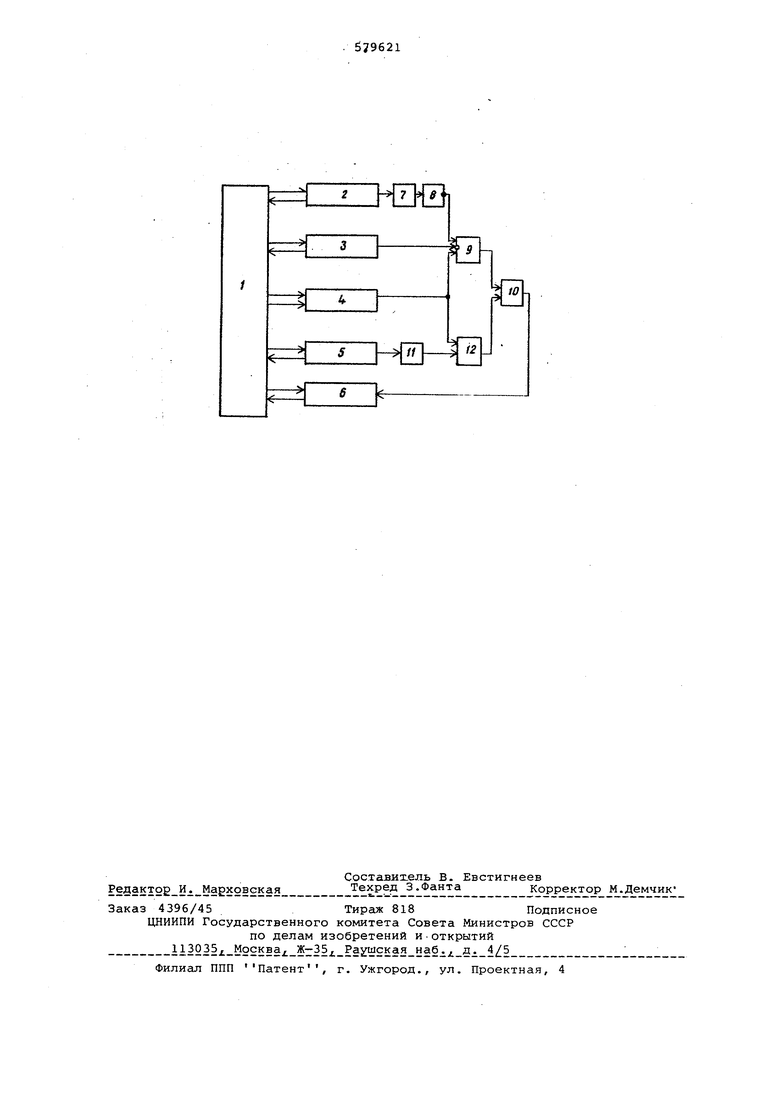

регистр 3 текущего адреса, регистр 4 номера команды, регистр 5 кода операций, устройство 6 защиты памяти, дешифратор 7, элемент НЕ 8, э шмент И 9, элемент ИЛИ 10, дешифратор 11 и элемент И 12.

Процессор работает следующим обра зом.

Оперативное запоминающее устройство, с KOTopfciM процессор обменивается информацией, состоит из двух равных областей. Адреса ячеек памяти первой и второй области различаются по значению старшего двоичного разряда номера ячейки. В первой области ОЗУ рамещаются постоянные программы, защищаемые от ошибочного к ним обращения Вторая область ОЗУ отводится для размещения сменных программ. Если процессор выполняет адресную команду, расположенную во второй области one- ративного запоминающего устройства и осуществляет ошибочное обращение по адресу к первой области запоминающего устройства, то появляются сигналы на прямом выходе триггера старшего разряда регистра 4 номера команды и на инверсном выходе триггера старшего разряда регистра 3 текущего адреса. Эти сигналы присутствуют на двух входах элемента И 9.

Если при этом процессор находится не в фазе прерывания,т.е.на выходах регистра 2 формирования фаз выполнекия операций и соответственно на входах дешифратора 7 отсутствует комбинация сигналов, соответствующая фазе прерывания, то отсутствует сигнал на выходе дешифратора, и после элемента НЕ 8 присутствует сигнал на третьем входе элемента И 9. HajiH4He сигналов на всех входах элемента И 9 обуславливает появление сигнала на выходе этого элемента,который через элемент ИЛИ 10 поступает на вход устройства 6 защиты памяти. В результате устройство 6 запрещает Обращение к первой области памяти, прерывает исполнение текущей сменной программы, содержащей ошибочное обращение, и осуществляет передачу упраления команде, записанной в ячейке памяти с фиксированным адресом, соответствующим причине прерывания.

Аналогично осуществляется защита первой области памяти от выполнения некоторых запрещенных безадресных команд, содержащихся в сменных программах.

К таким командам относятся, хоманды установки и снятия масок,Оста-

нов и другие, исполнение которых может нарушить содержимое первой области памяти. При наличии на выходах триггеров регистра 5 кода операции и соответственно на входах дешифратора 1 1 одного из кодов запрещенной операции на выходе дешифратора 11 появляется сигнал, поступающий на один из входов элемента И 12. Сигнал с прямого выхода триггера старшего разряда регистра номера команды поступает на второй вход элемента И 12. Этот сигнал появляется во всех случаях, когда подлежащая исполнению команда размещена во второй области памяти. Наличие сигналов на двух входах элемента И 12 обуславливает появление сигнала на ее выходе. Этот сигнал через элемент ИЛИ 10 поступает на вход устройства защиты памяти б.

Формула изобретения

Процессор управляюи ей вычислительной машины, содержащий регистр формирования фаз выполнения оггераций, регистр текущего адреса, регистр номера команды, регистр кода операций, устройство защиты памяти, входы-выходы которых подключены к соответствующим выходам-входам арифметико-логического устройства, отличающийся тем, что, с целью 1овышения надежности работы процессора, в него дополнительно введены элемент ИЛИ, два элемента И, элемент НЕ,первый дешифратор и второй дешифратор, вход которого подключен к выходу регистра кода операций, а выход - к первому входу первого элемента И, второй вход которого подключен к выходу старшего разряда регистра номера команды и к первому входу второго элемента И, второй вход которого роединен с выходом старшего разряда регистру текущего адреса, а третий через первый инвертор и первый дешифратор подключен к выходу регистра формирования фаз выполнения операций, выходы первого и второго элементов И подсоединены к входам элемента ИЛИ, выход которого подключен к устройству защиты памяти.

Источники информации, принятые во внимание при экспертизе:

1.Патент Франции № 2027419, кл. 6 06 F 9/00. 12.12.1969.

2.Архитектура , НИИУВМ, Северодонецк, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1501065A1 |

| Устройство для контроля программ | 1985 |

|

SU1251128A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

Авторы

Даты

1977-11-05—Публикация

1975-12-17—Подача