Изобретение относится к областйа8 тематики и вычислительной техники.

Известны накопители для постоянных запоминающих устройств (ПЗУ), содержащие матрицу адресных и разрядных шин, в одних из пересечений которых включены элементы связи 1.

Недостатком таких, накопителей для ПЗУ является сравнительно большой уррвень помех нуля на разрядных шинах, обусловленных паразитными связями между разрядными шинами и связями через элементы связи выбранной адресно шины с остальными невыбранннми адресными шинами. При этом уровень помех нуля возрастает при увеличении инфор мационной емкости накопителя.

Целью изобретения является повышение надежности работы накопителя.

Эта цель достигается тем, что в предложенном накопителе, содержащем матрицу адресных и разрядных шин, в одних из пересечений которых включены элементы связи, в других пересечем ниях адресных и разрядных шин содердатся ключевые элементы, например транзисторы, коллекторы и базы которых подключены соответственно к разряднь ли и адресным шинам, а эмиттер к шиНчг нулевого потенциала.

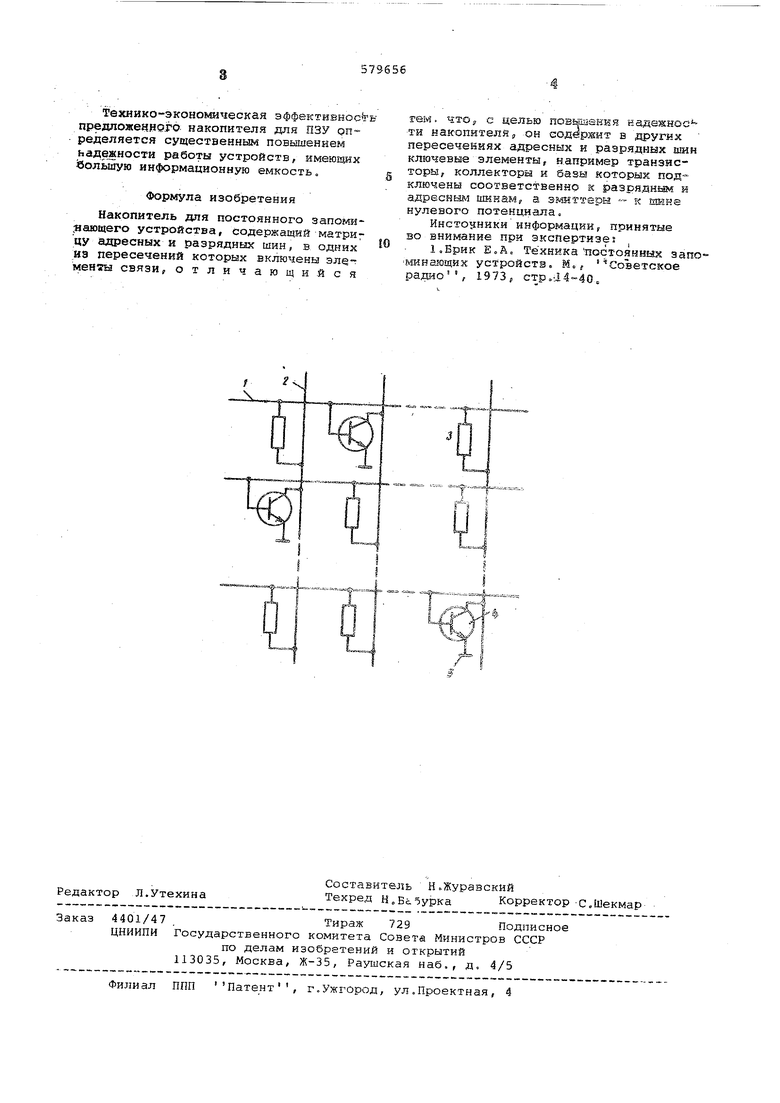

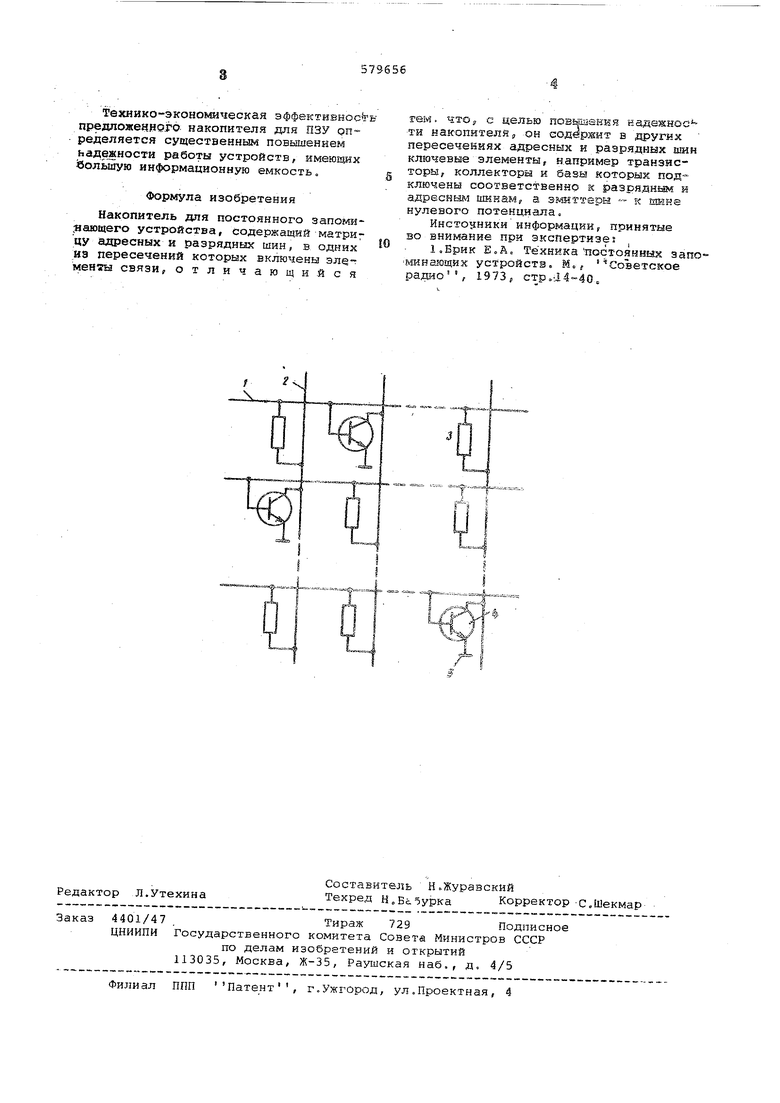

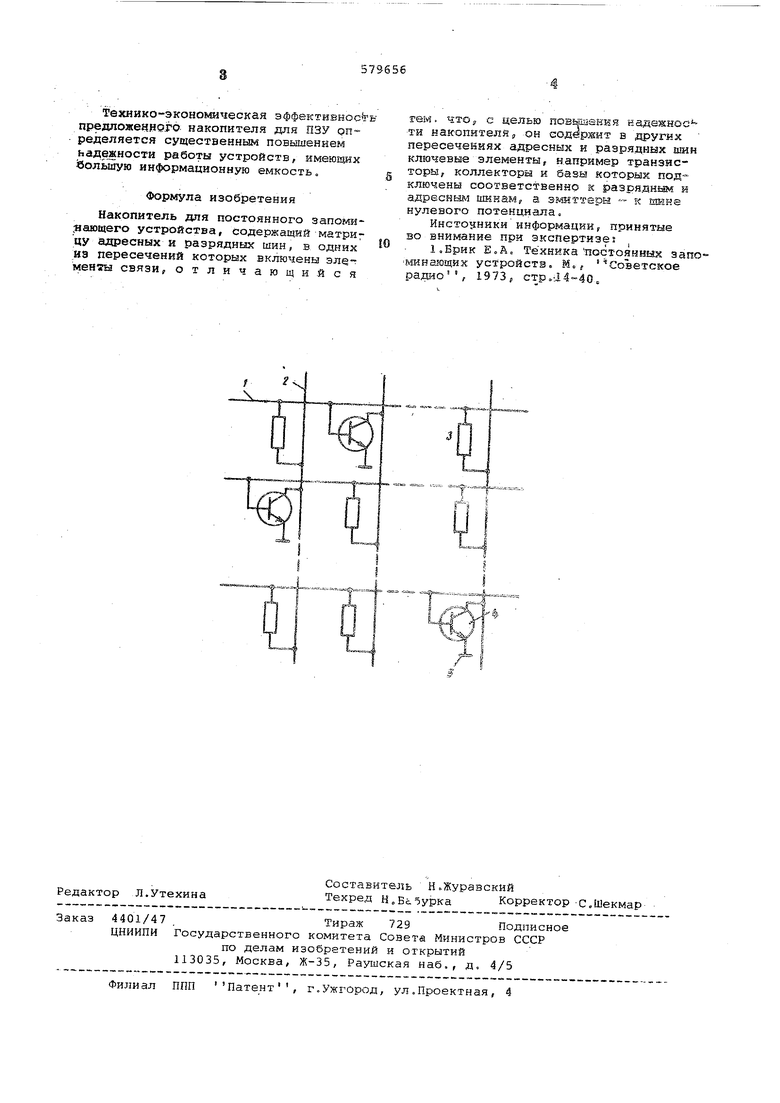

На чертеже представлена схема накопителя .

Накопитель содержит матрицу адресгных 1 и разрядных 2 шин, в одних из пересечений которых включены элементы связи 3. В других пересечениях включены транзисторы 4, коллекторы и базы которых подключены соответственно к разрядным 2 и адресным 1 шинам, а эмиттеры - к шине 5 нулевого потенциала.

Показан набор, кодов 10. . .1 01. . .1

11. . .0

Накопитель работает следующим образом.

При поступлении сигнала чтения наодну из адресных шин 1 через элементу связи, возникают сигналы единиц.. Одновременно сигнал чтения открываеттранзисторы, подключенные к выбраннор адресной шине. На разрядных шинах, подключенных к открытым транзисторам в момент чтения уровень напряжения близок к нулю. Это исключает появление помех нуля на соответствующих ра рядных шинах.

Технико-экономическая эффективнос гпредложенного накопителя для ПЗУ определяется существенным повышением надежности работы устройств, имеюпщх большую информационную емкость,

Формула изобретения

Накопитель для постоянного запоми.«ающего устройства, содержащий матриц цу адресных и разряднЕлх шин, в одних из пересечений которых включены ментьа связи, отличающийся

гем. что, с целью повыыакия надежнос-тн накопителя, он содержит в других пересечениях адресных и разрядных шин ключевые элементы, например транзисторы, коллекторы и базы которых подключены соответственно к разрядной и адреснш.- шкнам, а эмиттеры - к шине нулевого потенциала.

Инстоуники информации, принятые во внимание при экспертизе;

l.BpHK ЕоА, ТехникаnocTOHHHtsx запомккаящих устройств. М., Советское радио , 1973, строа4 40.

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для постоянного запоминающего устройства | 1976 |

|

SU579655A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Постоянное запоминающее устройство | 1976 |

|

SU744729A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Матричный накопитель | 1979 |

|

SU773728A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| Накопитель для постоянного запо-МиНАющЕгО уСТРОйСТВА | 1979 |

|

SU841045A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU637870A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

Авторы

Даты

1977-11-05—Публикация

1976-04-26—Подача