(54) НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Матричный накопитель | 1979 |

|

SU773728A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU763969A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU637870A1 |

| Матричный накопитель | 1979 |

|

SU799007A1 |

| Запоминающий модуль для постоянной памяти | 1981 |

|

SU991510A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении интегральных постоянных запоминающих устройств (ПЗУ).

Известен накопитель ПЗУ, содержащий числовые и разрядные шины, в местах пересечения которых включены элементы связи, например транзисторы 1.

Недостатком такого накопителя является большое количество числовых и разрядных шин (не менее (, где М - информационная емкость накопителя), а следовательно, и большое количество выводов накопителя.

Известен также накопитель ПЗУ, содержащий числовые и разрядные шины, в местах пересечения которых включены элементы связи (диоды) 2.

Недостатком данного накопителя также является большое количество числовых и разрядных шин (не менее ).

Наиболее близким к предлагаемому является накопитель ПЗУ, содержащий числовые и разрядные шины и транзисторы, затворы которых соединены с числовыми щинами, а истоки и стоки - с разрядными шинами. Транзисторы являются элементами

связи и наличие или отсутствие тако1о транзистора соответствует «1.-; или «О двоичной информации, хранимой на пересечении числовой и разрядной шин 3.

Недостатком такого устройства является большое количество числовых и разрядных шин (не менее ), причем указанный минимум достигается лишь в случае равенства количества слов и количества разрядов в слове, что не всегда бывает удобно. Кроме того, каждый элемент связи накопителя может хранить ограниченный объем информации.

Цель изобретения - увеличение информационной емкости и расширение области применения за счет обеспечения записи логических функций.

S

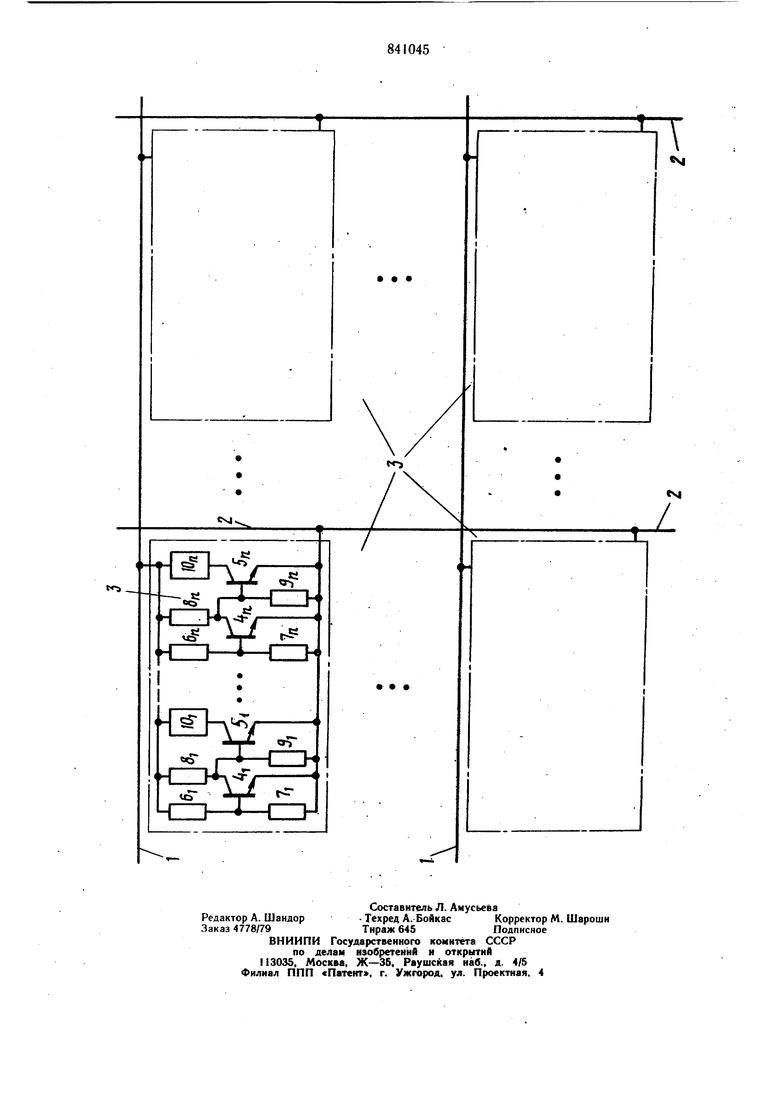

Поставленная цель достигается тем, что в накопителе для постоянного запоминающего устройства, содержащем числовые и разрядные шииы, в местах пересечения которых включены элементы связи, каждый разряд элемента связи содержит т)анзисторы, эмиттеры которых подключены к разрядной шине, а коллекторы соответственно через первый резистор и резистивный элемент подключены к числовой шине, база первого транзистора подключена к одним выводам второго и третьего рёзисторов, другие выводы которых подключены соответственно к числовой и разрядной шинам, база второго транзистора подключена непосредственно к коллектору первого транзистора и через четвертый резистор - к разрядной шине. На чертеже схематически представлен накопитель для ПЗУ. Накопитель содержит числовые шины 1, разрядные шины 2 и элементы 3 связи. Каждый из разрядов элементов связи содержит п транзисторов 4| - 4, п транзисторов 5| - 5л, резисторы 6/ - 6/,, 7i - 1п 8 - 8л, 9( - 9/t, а также п резистивных элементов 10i-Юл. Резистивными элементами могут быть,, например, плавкие перемычки, резисторы и т. д. На рассматриваемый элемент связи подается напряжение Use. При напряжении на нем Pi транзистор 4 (1 1, 2, ..., п) открывается. При напряжении dL на элементе связи транзистор 5t открывается, транзистор 4i при этом закрыт. Устройство работает следующим образом. Пусть выполнено условие (1), чего можно достигнуть выбором номиналов резисторов 6, 7, 8, 9. Тогда, очевидно, в случае подачи На элемент связи напряжения Ujie. Ut (условие (2) напряжение на резистивном элементе IQt будет близко к Ut, а напряжение на остальных резистивных элементах 10 близко к нулю. Пусть высокому сопротивлению элемента связи соответствует «О двоичной информации, а низкому - «h двоичной информации. Р2... Р Cde.-. -cf/t d, РГ d3 d 2 p 2 d di Ut pf Pi., U,dif, Тогда п-разрядное двоичное слово можно закодировать в одном элементе 3 свяви следующим образом. Если разряд слова равен «О, резистивный элемент lOi должен быть высокоомным. Если же i-тый разряд слова равен «1, то резистивный элемент lOt должен быть низкоомным. В последнем случае сопротивление элемента lOi выбирается так, чтобы ток, протекающий по нему при Upe Uj был много больше суммы токов, текущих через резисторы 6 и 8, входящие в элементы связи, под люченные к той же разрядной шине, что и рассматриваемый элемент связи. Сопротивления резистивных элементов 10, соответствующие кодируемому п-разрядному двоичному слову, задаются либо при изготовлении накопителя, либо с помощью специального кодирования после изготовления, например, с помощью пережигания резистивных элементов (изготовленных в виде плавких перемычек) за счет пропускания по ним тока при приложении к элементу связи достаточно длинных импульсов напряжения Uj. Если выполнены перечисленные условия, то, подавая на элемент 3 связи напряжение и (I i п) и контролируя величину тока, протекающего по соответствующей разрядной шине, можно считать содержимое .зюбой из п бит, закодированных в этом элементе связи. Если же условие (1) дополнить, например, условием (3), ds п-, Р/г-2,1 То помимо считывания отдельных бит из элемента 3 связи, возможно считать также логические п-1 пар бит. Следователь но, каждый элемент связи может быть использован для хранения не только п бит, но и их логических функций. Формула изобретения Накопитель для постоянного запоминающего устройства, содержащий числовые и разрядные шины, в местах пересечения которых включены элементы связи, отличающееся тем, что, с целью увеличения информационной емкости и расширения области применения за счет обеспечения записи логических функций, каждый разряд элемента связи содержит транзисторы, эмиттеры которых подключены к .разрядной шине, а коллекто|5ы соответственно через первый резистор и резистивный элемент подключены К числовой щине, база первого транзистора подключена к одним выводам второго и третьего резисторов, другие выводы которых подключены соответственно к числовой и разрядной шинам, база второго транзистора подключена непосредственно к коллектору первого транзистора и через четвертый резистор - к разрядной шине. Источники информации, принятые во внимание при экспертизе 1.Патент США Я 3976983, кл. 340-473 опублик. 1976. 2.Патент США № 341614, кл. 340-173,. опублик. 1970. 3.Авторское свидетельство СССР №641498, кл. О II С 11/40, 1978 (прототип).

М

Авторы

Даты

1981-06-23—Публикация

1979-05-31—Подача