1

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств на биполярных транзисторных структурах.5

Известен накопитель постоянных запоминающих устройств, собранный на биполярных транзисторах, в которых запись информации производится путем Подачи злектрических сигналов на 10 соответствующие внешние выводы l.

Недостатком накопителя, где запоминающие элементы включены в цепь коллектора транзистора, является недостаточно высокая плотность ин- 5 формации.

Наиболее близким по технической сущности к предлагаемому является накопитель, содержащий числовые шины, разрядные шины, соединенные 20 с числовыми шинами посредством диодов и запоминающих элементов, транзисторы, эмиттеры которых соединены с разрядными шинами, коллекторы - с выходными шина1 и, а базы посредством 25 резисторов соединены с входными шинами накопителя {2.

Недостатком такого накопителя является большое число внешних выводов , что требует большого коли- 30

чества оборудования, а это, в свою очередь, приводит к увеличению стоимости всего ПЗУ, увеличению потребляемой мощности и снижению быстродействия.

Цель изобретения - упрощение устройства.

Поставленная цель достигается темчто в матричный накопитель, содержащий последовательно соединенные запоминакнцие элементы и диоды, которые подключены между числовыми и разрядг ными шинами, транзисторы, коллекторы которых подключены к выходным шинам, эмиттеры - к разрядным шинам, а базы - через резисторы к входным шинам. введены группы транзисторов и первые и вторые адресные шины, причем коллекторы транзисторов первой группы подключены к числовым шинам, базы к первым адресным шинам, а эмиттеры подключены к коллекторам транзисторов второй группы, которые через резисторы подключены к шине питания, базы транзисторов второй группы подключены ко вторым адресным шинам, а эмиттеры - к общей шине накопителя.

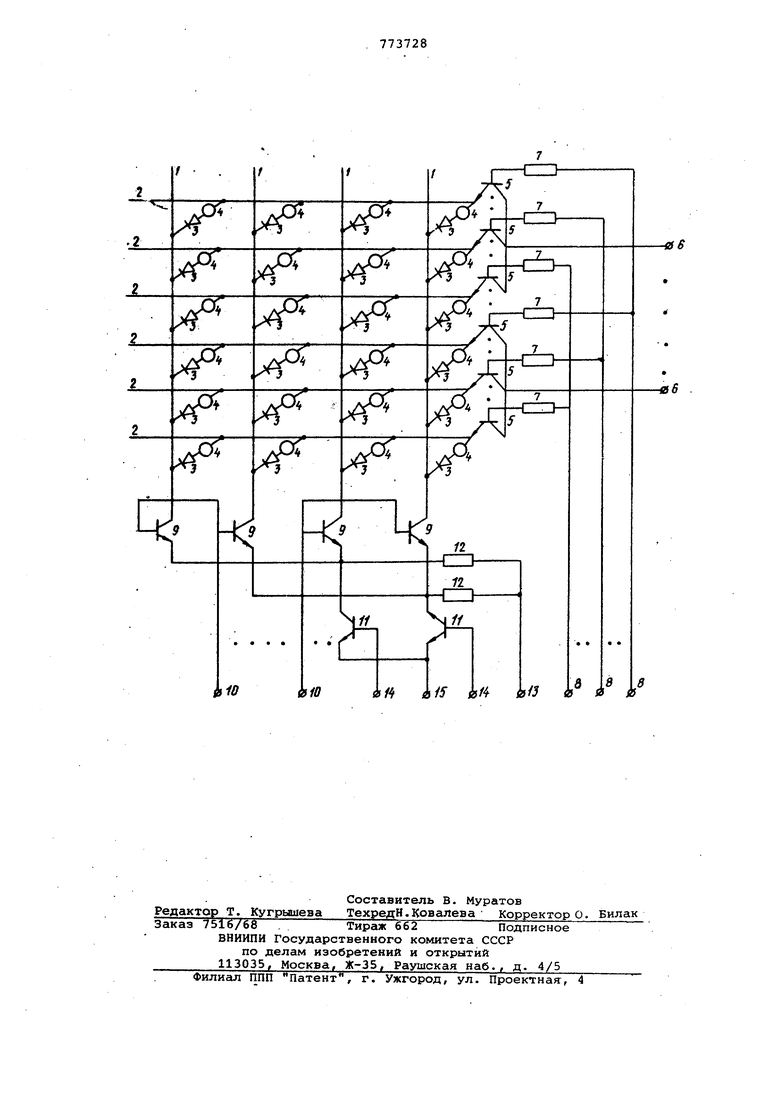

На чертеже показана электрическая схемаматричного накопителя.

Устройство содержит числовые шины 1 и разрядные шины 2, соединенные между собой.диодами, 3, и запоминающие элементы 4, к разряднь м шинам подключены эмиттеры транзисторов 5, коллекторы которых соединены с выходными шинами б, а базы - с резисторами 7. Другие выводы резисторов 7 подключены ко входным шинам 8, коллекторы транзисторов 9 первой группы соединены с числовыми шинами 1 , с первыми адресными шинами 10, а эмиттеры подключены к коллекторам транзисторов 11 второй группы и через резисторы 12 к шине 13, базы транзисторов соединены со вторыми адресными шинами 14.. а эмиттеры - с общей шиной 15.

Матричный накопитель работает следующим образом.

В режиме записи на шину 15 подают нулевой потенциал, а на шину 13 положительный потенциал, например 2-5 В, на одну из шин 10 и 14 подают токи выборки. В результате открываются: транзисторы 9 и 11, соединенные с выбранными шинами, и подключают одну из числовых шин 1 к общей шине 15.

Остальные шины 1 остаются отключенньали от общей шины 15, так как в цепочке транзисторов 9, 11 этих шин хотя бы один оказывается закрытым.

На одну из шин 8 подают потенциал записи, а на остальные - нулевой потенциал. При этом транзисторы 5, подключенные к выбранной числовой шине 1 переходят в режим насыщения, а остальные находятся в режиме отсечки, в соответствии с записываемой информацией на выходные шины б подается ток записи или нулевой потенциал, в первом случае ток записи через выбранный транзистор, находящийся в режиме насыщения, попадает на соответствующую разрядную шину, а оттуда через диод и запоминающий элемент - на выбранную числовую шину, производя запись. Во втором случае ток, протекающий через выбранный резистор 7 стекает череэ коллекторный переход транзистора на выходную шину и запись не происходит.

В режиме считывания, так же как и при записи выбранная числовая шина 1 подключается, а остальные отключаются от общей шины 15. На выбранную входную шину 8 подается потенциал высокого уровня, а на остгшьные нулевой потенциал. При этом, в зависимости от состояния проводимости эа поминающих элементов, находящихся на пересечении выбранных, числовой и разрядных шин, ток выбранных резне торов 7 через эмиттерные переходы транзисторов 5, разрядные шины и проводящие - 3 апоминающие элементы;

стекает на выбранную числовую шину, либо, если запоминающие элементы не проводят, через коллекторные переходы поступает на выходные шины накопителя. В первом случае на выходных,шинах устанавливается по тенциал низкого уровня, а во втором высокого.

По сравнению с известным предлагаемый накопитель дает значительный . выигрьпы в количестве внешних

ВЫВОДОВ; Минимально возможное

число внешних выводов , известного накопителя равЮ т,, J-W где N - объем информации. В предлагаемом накопителе минимально возмо 5 ное число внешних выводов nij. . Например для объема 4096 бит m 48, а т 26, причем в первом случае диодная матрица оказывается слишком несимметричной (16 числовых и 256 разрядных шин), что приводит к потерям в плотности информации и быстродействии, в то время как в предлагаемом . накопителе количество числовых и разрядных шин равно 64. Если же в извест

г ном накопителе число разрядных И;

числовых шин уравнять, -то накопитель будет иметь уже 80 внешних выводов, что приводит к необходимости подключения дополнительного оборудования и усложнению накопителя.

Формула изобретения

Матричный накопитель, содержащий 5 последовательно соединенные запоминающие элементы и диоды, которые подключены между числовыми и разряд21ыми шинами,транзисторы,коллекторы которых подключены к выходным шинам, эмиттеры - к разрядным шинам, а базы - через резисторы к вxoдны шинам, отличающийся тем, что, с целью упрощения устройства, в него введены группы тран- зисторов и первые и вторые адресные шины, причем коллекторы транзисторов первой группы подключены к числовым шинам, базы - к первым адресным шинам, а эмиттеры подключены к коллекторам транзисторов второй группы, которые через резисторы подключены к шине питания, базы транзисторов второй группы подключены ко вторым адресн ым шинам, а эмиттеры - к общей шине накопителя. 5

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 506060, кл. G II С 11/34, 1973,

2. Авторское свидетельство СССР по заявке 2697090, кл. G 11 С 11/34 45 18,12.78 (прототип).

/r

-0S

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель | 1979 |

|

SU799007A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU637870A1 |

| Запоминающее устройство | 1974 |

|

SU658600A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Матричный накопитель | 1978 |

|

SU752483A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

8

d я

Авторы

Даты

1980-10-23—Публикация

1979-04-27—Подача