Устройство работает следующим образом.

Первый цикл деления выполняется по обычному алгоритму, остальные циклы выполняются в следующем порядке.

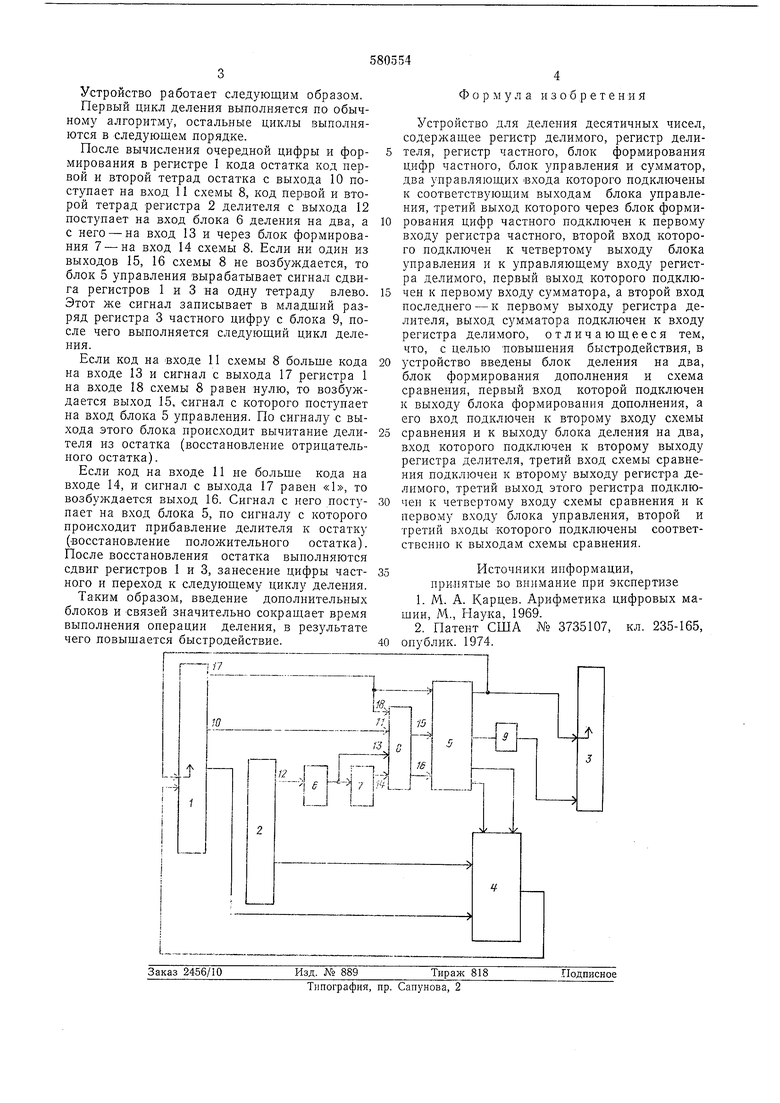

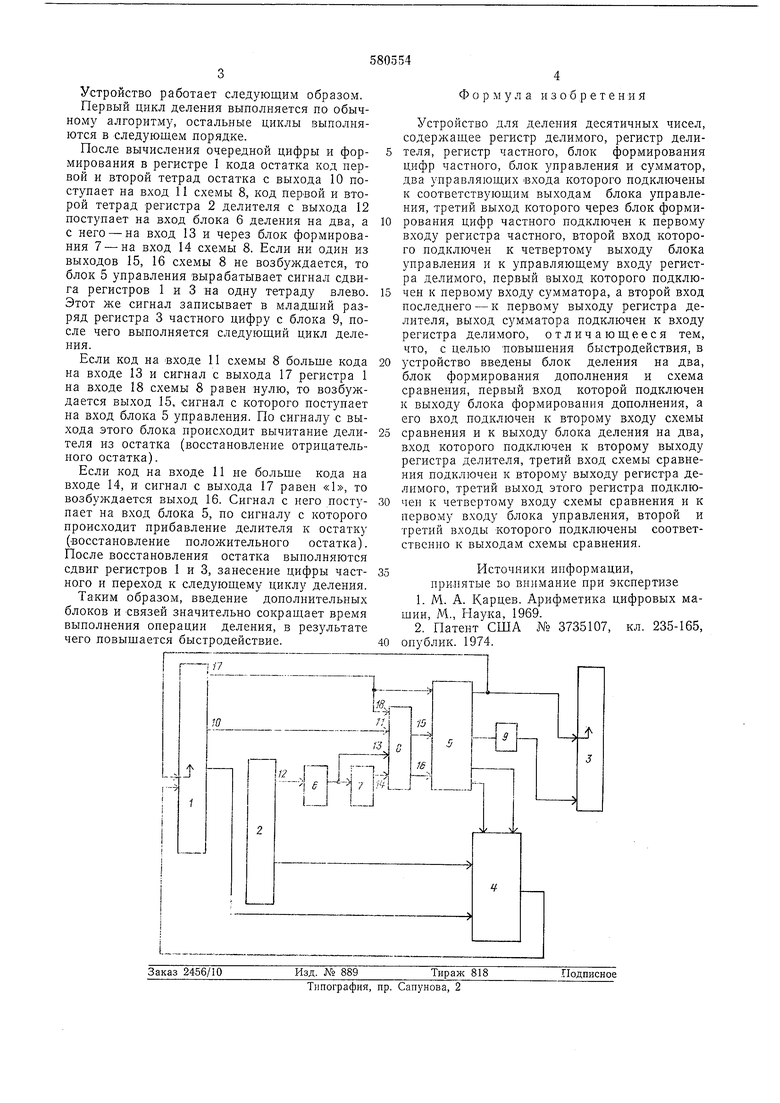

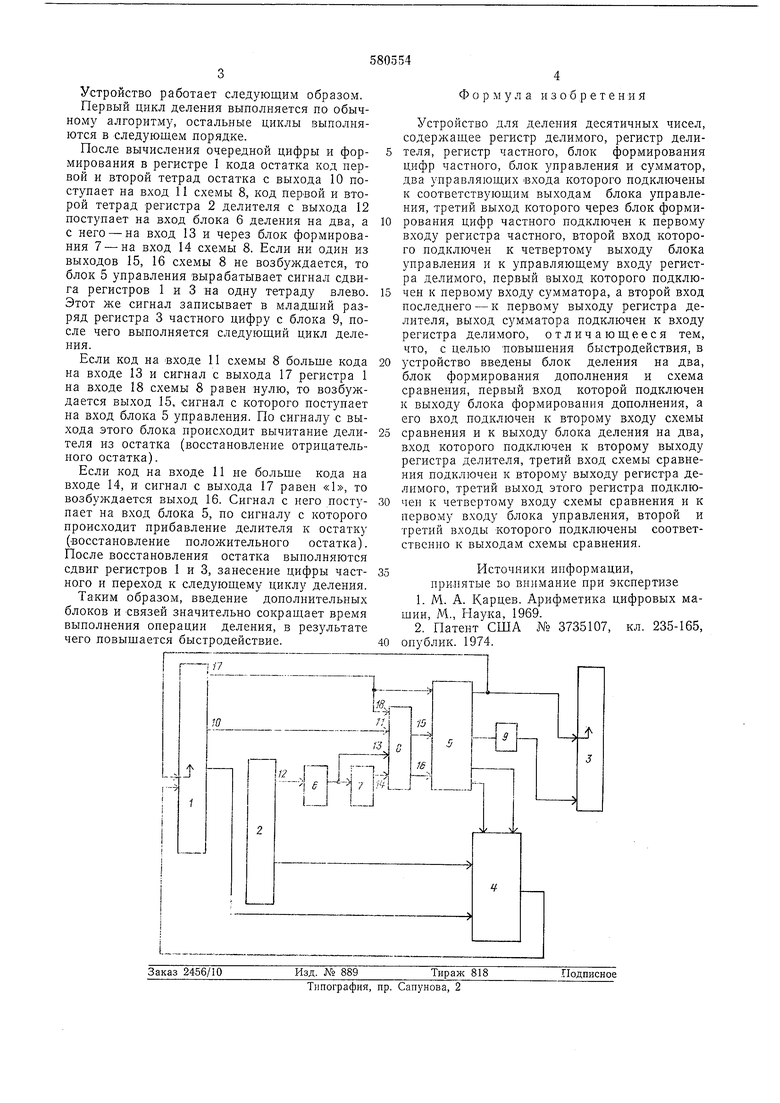

После вычисления очередной цифры и формирования в регистре 1 кода остатка код первой и второй тетрад остатка с выхода 10 поступает на вход 11 схемы 8, код первой и второй тетрад регистра 2 делителя с выхода 12 поступает на вход блока 6 деления на два, а с него - на вход 13 и через блок формирования 7 - на вход 14 схемы 8. Если ни один из выходов 15, 16 схемы 8 не возбуждается, то блок 5 управления вырабатывает сигнал сдвига регистров 1 и 3 на одну тетраду влево. Этот же сигнал записывает в младший разряд регистра 3 частного цифру с блока 9, после чего выполняется следующий цикл деления.

Если код на входе 11 схемы 8 больше кода на входе 13 и сигнал с выхода 17 регистра 1 на входе 18 схемы 8 равен нулю, то возбуждается выход 15, сигнал с которого постзпает на вход блока 5 управления. По сигналу с выхода этого блока происходит вычитание делителя из остатка (восстановление отрицательного остатка).

Если код на входе 11 не больше кода на входе 14, и сигнал с выхода 17 равен «1, то возбуждается выход 16. Сигнал с него поступает на вход блока 5, по сигналу с которого происходит прибавление делителя к остатку (восстановление положительного остатка). После восстановления остатка выполняются сдвиг регистров 1 и 3, занесение цифры часткого и переход к следующему циклу деления.

Таким образом, введение дополнительных блоков и связей значительно сокращает время выполнения операции деления, в результате чего повышается быстродействие.

Формула изобретения

Устройство для деления десятичных чисел, содержащее регистр делимого, регистр делителя, регистр частного, блок формирования цифр частного, блок управления и сумматор, два управляющих входа которого подключены к соответствующим выходам блока управления, третий выход которого через блок формирования цифр частного подключен к первому входу регистра частного, второй вход которого подключен к четвертому выходу блока управления и к управляющему входу регистра делимого, первый выход которого подключен к первому входу сумматора, а второй вход последнего - к первому выходу регистра делителя, выход сумматора подключен к входу регистра делимого, отличающееся тем, что, с целью -повышения быстродействия, в Зстройство введены блок деления на два, блок формирования дополнения и схема сравнения, первый вход которой подключен к выходу блока формирования дополнения, а его вход подключен к второму входу схемы сравнения и к выходу блока деления на два, вход которого подключен к второму выходу регистра делителя, третий вход схемы сравнения подключен к второму выходу регистра делимого, третий выход этого регистра подключен к четвертому входу схемы сравнения и к первому входу блока управления, второй и третий входы которого нодключены соответственно к выходам схемы сравнения.

Источники информации, принятые во внимание при экспертизе

1.М. А. Карцев. Арифметика цифровых машин, М., Наука, 1969.

2.Патент США № 3735107, кл. 235-165, опублик. 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления десятичных чисел | 1978 |

|

SU656087A2 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для вычисления квадратного корня | 1973 |

|

SU560224A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1151957A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

Авторы

Даты

1977-11-15—Публикация

1976-03-17—Подача