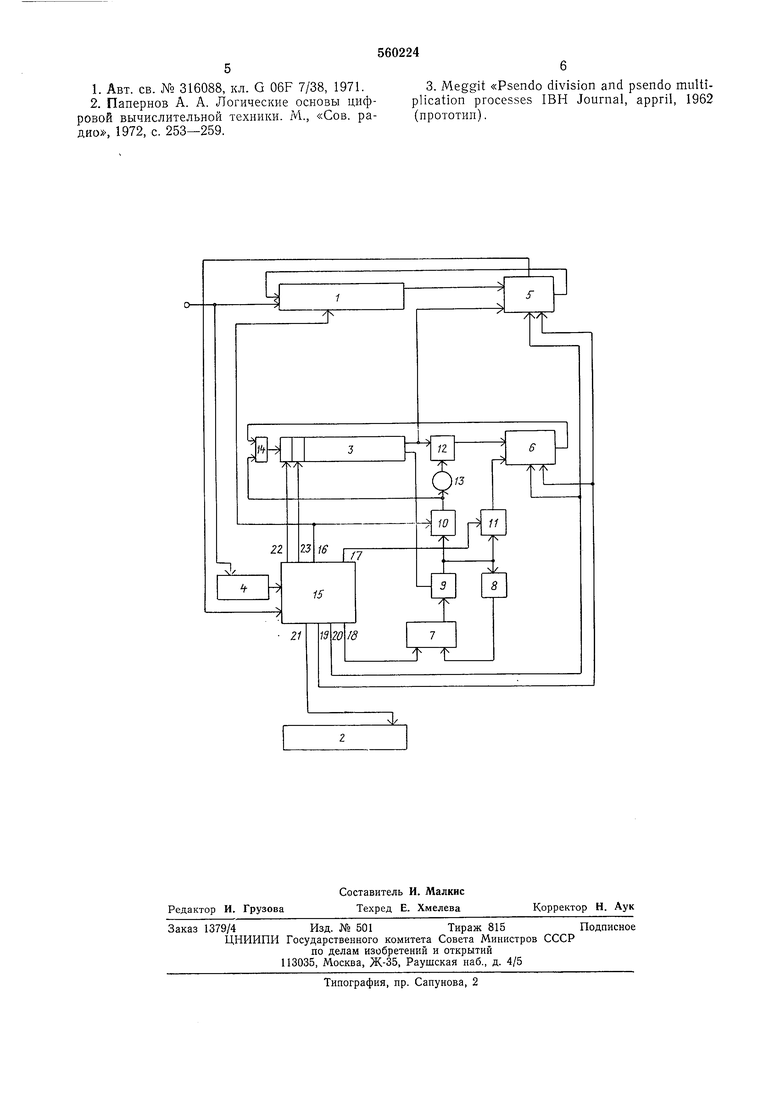

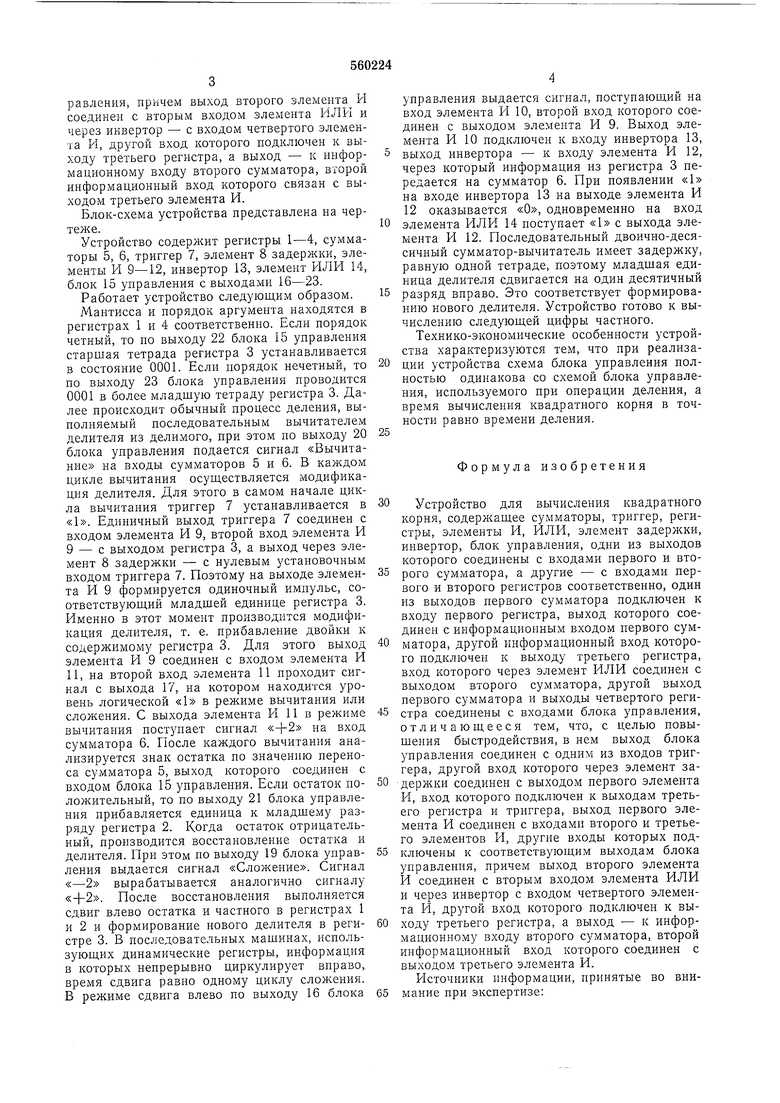

рявления, причем выход второго элемента И соединен с вторым входом элемента ИЛИ и через инвертор - с входом четвертого элемента И, другой вход которого подключен к выходу третьего регистра, а выход - к информационному входу второго сумматора, второй информационный вход которого связан с выходом третьего элемента И. Блок-схема устройства представлена на чертеже. Устройство содержит регистры 1-4, сумматоры 5, 6, триггер 7, элемент 8 задержки, элементы И 9-12, инвертор 13, элемент ИЛИ 14, блок 15 управления с выходами 16-23. Работает устройство следующим образом. Мантисса и порядок аргумента находятся в регистрах 1 и 4 соответственно. Если порядок четный, то но выходу 22 блока 15 управления старшая тетрада регистра 3 устанавливается в состояние 0001. Если порядок нечетный, то по выходу 23 блока управления проводится 0001 в более младшую тетраду регистра 3. Далее происходит обычный процесс деления, выполняемый последовательным вычитателем делителя из делимого, при этом по выходу 20 блока управления подается сигнал «Вычитание на входы сумматоров 5 и 6. В каждом цикле вычитания осуществляется модификация делителя. Для этого в самом начале цикла вычитания триггер 7 устанавливается в «1. Единичный выход триггера 7 соединен с входом элемента И 9, второй вход элемента И 9 - с выходом регистра 3, а выход через элемент 8 задержки - с нулевым установочным входом триггера 7. Поэтому на выходе элемента И 9 формируется одиночный импульс, соответствующий младшей единице регистра 3. Именно в этот момент производится модификация делителя, т. е. прибавление двойки к содержимому регистра 3. Для этого выход элемента И 9 соединен с входом элемента И И, на второй вход элемента И проходит сигнал с выхода Г/, на котором находится уровень логической «1 в режиме вычитания или сложения. С выхода элемента И 11 в режиме вычитания поступает сигнал «+2 на вход сумматора 6. Иосле каждого вычитания анализируется знак остатка по значению переноса сумматора 5, выход которого соединен с входом блока 15 управления. Если остаток положительный, то по выходу 21 блока управления прибавляется единица к младшему разряду регистра 2. Когда остаток отрицательный, производится восстановление остатка и делителя. При этом по выходу 19 блока управления выдается сигнал «Сложение. Сигнал «-2 вырабатывается аналогично сигналу «-)-2. После восстановления выполняется сдвиг влево остатка и частного в регистрах 1 и 2 и формирование нового делителя в регистре 3. В последовательных машинах, использующих динамические регистры, информация в которых непрерывно циркулирует вправо, время сдвига равно одному циклу сложения. В режиме сдвига влево по выходу 16 блока управления выдается сигнал, поступающий на вход элемента И 10, второй вход которого соединен с выходом элемента И 9. Выход элемента И 10 подключен к входу инвертора 13, выход инвертора - к входу элемента И 12, через который информация из регистра 3 передается на сумматор 6. При появлении «1 на входе инвертора 13 на выходе элемента И 12 оказывается «О, одновременно на вход элемента ИЛИ 14 поступает «1 с выхода элемента И 12. Последовательный двоично-десясичный сумматор-вычитатель имеет задержку, равную одной тетраде, поэтому младшая единица делителя сдвигается на один десятичный разряд вправо. Это соответствует формированию нового делителя. Устройство готово к вычислению следующей цифры частного. Технико-экономические особенности устройства характеризуются тем, что при реализации устройства схема блока управления полностью одинакова со схемой блока управления, используемого при операции деления, а время вычисления квадратного корня в точности равно времени деления. Формула изобретения Устройство для вычисления квадратного корня, содержащее сумматоры, триггер, регистры, элементы И, ИЛИ, элемент задержки, инвертор, блок управления, одни из выходов которого соединены с входами первого и второго сумматора, а другие - с входами первого и второго регистров соответственно, один из выходов первого сумматора подключен к входу первого регистра, выход которого соединен с информационным входом первого сумматора, другой информационный вход которого подключен к выходу третьего регистра, вход которого через элемент ИЛИ соединен с выходом второго сумматора, другой выход первого сумматора и выходы четвертого регистра соединены с входами блока управления, отличающееся тем, что, с целью повышения быстродействия, в нем выход блока управления соединен с одним из входов триггера, другой вход которого через элемент задержки соединен с выходом первого элемента И, вход которого подключен к выходам третьего регистра и триггера, выход первого элемента И соединен с входами второго и третьего элементов И, другие входы которых подлючены к соответствующим выходам блока правлепия, причем выход второго элемента соединен с вторым входом элемента ИЛИ через инвертор с входом четвертого элемена И, другой вход которого подключен к выоду третьего регистра, а выход - к инфорационному входу второго сумматора, второй нформационный вход которого соединен с ыходом третьего элемента И. РГсточники информации, принятые во вниание при экспертизе:

1.Авт. св. № 316088, кл. G 06F 7/38, 1971.

2.Папернов А. А. Логические основы цифровой вычислительной техники. М., «Сов. радио, 1972, с. 253-259.

3. Meggit «Psendo division and psendo multiplication processes IBH Journal, appril, 1962 (нрототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1151957A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

Авторы

Даты

1977-05-30—Публикация

1973-04-04—Подача