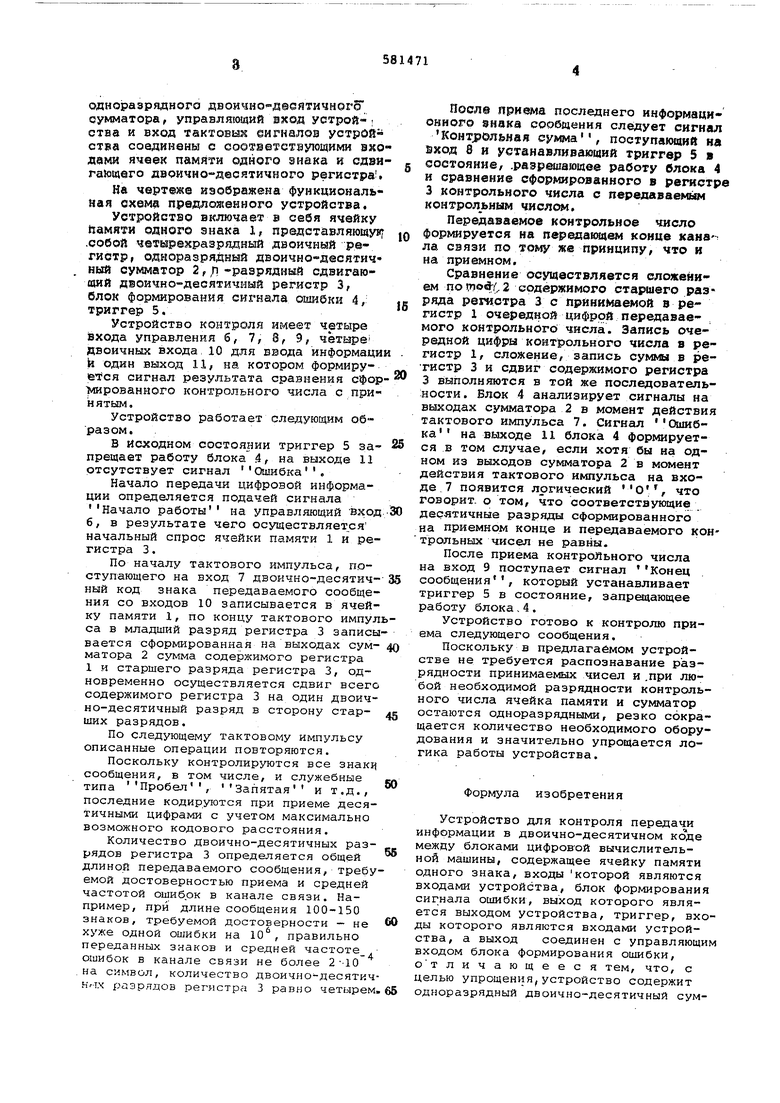

ояно)разрядного двоично-д сятичного сумматора, управляющий вход устрой-; ства и вход тактовык еигналоэ устрОйст а соединены с еоответетэугощими вхо дами ячеек памяти одного знака и сдви ratowero двоично-десятичного регистра . На чертеже изображена функциональная схема предложенного устройства. Устройство включает э себя ячейку памяти одного знака 1, представляющук .собой четырехразрядный двоичный регистр, одноразрядный двоично-десятичный сумматор 2,я -разрядный сдвигающий двоично-десятичный регистр 3, елок формирования сигнала ошибки 4, триггер 5. Устройство контроля имеет четыре 1зхода управления б, 7, 8, 9, четыре двоичных входа,10 для ввода информаци и один выход И, на котором формируег1 ся сигнал результата сравнения сфор мированного контрольного числа с принятым. Устройство работает следующим образом. В Исходном состоянии триггер 5 запрещает работу блока 4, на выходе 11 Ошибка отсутствует сигнал Начало передачи цифровой информации определяется подачей сигнала Начало работы на управляющий Вход 6, в результате чего осуществляет ся начальный спрос ячейки памяти 1 и регистра 3. По началу тактового импульса, поступающего на вход 7 двоично-десятичный код знака передаваемого сообщения со входов 10 записывается в ячейку памяти 1, по концу тактового импул са в младший разряд регистра 3 записы вается сформированная на выходах сумматора 2 сумма содержимого регистра 1 и старшего разряда регистра 3, одновременно осуществляется сдвиг всего содержимого регистра 3 на один двоично-десятичный разряд в сторону старших разрядов. По следующему тактовому импульсу описанные операции повторяются. Поскольку контролируются все знак сообщения, в том числе, и служебные типа Пробел, Запятая и т.д., последние кодируются при приеме десятичными цифрами с учетом максимально возможного кодового расстояния. Количество двоично-десятичных разрядов регистра 3 определяется общей длиной передаваемого сообщения, требу емой достоверностью приема и средней частотой ошибрк в канале связи. Например, при длине сообщения 100-150 знаков, требуемой достоверности - не хуже одной ошибки на 10, правильно переданных знаков и средней частоте . ошибок в канале связи не более 2--10 ,на символ, количество двоично-десятич К-т.х разрядов регистра 3 равно четырем После приема последнего информационного знака сообщения следует сигнал Контрольная сумма , поступающий на Ёход 8 и устанавливающий триггер 5 в состояние, .разрешающее работу блока 4 и сравнение сформированного в регистре 3 контрольного числа с передаваемым KOHTponjbHEiM числом, Пгредаваемое контрольное число формируется на первдакедем конце хаиа ла связи по тому же принципу, что и на приемном. Сравнение осуществляется сложейием по содержимого старшего разряда регистра 3 с принимаемой а регистр 1 очередной цифрой передаваемого контрольного числа. Запись очередной цифры контрольного числа в регистр 1, сложение, запись суммы в ретистр 3 и сдвиг содержимого регистра 3 Выполняются в той же последовательности. Блок 4 анализирует сигналы на выходах сумматора 2 в момент действия тактового импульса 7. Сигнал Ошкбка на выходе 11 блока 4 формируется в том случае, если хотя бы на одном из выходов cyNMaTopa 2 в момент действия тактового импульса на входе 7 появится логический О, что говорит, о том, что соответствующие десятичные разряды сформированного на приемном конце и передаваемого контрольных чисел не равны. После приема контрольного числа на вход 9 поступает сигнал Конец сообщения , который устанавливает триггер 5 в состояние, запрацающее работу блока,4. Устройство готово к контролю приема следующего сообщения. Поскольку в предлагаемом устройстве не требуется распознавание разрядности принимаемых чисел и .при любой необходимой разрядности контрольного числа ячейка памяти и сумматор остаются одноразрядными, резко сокращается количество необходимого оборудования и значительно упрощается логика работы устройства. Формула изобретения Устройство для контроля передачи информации в двоично-десятичном коДе между блоками цифровой вычислительной машины, содержащее ячейку памяти одного знака, входы которой являются входами устройства, блок формирования сигнала ошибки, выход которого является выходом устройства, триггер, входы которого являются входами устройства, а выход соединен с управляющим входом блока формирования ошибки, отличающеес я тем, что, с целью упрощения,устройство содержит одноразрядный двоично-десятичный сумматор, сдаигаклций двоично-десятичный регистр/ причем выходы ячейки па мяти одного знака соединены с пер вой группой входов одноразрядного двоично-десятичного сумматора, выходы которого соединены со входами блока формирования сигнала ошибки и со входами младшего разряда сдвигающего двоично-Аесятичногр регистра, выходы старшего разряда сдвигакядего двоич- но-явсятичного регистра соединены со второй группой входов одноразрядного

J/ ф Ф

двсятично-двоично,го сумматора, управляюиий вход устройства и вход тактовых сигналов устройства соединены с соответств тощими входами ячейки памяти одного знака и сдвигающего двоично-десятичного регистра.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР 469130, &08 С 25/00, 1972.

2.Авторское свидетельство СССР 269600, е 06 Т 7/02, 1968,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля передачи информации | 1981 |

|

SU1029207A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| Устройство для преобразования двоичного кода в код магнитного носителя | 1980 |

|

SU1148572A3 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Способ передачи и приема дискретных сообщений в комплексе декаметровой радиосвязи | 2020 |

|

RU2743233C1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

Г

,5 /

п

I

I

I

I

I I

-и

LJ

t4 ITJ

Авторы

Даты

1977-11-25—Публикация

1975-12-18—Подача