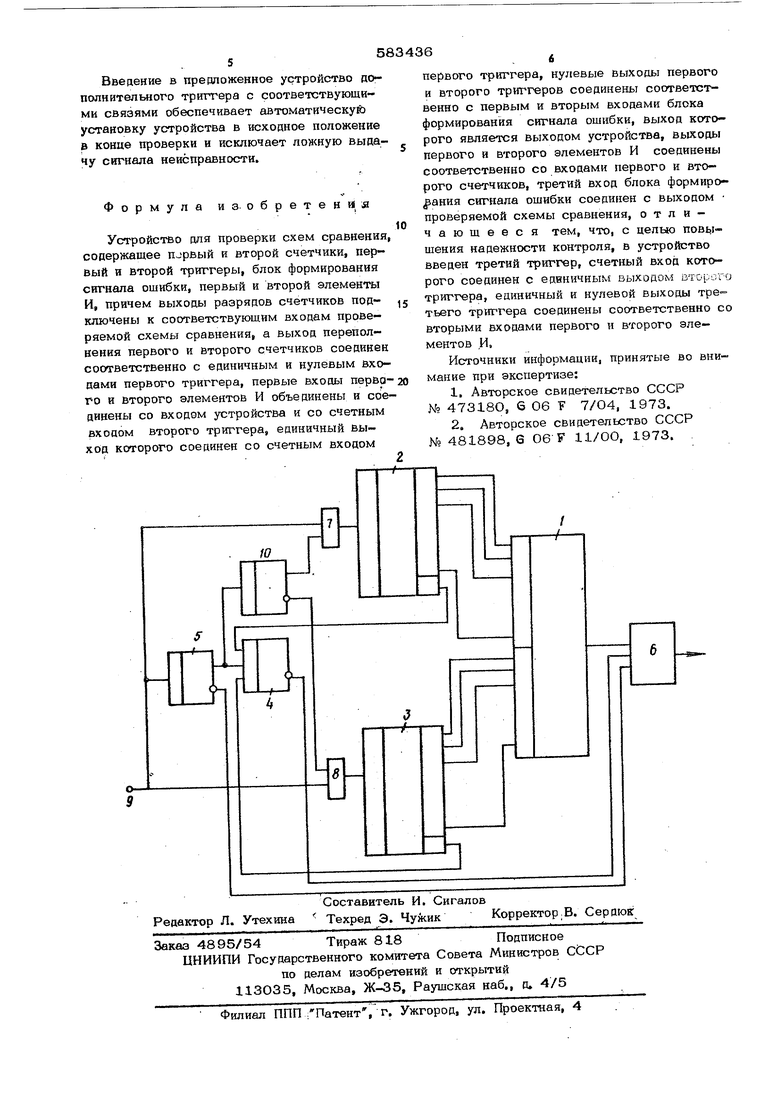

(54) УСТРОЙСТВО ДЛЯ ПРОВЕРКИ СХЕД СРАВНЕНИЯ

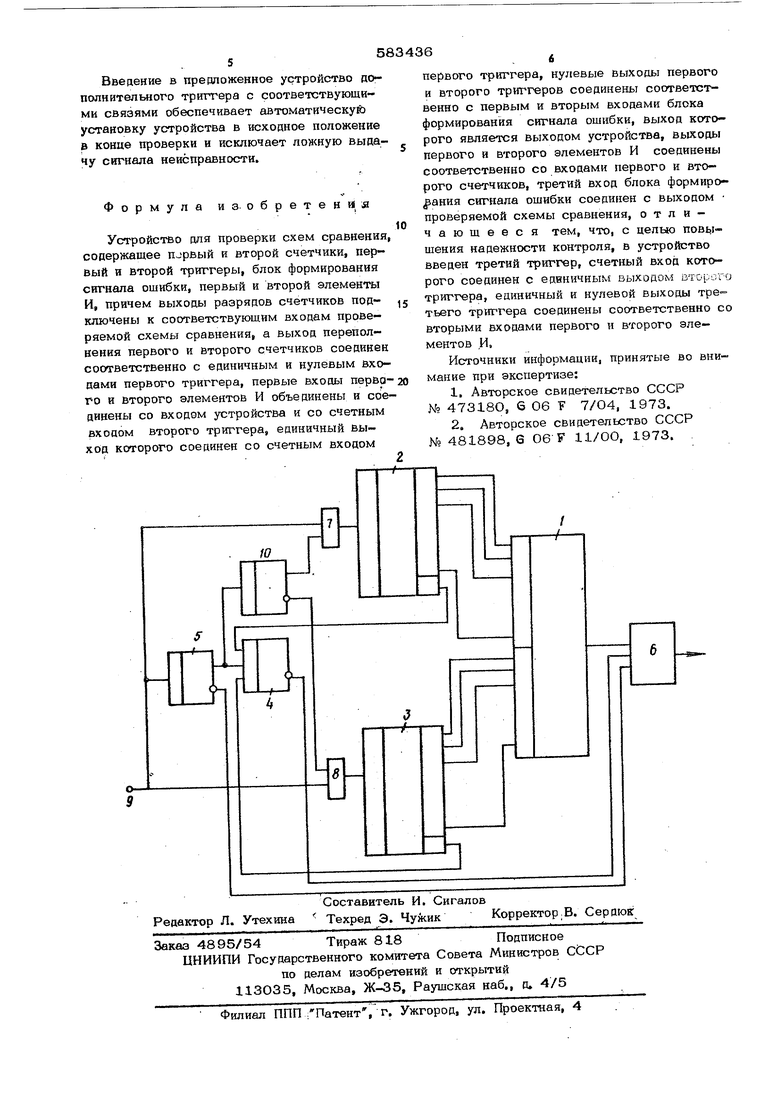

разрядов двоичных счетчиков 2 н З.Нулв-т, вые выходы триггеров 4 и 5 подключены к первому и второму входам блока 6 формиртваниа сигнала ошибки, третий вход которого подключен к выходу схемы сравнения 1, Вы5соды элементов и 7- и 8 подключены ко входам счетчиков 2 и 3 соответственно, их первые входы объединены и подключены КО- входу 9 устройства и к счетному входу триггера 5, а вторые входы - соответстве но к единичному и нулевому выходам тригге ра 10, счетный вход которого подключен г единичному выходу триггера 5, Единичный и нулевой входы триггера 4 подключены к выходам переполнения счетчиков 2 и 3 с оответственно.

Устройство работает следующим образом..

Перед началом работы оба счетчика и все триггеры устанавливаются в нулевое положение.

При этом на выходе элемента И 8 положительный потенциал, на выходе элемента

И 7 - отрицательный потенциал. При поступлении тактовых импульсов на вход ycTpOiiства происходит последовательное переключение триггеров 5,4,10 из состояния ООО

в состояние 111% ОН, 100, ООО и т.д. {триггеры 4 и 10 переключаются синхронно вплоть до заполнения счетчиков). Триггер 10 коммутирует входы счетчиков 2 и 3, благодаря чему соотношение

между числами А и В в счетчиках 2 и 3 соответственно на каждом такте меняется такой последовательности: А В, А В, А В, А В, А В, и т. д.

В соответствии с этими соотношениями

схема сравнения 1 выдает в блок в формирования сигнала ошибки сигналы В), Xj () ил, ).

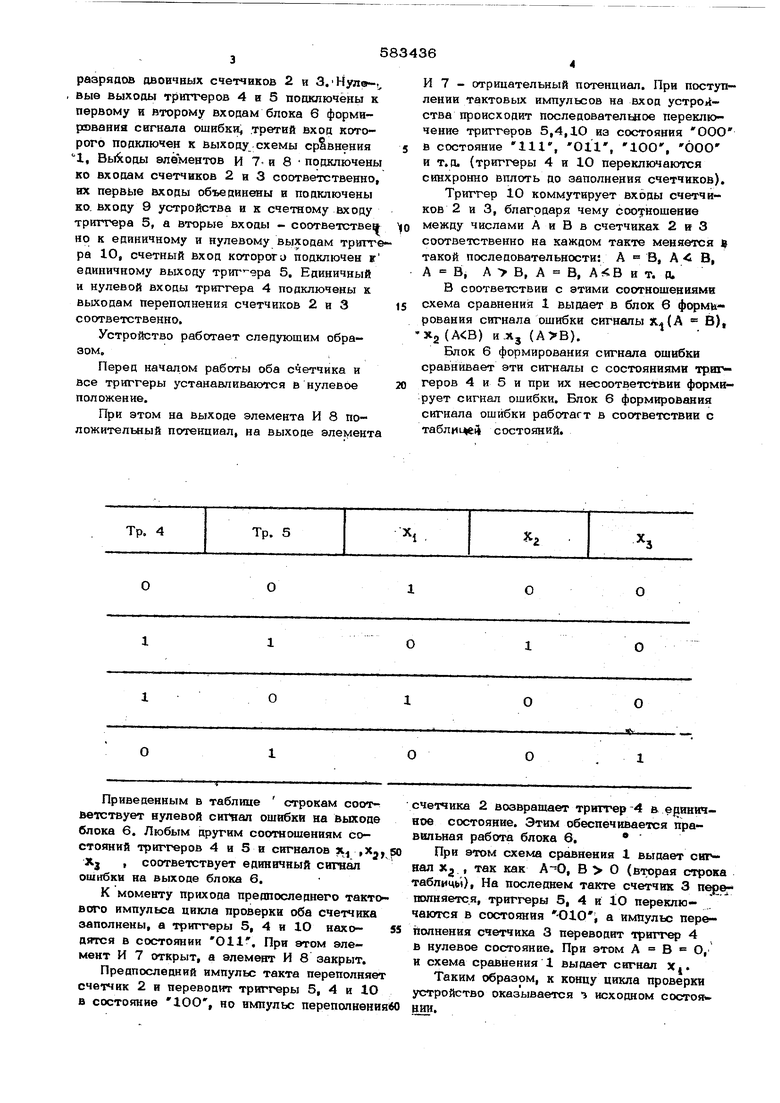

Блок 6 формирования сигнала ошибки сравнивает эти сигналы с состояниями триггеров 4 и 5 и при их несоответствии формирует сигнал ошибки. Блок 6 формирования сигнала ошибки работает в соответствии с таблицей состояний.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки схем сравнения двоичных чисел | 1973 |

|

SU481898A1 |

| Устройство для контроля схем сравнения | 1976 |

|

SU584309A1 |

| Устройство для изготовления и контроля полнокодовой перфоленты | 1983 |

|

SU1118555A1 |

| Устройство для контроля схем сравнения | 1979 |

|

SU960822A1 |

| Устройство для контроля схем сравнения | 1978 |

|

SU767767A1 |

| Устройство распределения задач в мультипроцессорной системе | 1986 |

|

SU1363235A2 |

| Устройство для обнаружения и исправления ошибок | 1989 |

|

SU1640814A1 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

О

О

о

о

Приведенным в таблице строкам соответствует нулевой сигнал ошибки на выходе блока 6. Любым другим соотношениям состояний триггеров 4 и 5 и сигналов х ,4 so Xj , соответствует единичный сигнал ошибки на выходе блока 6.

К моменту прихода предпоследнего тактового импульса цикла проверки оба счетчика заполнены, а триггеры 5, 4 и 1О нахо- 55 дятся в состоянии 011, При этом элемент И 7 открыт, а элемент И 8 закрыт.

Предпоследний импульс такта переполняет счетчик 2 и переводит триггеры 5, 4 и Ю в состояние 100, но импульс переполнениявО

О

о

о

о

о

о

счетчика 2 возвращает триггер-4 в единичное состояние. Этим обеспечивается правильная работа блока 6,

При этом схема сравнения 1 выдает сигнал Хд , так как A-Q, В О (вторая строка табличь). На последнем такте счетчик 3 переполняется, триггеры 5, 4 и 1О переключаются в состояния -СЮ, а импульс переполнения счетчика 3 переводит триггер 4 в нулевое состояние. При этом А В О, и схема сравнения 1 выдает сигнал х..

Таким образом, к концу цикла проверки устройство оказывается i исходном состоя. ВИН.

Авторы

Даты

1977-12-05—Публикация

1976-05-11—Подача