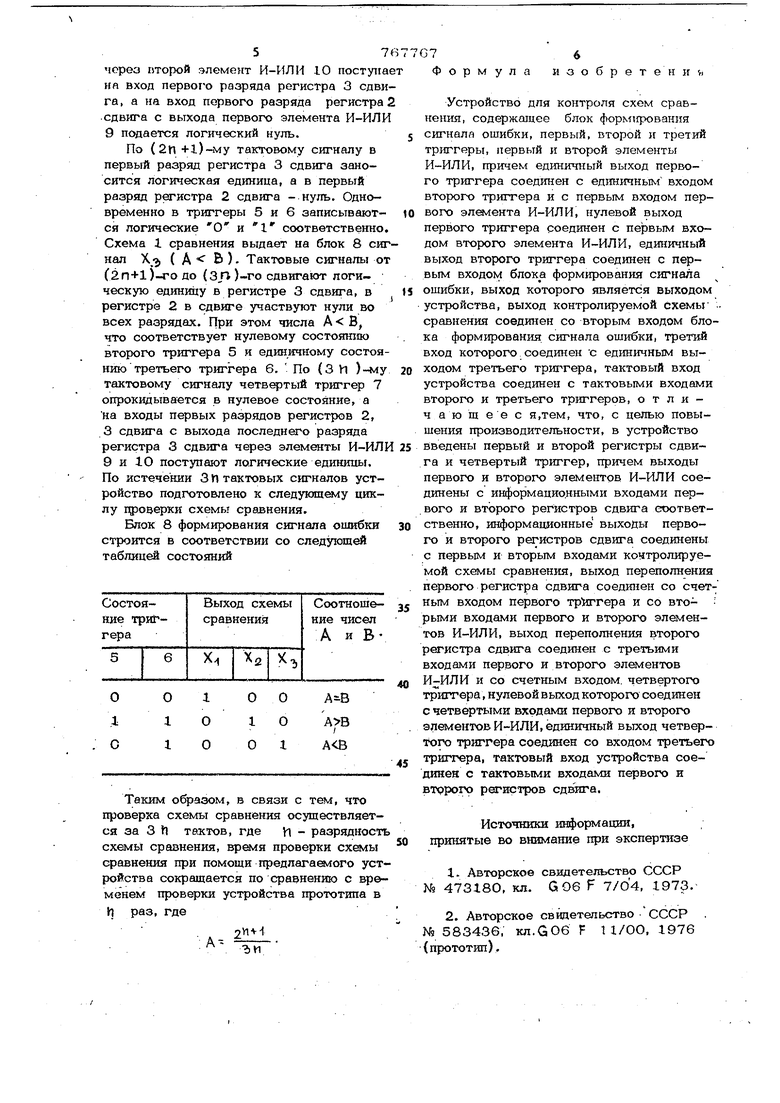

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СХЕМ Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств проверки электронных блоков дискретной автоматики и вычислительных машин. Известно устройство для проверки схем сравнения, содержащее два двоичных счет чика, выходы разрядов которых подклю чены ко входам проверяемой схемы сравнения, триггер, элемент неравнозначности и индикатор . В этом устройстве входы переполнения двоичных счетчиков соединены со входами триггера, один из выходов которого и выход проверяемой схемы сравнения связаны со входами элемента неравнозначности, выход которого подключен ко входу индикатора, причем входы обоих двоичных счетчиков соединены с шиной тактовых сигналов, а вход одного из них - с входной шиной предварительной установки. Недостаток такого устройства в том, что схема сравнения не проверяется на СРАВНЕНИЯ разность двух чисел, участвующих в сравнении, причем для этой неполной проверки требуется 2 тактовых сигналов, где VI - разрядность схемы сравнения. Наиболее близким техническим решением к изобретению является устройство для проверки схем сравнения, содержащее триггеры, блок формирования сигнала .ошибки, два счетчика, входы которых через соответствующие элементы И соединены с тактовым входом устройства, а выходы подключены ко входам проверяемой схемы сравнения 2. . К недостатку известного устройства относится большое время проверки схемы сравнения, которое равняется , где Ц - разрядность схемы сравнения. Цель изобретения i- повышение производительности работы устройства. Поставленная цель достигается тем, что в устройство для контроля схем сравнения, содержащее блок формирования сигнала ошибки, первый, второй и третий триггеры, первый и второй элементы - -И-ИЛИ, причем едшпгчный выход первого триггера соединен с едини пи. входом втоуюго триггера и с первым входом первого элеьшнта И- ИЛИ, нулевой выход первого триггера связан с первым входом второго элемента И-ИЛИ, едпншшый выход второго триггера - с первым входом блока -форм фования сигнала ошибки, выход которого является выходом устройства, выход контролируемой схемы сравнения - со вторым входом блока форм1-фо вания сигнала ошибки, третий вход которо го подключен к единичному выходу третье го триггера, а тактовый вход устройства соединен с тaктoвьnv и входами второго и Третьего триггеров, введены первый и второй регистры сдвига и четвертый триг гер. При этом выходы первого и второго элементов И-ИПИ соединены с информационными входами первого и второго регистров сдвига соответственно, информаUHiDfHHbie выходы первого и второго регис ров сдвига - с первым н вторым входами 1 онтрол1фуемой схемы сравнения, а выход переполнения первого регистра сдвига со счетным входом первого триггера и со вторыми входами первого и второго элементов И-ИЛИi Выход переполнениявто poix) регистра сдвига соединен с третьими входами первого-и второго элементов И-ИЛИ и со счетным входом четвертого Tpiflnrepa, нулевой выход которого связан с четвертыми входами первого н второго элементов И-ИДИ, а едишиный выход -четвертого триггера - со входом третьего триггера, тактовый вход устройства подключен к тактовым входам первого к второгчэ регистров сдвига. Схема устройства представлена на чертеже. Она содержит контролируемую схему сравнения, первый 2 и второй 3 регистры сдвига, первый 4, второй 5, третий 6 и четвертый 7 триггеры, блок 8 формирования сигнала ошибки, первый 9 и второй 10 элементы И-ИЛИ, вход 11 - тактовьгй вход устройства. Устройство работает следующим образом. Перед началом проверки схемы сравнения триггеры 4 - 7 сбрасываются в нулевое состояние, в первые разряды регистров 2, 3 сдвига записываются логические единицы, а остальные разряды обнуляются (цепи начальной установки устройства не показаны). Схема 1 сравнения выдает на блок 8сигнал X., ( А Ъ ) где А и В - числа в регистрах 2 и 3 соответственно. По каждому тактовому ciirHfiny, поступающему по входу 1-1, в регистрах 2, .3 производится сдвиг информации на один разряд вправо. За Ц тактов , где Vi - разрядность схемы сравнения, логические единицы проходят поочередно все разряды регистров сдвига. При этом числа в регистрах сдвига равны, что соответствует нулевым состояниям триггеров 5,6. Блок 8 выдает на выход 12 сигнал ИСПРАВНО при .наличии сигнала или сигнал НЕИСПРВНО при отсутствии сигнала Х . При сдвиге логических ед1тиц в последние разряды регистров сдвига ( ц -и тактовый сигнал) триггеры 4,7 по счетным входам устанавливаются в, единичные состояния. На вход первого разряда первого регистра 2 сдвига через первый элемент И-ИЛИ 9 поступает логическая единица, а на вход первого разряда второго регистра 3 сдвига с выхода второго элемента И-ИЛИ 1О - логический нуль. Работа . элементов И-ИЛИ 9, 10 описывается следуюшикти уравнениями: 0--3hQ-(4Q; де c(ott)o - выходы первого и второго . элементов. И-ИЛИ соответственно;hi выходы последних разрядов первого и второго регистров сдвига соответственно;jl прямые выходы первого к второго триггеров соответ ственно;Q, Q 2 - инверсные выходы п эвого и второго триггеров соответственно. . По ( i- 1)му тактовому сигналу третий 6 и.четвертый 7 триггеры и в ервый разряд первого регистра 2 сдвиа записывается логическая единица, а в ервый разряд второго регистра 3 сдвиа - логический нуль. Схема 1 сравнеия выдает на блок В сигнал ), актовые сигналы от ( V +l)-ro до 2 И ) -го сдвигают логическую единицу регистре 2 сдвига, в регистре 3 в сдвиге частвуют нули во всех разрядах. При том числа,, что соответствует едиичньпл состряниям триггеров. По 2 И ) -му тактовому сигналу первый риггер 4 опрокидывается по счетному ходу и логическая единица с выхода оследнего разряда регистра сдвига 2. 57 через нторой элемент И-ИЛИ 10 поступа н« вход первого разряда регистра 3 сдви га , а на вход первого разряда регистра сдвига с выхода первого элемента И-ИЛИ 9 подается логический нуль. По (2п +1)му тактовому сигналу в первый разряд регистра 3 сдвига заносится логическая единица, а в первый разряд регистра 2 сдвига - нуль. Одновременно в триггеры 5 и 6 записываются логические О и 1 соответственно Схема 1 сравнения выдает на блок 8 си нал X -j ( А В ). Тактовые сигналы о (2п+1)-го до (3/v)-ro сдвигают логическую единицу в регистре 3 сдвига, в регистре 2 в сдвиге участвуют нули во всех разрядах. При этом числа А В, что соответствует нулевому состоянию второго триггера 5 и единичному состоя нию третьего триггера 6. По (3 Я )-му тактовому сигналу четвертый триггер 7 опрокидывается в нулевое состояние, а на входы первых разрядов регистров 2, 3 сдвига с выхода последнего разряда регистра 3 сдвига через элементы И-ИЛ 9 и 10 поступают логические единицы. По истечении 3 И тактовых сигналов устройство подготовлено к следующему циклу гфоверки схемы сравнения. Блок 8 формирования сигнала ошибки строится в соответствии со следующей таблицей состожгний Таким образом, в связи с тем, что проверка схемы сравнения осуществляется за 3 h тактов, где VI - разрядност схемы сравнения, время проверки схетлы сравнения при помощи предлагаемого уст ройства сокращается по сравненгао с временем проверки устройства прототипа в II раз, где Формула изобретен и VJ Устройство для контроля схем сравнения, содержащее блок формирования сигнала ошибки, первый, второй и третий триггеры, первый и второй элементы И-ИЛИ, причем единичный выход перниэго триггера соединен с ед1гаичным входом второго триггера и с первым входом первого элемента И-ИЛИ, нулевой выход первого триггера соединен с первым входом вторюго элемента И-ИЛИ, единичный выход второго триггера соединен с первым входом блока формирования сигнала ошибки, выход которого является выходом устройства, выход контролируемой схемы .сравнения соединен со вторым входом блока формирования сигнала ошибки, третий вход которого соединен с единичным выходом третьего триггера, тактовый вход устройства соединен с тактовыми входами второго и третьего триггеров, о т л и ч а ю щ е е с я,тем, что, с целью повышения производительности, в устройство введены первый и второй регистры сдвига и четвертый триггер, причем выходы первого и второго элементов И-ИЛИ соединены с информационными входами первого и второго регистров сдвига соответственно, информационные выходы первого и второго регистров сдвига соединены с первым и вторым входами контролируемой схемы сравнения, выход переполнения первого регистра сдвига соеди71ен со счетным входом первого Tplirrepa и со вторыми входами первого и второго элементов И-ИЛИ, выход переполнения второго регистра сдвига соединен с третьими входами первого и второго элементов И-ИЛИ и со счетным входом, четвертого триггера, нулевой выход которого соединен с четвертыми входами первого и второго элементов И-ИЛИ, единичный выход четвертого триггера соединен со входом третьего триггера, тактовый вход устройства соединен с тактовыми входами первого и второго регистров сдЕШга. Источншш информации, принятые во внимание при экспертазе 1.Авторское свидетельство СССР № 473180, кл. G06 F 7/04, 1973. 2.Авторское свидетельство СССР № 583436, кл.ООб F И/ОО, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля схем сравнения | 1980 |

|

SU940162A1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| Устройство для контроля @ -разрядных схем сравнения | 1984 |

|

SU1187171A1 |

| Устройство для контроля схем сравнения | 1984 |

|

SU1218386A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля регистра сдвига | 1981 |

|

SU964646A1 |

| Устройство для контроля регистра сдвига | 1987 |

|

SU1476471A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

Авторы

Даты

1980-09-30—Публикация

1978-08-28—Подача