I

Изобретение относится к автоматике и вычислительной технике и может быть использовано нри реализации технических средств проверки электронных блоков дискретной автоматики и вычислительных машин.

Известно устройство для проверки логических схем, которое может быть применено для проверки схем сравнения IJ. Однако вследствие своей универсальности это устройство сложно и дорого. Известно также сравнительно простое устройство для проверки схем сравнения, однако процесс проверки этим устройством достаточно сложен 2j. Иаиболее олизким к изобретению техническим решением является устройство для контроля схем сравнения, содержаш,ее элемент И и нервый и второй счетчики, выходы разрядов которых подключены к соответствующим входам контролируемой схемы сравнения, выход которой подключен к первому входу логического блока, второй и третий входы которого соединены с выходами первого и второго триггеров соответственно, а первый вход первого триггера подключен к выходу второго счетчика 3. Это устройство не обеспечивает надежного контроля схем сравнения. Чтобы убедиться в этом, можно выписать последовательность двоичных чисел А и Б, записываемых на каждом такте в первом и втором счетчиках. Сравнивая состояния одноименных разрядов обоих счетчиков на каждом такте и выделяя в каждом случае пару разрядов, определяюш,ую знак соотношения чисел А и В (А В, или , можно убедиться, что соотношение А.В во всех случаях определяется нарой первых разрядов счетчиков. Гаким образом, первый (младший) разряд схемы сравнения проверяется только лишь на условие , а остальные - на условие . Кроме того, его логический блок выдает ложный сигнал «Неисправно на последнем такте работы.

Целью изобретения является повышение достоверности контроля схем сравнения за счет обеспечения полного объема нроверки.

В онисываемом устройстве это достигается тем, что в него введены элемент задержки и элемент ИЛИ, выход которого подключен ко входу второго счетчика, первый вход - ко входу первого счетчика и к тактовой шине, а второй вход - к выходу первого счетчика, к первому входу второго триггера и через элемент задер кки ко второму входу первого триггера и к нервому входу элемента И, второй вход которого подключен к выходу второго счетчика, а выход - ко второму входу второго триггера.

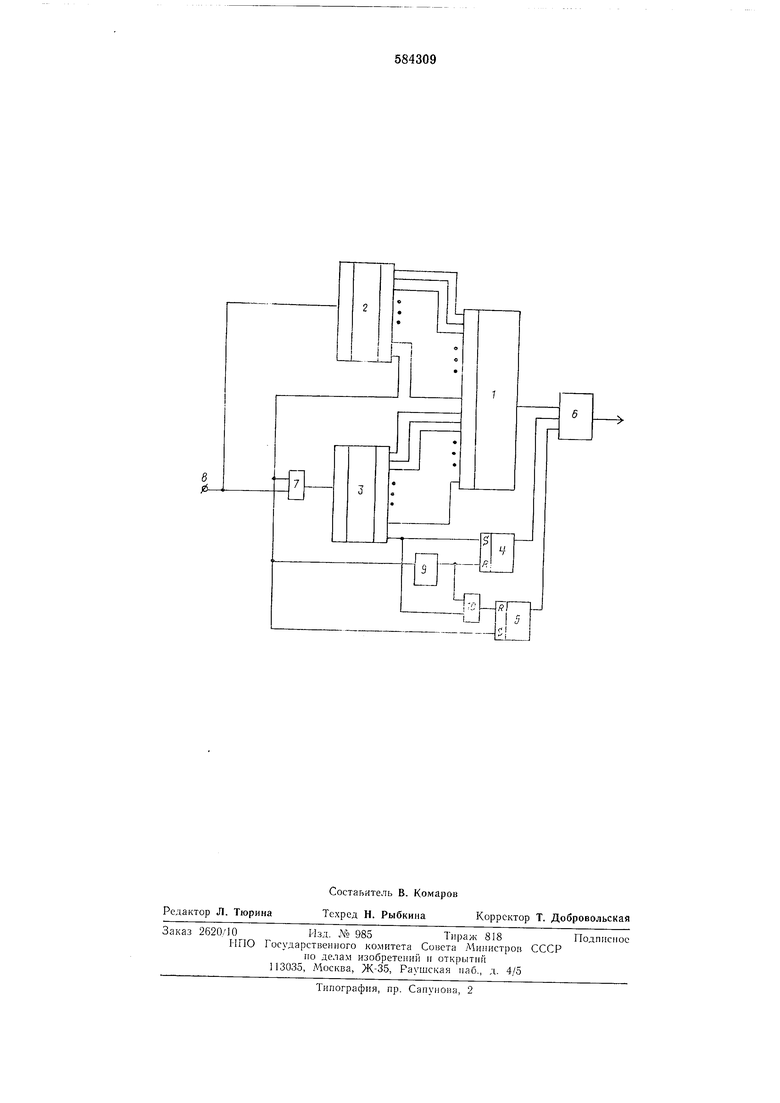

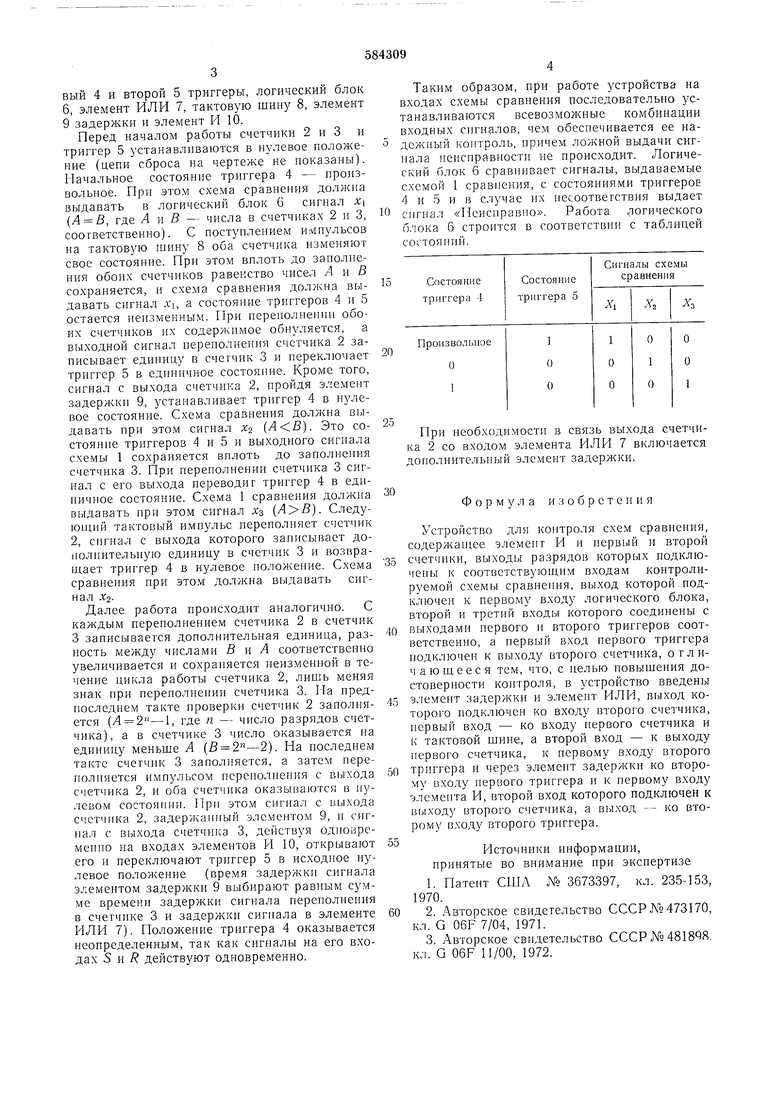

На чертеже представлена функцнональная схема описываемого устройства.

Оно содержит контролируемую схему 1 сравнения, первый 2 и второй 3 счегчики, первый 4 и второй 5 триггеры, логический блок 6, элемент ИЛИ 7, тактовую шину 8, элемент 9 задержки и элемент PI 10.

Перед началом работы счетчики 2 и 3 и триггер 5 устанавливаются в нулевое ноложеиие (цени сброса на чертеже не ноказаны). Начальное состояние триггера 4 - ироизвольное. При этом схема сравнения должна выдавать в логический блок 6 сигнал Xi {А В, где Л и В - числа в счетчиках 2 н 3, соответственно). С ностунлением имиульсов на тактовую шину 8 оба счетчика изменяют свое состояние. При этом внлоть до занолнения обоих счетчиков равенство чисел А и В сохраняется, и схема сравнения должна выдавать сигнал ..xl, а состояние триггеров 4 и 5 остается неизменным. При неренолненни обоих счетчиков их содержимое обнуляется, а выходной сигнал нереиолнения счетчика 2 занисывает единицу в счегчик 3 и нереключает триггер 5 в единичное состояние. Кроме того, сигнал с выхода счетчика 2, нройдя элемент задержки 9, устанавливает триггер 4 в нулевое состояние. Схема сравнения должна выдавать ири этом сигнал х (). Это состояние триггеров 4 и 5 и выходного сигнала схемы 1 сохраняется вплоть до занолнення счетчика 3. При неренолнении счетчика 3 сигнал с его выхода иереводиг триггер 4 в единичное состояние. Схема 1 сравнения должна выдавать нрн этом сигнал лз (). СледуЮИ1ИЙ тактовый имнульс нереполняет счетчик 2, сигнал с выхода которого занисывает до11олнителы1ую единицу в счетчик 3 и возвращает триггер 4 в нулевое положение. Схема сравнения нри этом должна выдавать сигнал х.

Далее работа нроисходит аналогично. С каждым неренолнением счетчика 2 в счетчик 3 записывается дополнительная единица, разность между числами В и Л соответственно увеличивается и сохраняется неизмеииой в течение цикла работы счетчика 2, лишь меняя знак нри нереполнении счетчика 3. Па иредноследнем такте нроверки счетчик 2 заполняется (Л , где п - число разрядов счетчика), а в счетчике 3 число оказывается на единицу меньше Л (.6 ). На носледнем такте счетчнк 3 заполняется, а затем переполняется импульсом переполнения с выхода счетчика 2, и оба счетчика оказываются в нулевом состояпии. При этом сигнал с выхода счетчика 2, задержанный элементом 9, и сигнал с выхода счетчика 3, действуя одновременно на входах элементов И 10, открывают его и переключают триггер 5 в исходное нулевое положение (время задержки сигнала элементом задержки 9 выбирают равным сумме времени задержки сигнала иеренолнения в счетчике 3 и задержки сигнала в элементе ИЛИ 7). Положение триггера 4 оказывается неопределенным, так как сигналы на его входах S н R действуют одновременно.

Таким образом, нри работе устройства на входах схемы сравнения последовательно устанавливаются всевозможные комбинации входных сигналов, чем обеспечивается ее надежный контроль, нричем ложной выдачи сигнала неиснравности не происходит. Логический блок 6 сравнивает сигналы, выдаваемые схемой 1 сравнения, с состояниями триггеров 4 и 5 и в случае их несоответствия выдает сигнал «Неиснравно. Работа логического б.юка б строится в соответствии с таблицей состояний.

При необходимости в связь выхода счетчика 2 со входом элемента ИЛИ 7 включается дополнительный элемент задержки.

Формула изобретения

Устройство для контроля схем сравнения, содержащее элемент И и первый и второй счетчики, выходы разрядов которых нодключепы к соответствуюни-1м входам контролируемой схемы сравнения, выход которой.подключен к первому входу логического блока, второй и третий вход.ы которого соединены с выходами первого н второго триггеров соответственно, а нервый вход первого триггера иодключеи к выходу второго счетчика, отличаюшееся тем, что, с целью повышения достоверности контроля, в устройство введены элемент задержки и элемент ИЛИ, выход которого подключен ко входу второго счетчика, нервый вход - ко входу нервого счетчика и к тактовой шине, а второй вход - к выходу нервого счетчика, к первому входу второго триггера и через элемент задержки ко второму входу нервого триггера и к первому входу элемента И, второй вход которого подключен к В1)1ходу второго счетчика, а выход - ко второму входу второго триггера.

Источники информации, нринятые во внимание ири экспертизе

1.Патент США № 3673397, кл. 235-153, 1970.

2.Авторское свидетельство СССР 473170, кл. G 06F 7/04, 1971.

3.Авторское свидетельство СССР №481898. кл. G 06F 11/00, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬ ФУНКЦИЙ СИНУСА И КОСИИУСА | 1971 |

|

SU419896A1 |

| Устройство для передачи информации с обратной связью | 1986 |

|

SU1322356A1 |

| Устройство для проверки схем сравнения двоичных чисел | 1973 |

|

SU481898A1 |

| Последовательное буферное запоминающее устройство с самоконтролем | 1985 |

|

SU1302321A1 |

| Устройство для вычисления первой разности | 1972 |

|

SU475618A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| УСТРОЙСТВО для КОДИРОВАНИЯ РЕЗУЛЬТАТОВ ПРОГРАММНОГО КОНТРОЛЯ | 1969 |

|

SU249058A1 |

| Цифровой фазовращатель | 1984 |

|

SU1239630A1 |

| Микропрограммное устройство управления | 1981 |

|

SU955061A1 |

| Устройство для диагностики неисправностей многоярусных пирамидальных табличных схем | 1976 |

|

SU595736A2 |

Авторы

Даты

1977-12-15—Публикация

1976-07-07—Подача