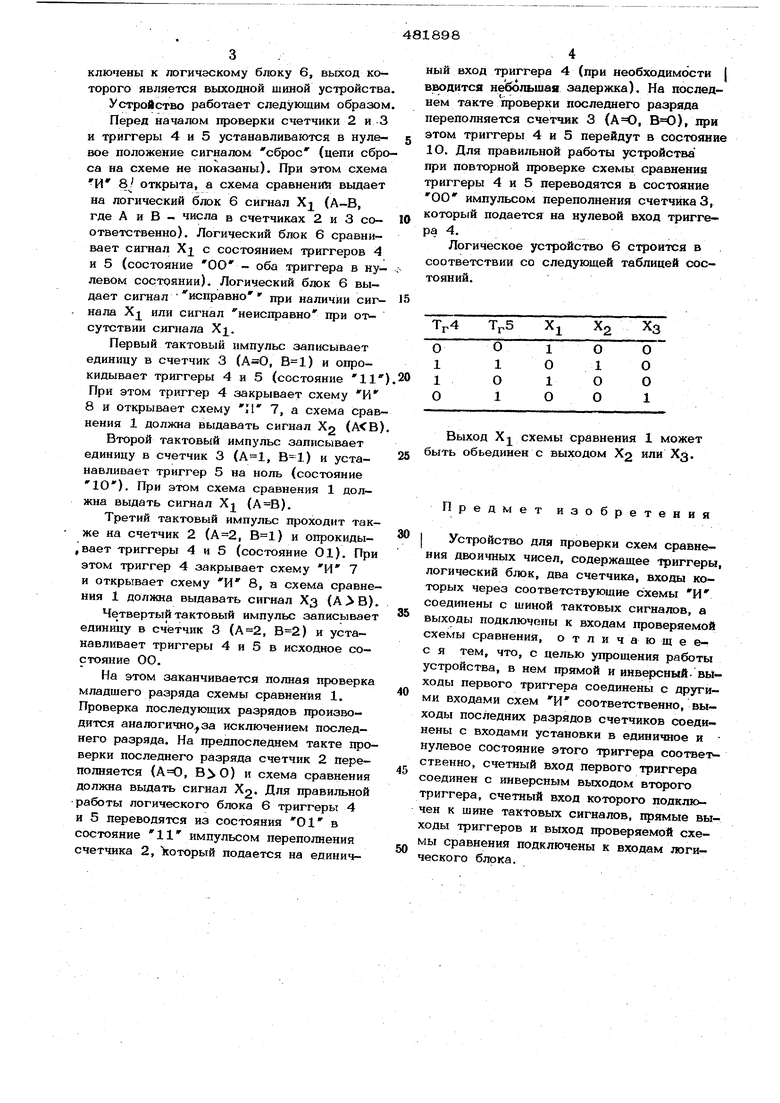

(54) УСТР- ОЙСЛВО ДЛЯ ПРОВЕРКИ СХЕМ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ ключены к логичаскому блоку 6, выход которого является выходной шиной устройства Устройство работает следующим образом Перед началом проверки счетчики 2 и 3 и триггеры 4 и 5 устанавливаются в нулевое положение сигналом сброс (цепи сбро са на схеме не показаны). При этом схема И 8/ открыта, а схема сравнений вьщает на логический блок 6 сигнал Xj (А-В, где А и В - числа в счетчиках 2 и 3 соответственно). Логический блок 6 сравнивает сигнал X;j с состоянием триггеров 4 и 5 (состояние 00 - оба триггера в нулевом состоянии). Логический блок 6 выдает сигнал исправно при наличии сиг- нала Xj или сигнал неисправно при от сутствии Сигнала Х. Первый тактовый импульс записывает единицу в счетчик 3 (, ) и опрокидывает триггеры 4 и 5 (состояние 11 При этом триггер 4 закрывает схему И 8 и открывает схему 7, а схема сравнения 1 должна выдавать сигнал Х2 () Второй тактовый импульс записывает единицу в счетчик 3 (, ) и устанавливает триггер 5 на ноль (состояние 10), При этом схема сравнения 1 должна выдать сигнал Xj (). Третий тактовый импульс проходит также на счетчик 2 (А 2, ) и опрокиды,вает триггеры 4 и 5 (состояние 01). При этом триггер 4 закрывает схему И 7 и открывает схему И 8, а схема сравнения 1 должна выдавать сигнал Хз (). Четвертый тактовый импульс запись1вает единицу в счётчик 3 (А 2, ) и устанавливает триггеры 4 и 5 в исходное состояние 00. На этом заканчивается полная проверка младшего разряда схемы сравнения 1. Проверка последующих разрядов производится аналогично. за исключением последнего разряда. На предпоследнем такте проверки последнего разряда счетчик 2 переполняется (, ) и схема сравнения должна вьщать сигнал Х2- Для правильной работы логического блока 6 триггеры 4 и 5 переводятся из состояния 01 в состояние 11 импульсом переполнения счетчика 2, 1который подается на единичый вход триггера 4 (при необходимости j водится небольшая задержка). На последем такте проверки последнего разряда ереполняется счетчик 3 (, ), при том триггеры 4 и 5 перейдут в состояние 1О. Для правильной работы устройства ри повторной проверке схемы сравнения риггеры 4 и 5 переводятся в состояние 00 импульсом переполнения счетчика 3, оторый подается на нулевой вход триггеа 4. Логическое устройство 6 строится в соответствии со следующей таблицей состояний. Выход X j схемы сравнения 1 может быть объединен с выходом Х2 или ХзПредмет изобретения I Устройство для проверки схем сравнения двоичных чисел, содержащее триггеры, логический блок, два счетчика, входы которых через соответствующие схемы И соединены с шиной тактовых сигналов, а выходы подключены к входам проверяемой схемы сравнения, отличающеес я тем, что, с целью упрощения работы устройства, в нем прямой и инверсный- BBIходы первого триггера соединены с другими входами схем И соответственно, выходы последних разрядов счетчиков соединены с входами установки в единичное и нулевое состояние этого триггера соответственно, счетный вход первого триггера соединен с инверсным выходом второго триггера, счетный вход которого подключен к шине тактовых сигналов, прямые выходы триггеров и выход проверяемой схемы сравнения подключены к входам логического блока.

7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля схем сравнения | 1979 |

|

SU960822A1 |

| Устройство для контроля схем сравнения | 1976 |

|

SU584309A1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

| Сигнализатор совпадения фаз | 1990 |

|

SU1824595A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля схем сравнения | 1980 |

|

SU940162A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900437A2 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для проверки схем сравнения | 1973 |

|

SU473180A1 |

Авторы

Даты

1975-08-25—Публикация

1973-07-16—Подача