(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1979 |

|

SU834766A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Буферное запоминающее устройство | 1980 |

|

SU888202A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1984 |

|

SU1238054A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

.1

Изобретение относится к области вычислительной техники.

Извести о буферное запоминающее устройство (БЗУ), которое позволяет переаавать информацию в одном направлении. Недостатьком данного устройства является невозможность передачи информации в двух направлениях Ij..

Наиболее близким к изобретению являетей БЗУ 2, содержащее накопитель, один из входов которого соединен через первую группу элементов И с входными шинами и управляющими шинами записи, а выход через вторую группу элементов И соединен с выходными шинами и управляющими шинами считывания, блок формирования адресов записи и считывания, выходы которых подключены ко входам схемы сравнения. Выход схемы сравнения соединен с одним из входов первого элемента И, другой вход которого подключен ко входу блока формирования адресов считывания и первой адресной шине. 1ход первого элемента И соединен с одним из входов первого элемента ИЛИ, другой вход которого соединен со второй

адресной шиной, а выход - со входом блока формирования адресов записи.

Недостатком такого устройства являются ограниченные функциональные возможности, например, в старт-стопных системах передачи (приема) информации необходимо использовать два накопителя со схемами управления: один - для согласования канала передачи информации, другой - для согласования канала приема информации.

Целью изобретения является расширение области применения устройства.

Для достижения поставленной цели npefVложенное устройство содержит второй и третий элементы И и ИЛИ. Выходы второго и третьего элементов И соединены с другим входом накопителя, входы - с выходами блоков формирования адресов записи и считывания, а вторые входы - с выходами второго и третьего элементов ИЛИ, входь которых подключены к управляющим шинам записи и считывания.

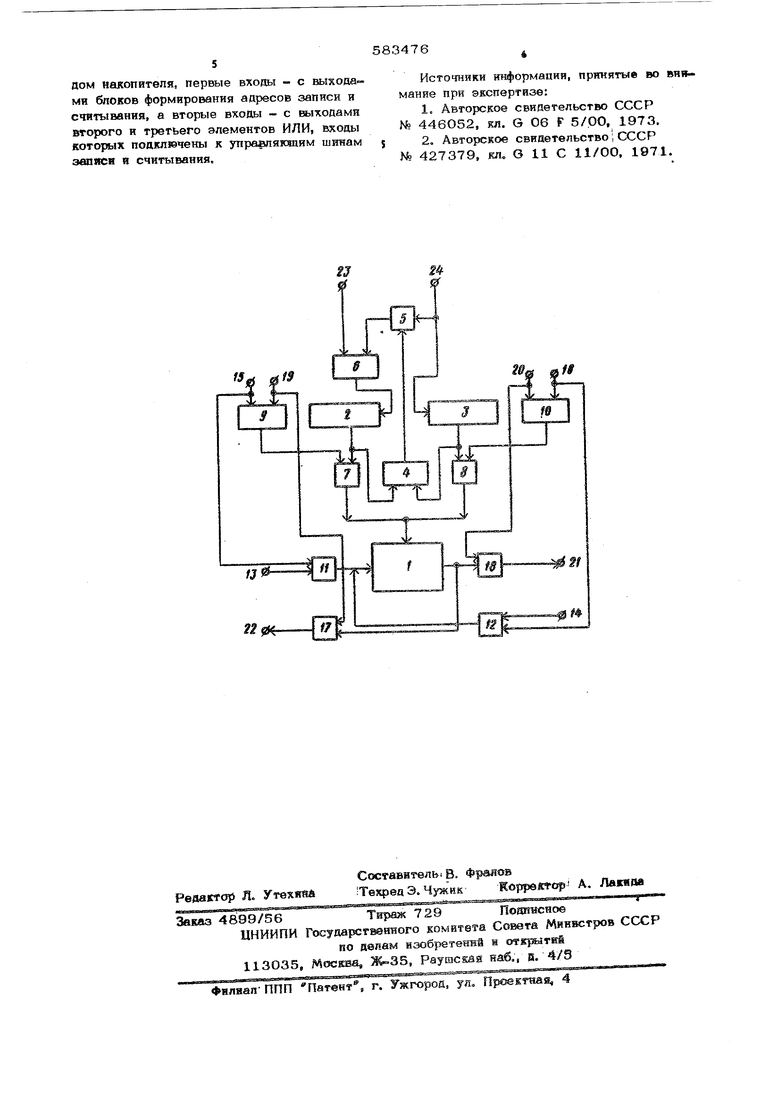

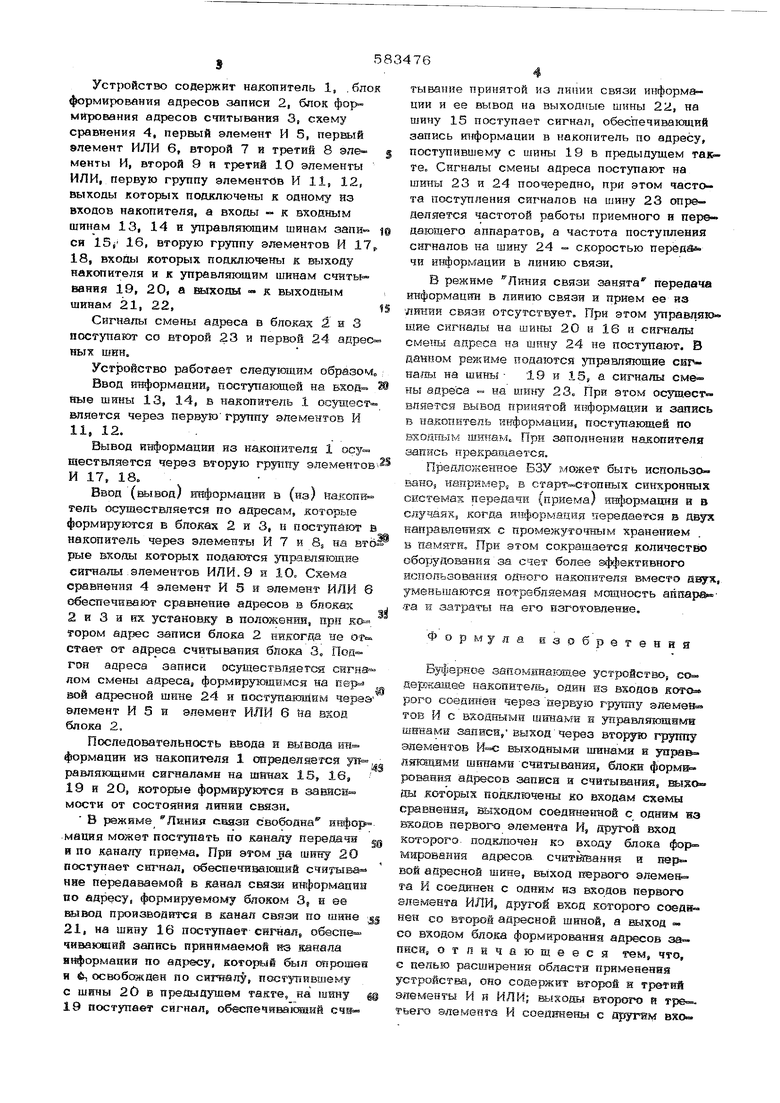

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит накопитель 1, .блок формирования адресов записи 2, блок формирования адресов считывания 3, схему сравнения 4, первый элемент И 5, первый элемент ИЛИ 6, второй 7 и третий 8 эле- § менты И, второй 9 и третий 10 элементы ИЛИ, первую группу элементов И 11, 12, выходы которых подключены к одному из входов накопителя, а входы - к входным шинам 13, 14 и управлягошим шинам запи g си 15j 16, вторую группу элементов И 17 18, вхос(ы которых подключены к выходу наксшителя и к управляющим шинам счйть вапля 19, 20, а шлхооы « к выходным шинам 21, 22,fS

Сигналы смены адреса в блоках 2 и 3 поступают со второй 23 и первой 24 айрео ных шин,

Усг эойство работает следующим образом

Ввод ргаформации поступающей на &xofb ные шины 13, 14, в накопитель 1 осу1цвст« вляегся через первую группу элементов И 11, 12.

Вывод информации из накопителя 1 осу ществляется через вторую группу элемеитов И 17, 18.

Ввод (вывод) 1шформаа1зи в (из) Накопи гель осушествляется по адресам, которые формируются в блоках 2 и 3, и поступйют в накопитель через элементы И 7 и 8, на вто рые входы которых подаются управляюшие сигналы ,элементов ИЛИ. 9 и 1О. Схема сравнения 4 элемент И S и элемент ИЛИ 6 обеспечивают сравнение адресов в блоках 2 и 3 и их установку в положении, при кем fopoM адрес записи блока 2 никогда не 0-г стает от адреса считывания блока 3. Подгон адреса записи осу1аесгв11яегс54 сигналом смены адреса, формирующимся на пвр вой адресной шине 24 и поступающим череэ элемент И 5 и элемент ИЛИ 6 tia аход блока 2.

Последовательность ввода н вывода ин формации из накопителя 1 оп делнется У№,з равлякацими сигналами на шинах 15, 16, 19 и 2 О, KOTOpbie формируются в зависн мости от состояния линии связи.

в южймв Линия свази СБободна инфор. мацня может поступать по каналу передача а по каналу приема, Прн этом на шину 20 поступает снгнал, обвспечнаагсацнй счигыва нне передаваемой в каяал связн )ормацна по адресу, формируемому блоком 3, н ее производится в канал связи по шине ,§3 21, на шину 16 поступает Сигнал обеспе-чивакиций запись принимаемой кз канала И1й} ормании по адресу, который бып опрошен я освобожаен по сигтшл5, поступившему с шнны 20 Б преды душем такте, на шину g@ 19 поступает сигнал, с еспечивакжций сч

тыванне принятой из пинии связи информации и ее вывод на выходные шнны 22, на шину 15 поступает сигнал, обеспечивающий запись информации в накопитель по адресу, поступившему с шины 19 в предыдущем такте. Сигналы смены адреса поступают на шины 23 и 24 поочередно, при этом частота поступления сигналов на шину 23 определяется частотой работы приемного и передающего аппаратов, а частота поступления Сигналов на шину 24 - скоростью переда, чи и 1формации в линию связи.

В режиме Линия связи занята передача информацш в линию связи и прием ее из линия связи отсутствует. При этом управляю шие Сигналы на шилы 20 и 16 и сигналы смены адреса на шину 24 не поступают, В даниом режиме подаются управляющие сигналы на шины 19 и 15, а сигналы смены адреса «- на шину 23 При этом осушествляе-тся вывод принятой информации и зштись в накопитель информации, поступающей по вхойпым При запопненаи накопителя запись прекравдаегся.

Предложенное БЗУ может быть испопьзо ваноз напримерг в старг.- ст-опиь5х синхронных системах передачи (приема) ин |юрмашга и в случаяк, когда информация передается в двух нап1заБлвШ ях с промежуточным хранением . в памяти. При этом сокращается количество оборудования за счет более эффективного использования одного накопителя вместо йву уменьшаются потребляемая мощность аппар®ТВ Е затрать на его нзготовление.

Формула изобретеннй

Буферное запоминаюхаее устройство, со деркащеё накопнтель, один из входов котгь рого соединен через еервую группу эламеа тов И с входными ш1Гйаь5й н управляюшнми швнами записи,- выход через вторую группу элементов выходными шинами и уарав. йякйннмй шинами считывания, блоки форм№ ровааия айрееов записи и считывания, ды которых подключены ко входам схемы сраваення, выходом сойдине гаой с одним на вкодов первог-о элемента И, другой вход которого, подключен ко входу блока фор Мйрования айресов. считывания и первой адресной шйне, выход первого элеме та И соединен с одним из входов первого элемента ИЛИ, другой вход которого соединен со второй адресной шиной, а к.ход .« со входом блока формирования адресов за. пйсй, отпачающееся тем, что, € кепью расширения области применений устройства, оно содержит второй н третий элементы И и ИЛИ; а.1ходы второго и тр&. тьего элемента И соейинены с другим вхо

Дом накопителя, первые входы - с выхода ми блоков формирования адресов записи и считывания, а вторые входы - с выходами второго и третьего элементов ИЛИ, входы которых подключены к управляющим шинам записи и считывания.

Источники информации, принятые во вня мание при экспертизе:

№ 427379, кл, G 11 С 11/00, 1971.

fj

2

0

FS Т

Авторы

Даты

1977-12-05—Публикация

1976-01-13—Подача