Изобретение относится к области запоминающих устройств. Известно буферное запоминакяцее устройство (БЗУ). содержащее счетчик, элементы И, элементы задержки, элемент памяти н блок управления l). Недостатком этого устройства является .,ТО, что при большой неравномерности поступ ления входной информации происходит переполнение счетчика, что снижает надежность работы устройства. Наиболее близким техническим решением к изобретению является БЗУ, содержащее счетчики импульсов считывания и записи, первые выходы которых подключены через дешифраторы считывания и записи ко входа накопителя, вторые соединены со входами компаратора, элемент задержки, подключенный через первый элемент И ко входу счетчика импульсов считывания, третьи выходы которого соединены со вторым элементом И, третий, четвертый и пятый элементы И, триггеры и тактоыле шины записи и считывания 2J. Недостатком этого устройства является сложность и ненадежная работа при больших неравномерностях поступления входной информации. Например, при аварийных режимах переполнения происходит не только потеря информации, но и наложение ее на ранее записанную информацию в накопителей. Цель изобретения - упрощение и повышение надежности устройства при аварийных режимах переполнения. Поставленная цель достигается тем, что в предложенном устройстве шлход второго элемента И подключен к нулевым входам первого и второго триггеров. Третьи выходы счетчика импульсов записи -через третий элемент И подключены к единичному входу второго триггера, прямой выход которого через четвертый элемент И соединен с единичным входом первого триггера. Входы пятого элемента И- подключены соответственно к выходам компаратора, к тактовой шине считывания и инверсному выходу второго триггера, а выход пятого элемента И с нуле№1м входом третьего триггера. Инверсный выход первого триггера и прямой

выход третьего триггера соединены соответственно с блокирукндими входами дешифраторов записи и считывания. Тактовая шина записи подключена ко входам счетчика импульсов записи и четвертого элемента И и к единичному входу третьего TpHrrepia.

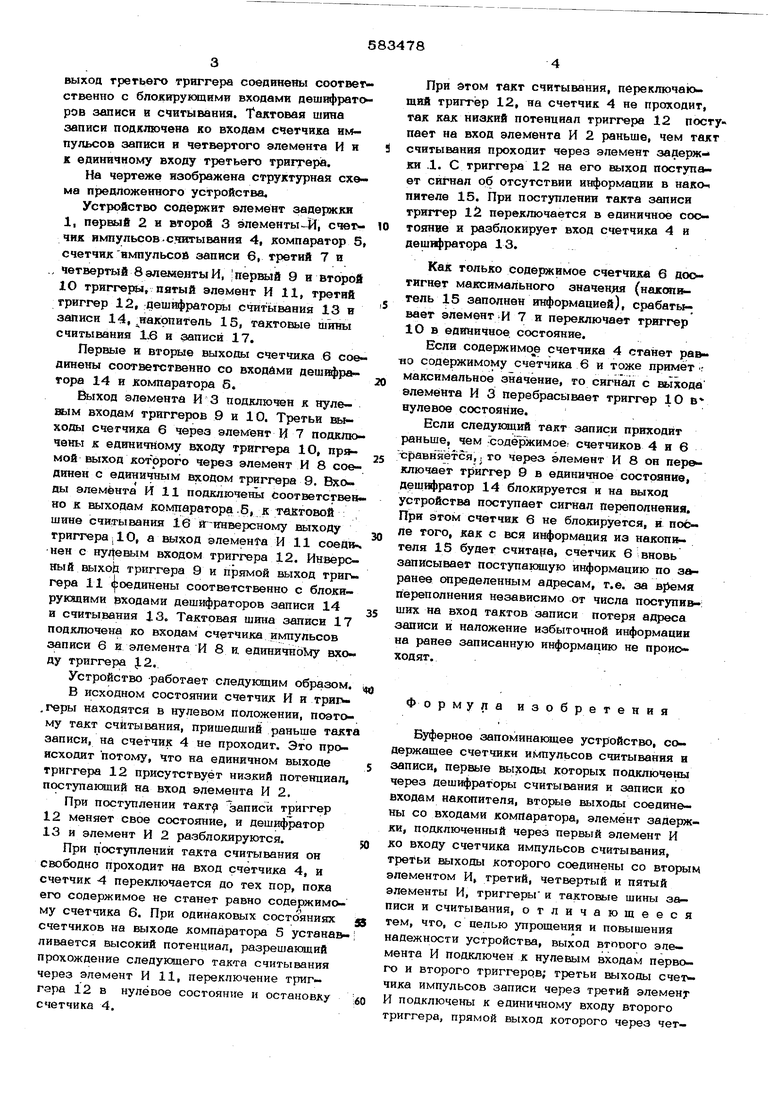

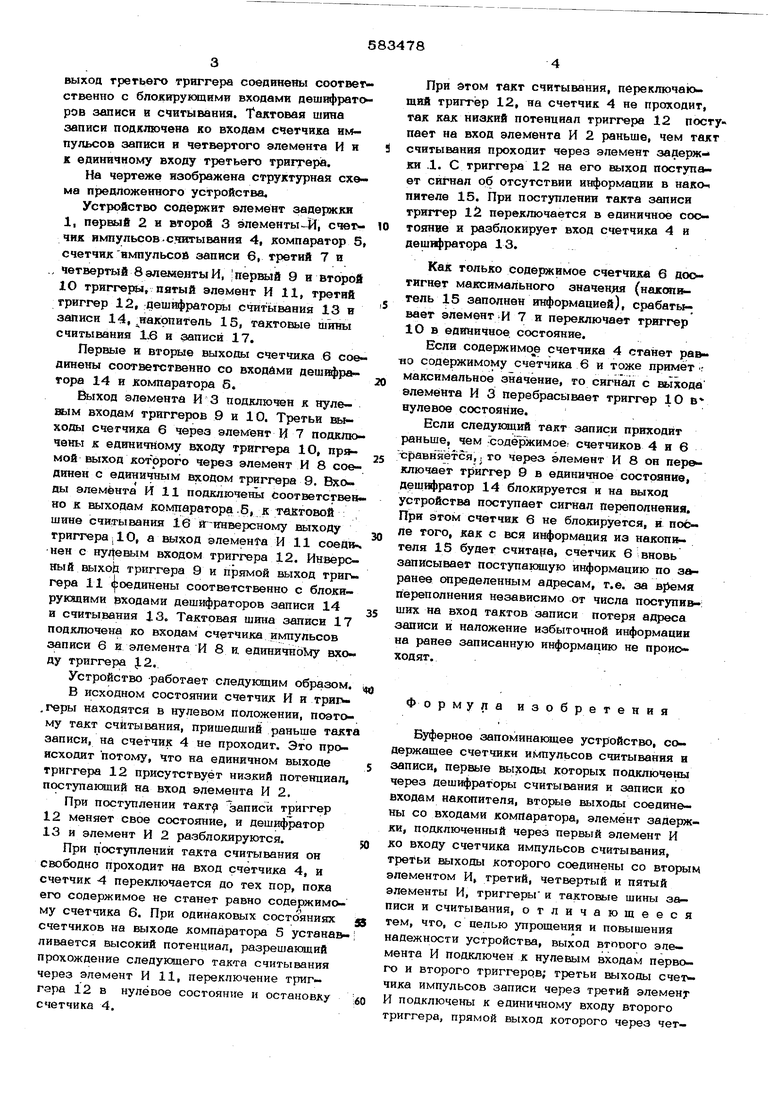

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит элемент задеркки 1, первый 2 и второй 3 элементы-Й, счетчик импульсов.с 0ггывания 4, компаратор 5, счетчикимпульсов записи 6, третий 7 и , четвертый 8 элементы И, першлй 9 и второй 1О триггеры, пятый элемент И 11, третий триггер 12, гдешйфраторы считывания 13 и записи 14, накопитель 15, тактовые шины считывания Ij6 и записи 17.

Первые я вторые выходы счетчика 6 соединены соответственно со входами дешг фратора 14 и компаратора 6.

Выход элемента И 3 подключен к нуле- Шз1м входам триггеров 9 и 10. Третьи выходы счетчика 6 через И 7 подключены к единичному входу триггера 10, прямой выход котррого через элемент И 8 соединен с единичным исодом триггера 9. Входы элемента И 11 подключены соответствен но к выходам компаратора .6, к тй&товой шине считывания 16 йг-инверсному выходу триггера, 10, а выход элемента И 11 соедтк нен с нулевым входом триггера 12. Инверсный аыхой триггера 9 и прямой выход триггера 11 «роединены соответственно с блокирующими входами дешифраторов записи 14 и считывания 13. Тактовая шина записи 17 подключена ко входам счетчика импульсов записи 6 и элемента И 8 и входу триггера J.2.

Устройство работает следукшим образом,

В исходном состоянии счетчик И и триг,геры находятся в нулевом положении, поэтому такт считывания, пришедший раньше такт записи, на счетчик 4 не проходит. Это происходит потому, что на единичном выходе триггера 12 присутствует низкий потенциал, пс ступа1сяций на вход элемента И 2.

При поступлении такт Записи триггер

12меняет свое состояние, и дешифратор

13и элемент И 2 разблокируются. При поступлений такта считывания он

свободно проходит на вход счетчика 4, и счетчик 4 переключается до тех пор, пока его содержимое не станет равно содержимому счетчика 6. При одинаковых состояниях счетчиков на выходе компаратора 5 устана&ливается высокий потенциал, разрешающий прохождение следующего такта считывания через эпемент И 11, переключение триггера 12 в нулевое состояние и остановку счетчика 4.

При этом такт считывания, переключающий триггер 12, на счетчик 4 не проходит, так как низкий потенциал триггера 12 постпает на вход элемента И 2 раньше, чем так считывания проходит через элемент задержки .1. С триггера 12 на его выкоа поступает сигнал об отсутствии информации в нако-i пятеле 15. При поступлении такта записи триггер 1Й переключается в единичное состояние и разблокирует вход счетчика 4 и дешифратора 13.

Как только содержимое счетчика 6 достигнет максимального значения (накопитель 15 заполнен информацией), срабаты-; вает элементен 7 и переключает триггер 10 в единичное состояние.

Если содержимо е счетчика 4 станет рав-ао содержимому счетчика 6 и тоже примет т максимальное значение, то сигнал с выхода элемента И 3 перебрасывает триггер 10 в нулевое состояние.

Если следующий такт записи приходит раньше, чем -содё ржимое счетчиков 4 и 6 -сравняется,, то через элемент И 8 он переключает триггер 9 в единичное состояние, дешифратор 14 блокируется и на выход устройства поступает сигнал переполнения. При этом счетчик 6 не блокируется, и после того, как с вся информация из накопителя 15 будет считара, счетчик 6 вновь записывает поступакшую информацию по заранее определенным адресам, т.е. за время переполнения независимо от числа поступивших на вход тактов записи потеря адреса записи и наложение избыточной информация на ранее записанную информацию не проиоходят.

Формула изобретения

Буферное запоминающее устройство, содержащее счетчики импульсов считывания и записи, первые Шзгходы которых подключены через дешифраторы считывания и записи ко входам накопителя, второю выходы соединены со входами компаратора, элемент задержки, подключенный через первый элемент И ко входу счетчика импульсов считывания, третьи Еыходы которого соединены со вторым элементом И, третий, четвертый и пятый элементы И, триггеры и тактовые шины записи и считывания, отличающееся тем, что, с целью упрощения и повышения надежности устройства, выход втпоого эпе- мента И подключен к нулевым входам первого и второго триггеров; третьи выходы счет. чика импульсов записи через третий элемент И подключены к единичному входу второго триггера, прямой выход которого через четвертый элемент И соединен с единнчнык вхоЦом первого триггера; вхопы пятого элемента И подключены соответственно к выходам компаратора, к тактовой шине считывания и инверсному;выходувтороготрйггера, а выход пятого элемента И соединен с нулевым входом третьего триггера; инверсный выход первого триггера и прямой выход третьего триггера соединены соответственно с блокирующими входами дешифраторов

записи и считывания; тактовая шина записи подключена ко входам счетчика нмпупьсов записи и четвертого элемента И и к единичному входу третьего триггера.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР

№ 446052, М. Кл. О 06 F 5/ОО, 1973 г.

2. Патент США № 3648247, КЛ. 34О-.172.5, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Устройство для сопряжения | 1983 |

|

SU1176337A1 |

| Анализатор экстремумов | 1984 |

|

SU1233173A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Генератор многомерных случайных процессов | 1990 |

|

SU1755279A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Устройство для считывания графической информации | 1984 |

|

SU1182553A1 |

| Устройство для регистрации информации | 1984 |

|

SU1234858A1 |

| Устройство для управления сортировкой штучных изделий | 1982 |

|

SU1375535A1 |

Авторы

Даты

1977-12-05—Публикация

1976-02-06—Подача