Устройство может быть использовано в машинах для автоматическото контроля и диагностики неисправностей ЦВМ и, в частности, в агрегатном устройстве программного контроля.

Известны устройства для кодирования результатов анализа схем, входящие в устройства программного контроля, содернсащие регистр кода неисправности и дешифратор выборки разряда этого регистра. В этих устройствах результат контроля представляется в виде кода неисправности, каждый разряд которого соответствует одной из подпрограмм теста. Каждая подпрограмма предусматривает несколько тактов воздействия jia /контролируемую схему и сравнение отвётйой реакции схемы с реакцией иснравной схемы. Результат сравнения (при равенстве -«1, при неравенстве- «О) записывается в соответст;вуюш.ий данной подпрограмме разряд регистра кода неисправности. Однако для многих типов схем более предпочтительны алгоритмы анализа со сравнением на каждой подпрограмме реакции контролируемой схемы как с реакцией исправной схемы, так и с реакциями, соответствующими наиболее вероятным неисправностям. При этом длина диагностического теста существенно сокращается. При использовании этих алгоритмов на каладой подпрограмме получается п результатов сравнения, где п-число эталонных реакций (/г 1), и в известных устройствах кодирования результатов требуется л разрядов регистра кода неисправности. Поскольку реакция контролируемой схемы

в нормальном случае может равняться только одной из п эталонных реакций, результат контроля оказывается представленным в сильно избыточном коде. Это требует либо сокращения максимально допустимого числа подпрограмм в тесте, либо существенного увеличения числа запоминающих элементов. Кроме того, избыточность кода затрудняет его дальнейщую обработку и использование для поиска координат отказавщего элемента по диагностической таблице.

В предлагаемом устройстве сжатие информации и расширение логических возможностей достигаются тем, что оно содержит первый и второй коммутаторы, счетчик, вспомогательный регистр и схему прерывания программ, причем входы первого коммутатора связаны с выходом вспомогательного регистра, с выходами схемы сравнения блока операций устройства программного контроля, в которое

входит предлагаемое устройство, и с информационными щинами устройства программного контроля, выход этого коммутатора подключен ко входам дещифратора выборки разряда. Входы второго коммутатора соединены со

Неисправности; входы вспомогательного регистра подключены к выходам счетчика и второго коммутатора; входы схемы прерывания соединены с выходами схемы сравнеиия и второго коммутатора, а выходы схемы прерывания связаны с блоком управления устройства программного контроля; синхронизирующие входы этой схемы, а также счетчика и вспомогательного регистра подключены к формирователям микрокоманд блока операций.

Устройство отличается также тем, что схема прерывания программы содержит первый и второй триггеры, причем единичные выходы обоих триггеров соединены со входами элемента «И, выход которого поступает в блок управления. Вход одного из элементов «И установки в «1 нервого триггера и элемента «И установки в «О второго триггера через инвертор СБЯзаиы с выходом второго коммутатора; вход другого элемента «И установки в «1 первого триггера также через инвертор подключен к выходу схемы сравнения блока операций; вход элемента «И установки в «О второго триггера через элемент задержки связан с выходом «1 первого триггера, остальные входы всех элементов «И, а также входы установки в «Ш.. перового триггера и установки в «1 второго триггера связаны с выходами формирователей микрокоманд блока операций.

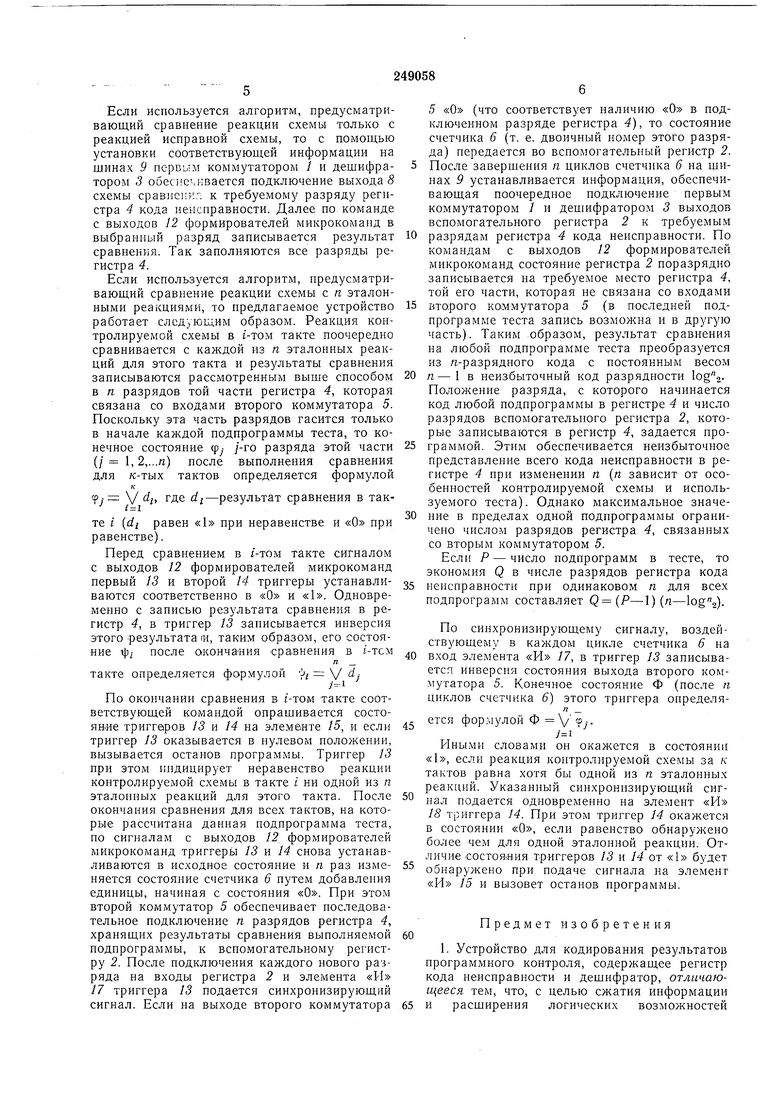

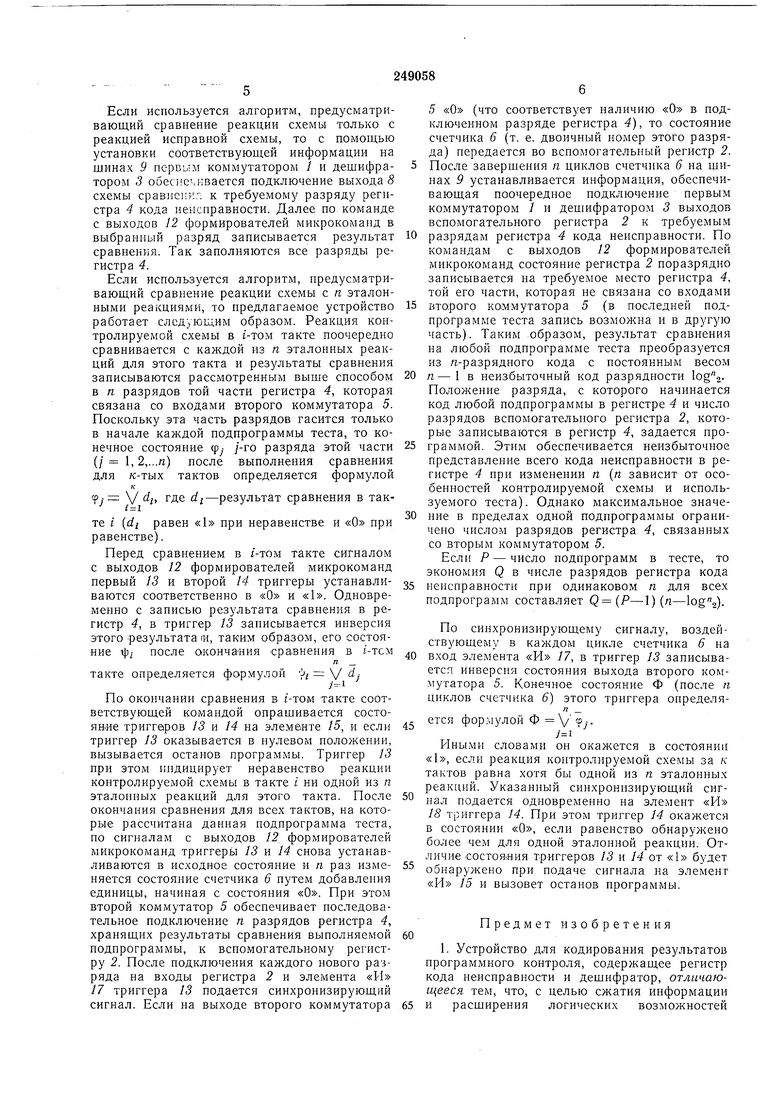

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2-схема прерывания программ, где приняты следующие обозначения: первый коммутатор /, вспомогательный регистр 2, дешифратор 5, регистр 4 кода неисправности, второй коммутатор 5, счетчик 6, схема прерывания 7, выход 8 схемы сравнения, информационные шины 9, выходы 10 регистра кода неисправности на индикаторы, выходы } схемы прерывания в блок управления, выходы 12 формирователей микрокоманд, первый триггер 13 и второй триггер 14, элементы «И 15-18, инверторы 19, 20, элемент 21 задержки, элемент «ИЛИ 22.

Первый коммутатор / связан с выходами вспомогательного регистра 2 и с выходами 8 схемы сравнения блока операций устройства программного контроля, в которое входит Нредлагаемое устройство. Этот коммутатор служит для подключения любого из указанных выходов ко входу дешифратора 5 выборки разряда, который, в свою очередь, подключает выход коммутатора / к любому из разрядов регистра 4 кода неисправности. Управление первым коммутатором 1 и дешифратором 3 осуществляется с помощью связанных с ними информационных шин 9 блока управления устройства программного контроля. Регистр 4 предназначен для хранения кода неисправности и передачи его через выходы 10 На индикаторы или последующую обработку. Часть выходов этого регистра связана со входами второго коммутатора 5, который предназначен для подключения любого из этих выходов к вспомогательному регистру .

С этой целью выход второго коммутатора 5 связан со входом регистра 2. Входы коммутатора 5 связаны также с выходами счетчика 6, который служит для формирования последовательных номеров разрядов (начиная с номера один) регистра 4 кода неисправности, связанных со входами второго коммутатора 5. Если в счетчике 6 установлен номер г, то t-й разряд указанной группы разрядов регистра 4

оказывается подключенным коммутатором 5 к вспомогательному регистру 2. Выходы счетчика 6 связаны также с вспомогательным регистром 2. Этот регистр служит для хранения номера того разряда регистра 4 кода неисправности, в котором записан «О. Причем передача состояния счетчика 6 в регистр 2 производится при наличии сигнала «О на выходе второго коммутатора 5. Схема 7 прерывания программы предназначена для обнаружения непредусмотренного программой контроля поведения контролируемой схемы (нанример, при наличии в схеме кратной или неучтенной одиночной неисправности, либо при неустойчнвой ненснравности). Входы схемы 7 подключены к выходам второго коммутатора 5 и к выходу 5 схемы сравнения. Выходы 11 схемы 7 поступают в блок управления устройства программного контроля для управленияостановом программы. Синхронизирующие входы вспомогательного регистра 2, регистра 4 кода неиснравности, счетчика 6 и схемы 7 прерывания связаны с выходами 12 формирователей микрокоманд блока операций.

Схема прерывания 7 включает два триггера. Первый триггер 13 служит для обнаружения и индикации неравенства реакции схемы и одной из п эталоиных реакций. Второй триггер 14 фиксирует и индицирует равеиство

реакции схемы более чем одной эталонной реакции. В схему прерывания 7 входят также элементы «И 15-18. Элемент 15 связан своими входами с выходами «1 обоих триггеров и служит для формирования сигнала

прерывания программы. Его выход является выходом // схемы прерывания 7. Входы элемента 17 установки в «1 первого триггера 13 и элемента 18 установки в «1 второго триггера 14 через инвертор 19 подключены к выходу второго коммутатора 5. Вход элемента 16 установки в «1 триггера 13 через инвертор 20 соединен с выходом 8 схемы сравнения. Вход элемента 18 через элемент задерл ки 21 связан с выходом «1 первого триггера 13. Элемент

21 служит для нредотвращения срабатывания триггеров 13 и 14 от одной микрокоманды. Выходы элементов 16 и 17 подключены ко входу установки в «О триггера 13 через элемент «ИЛИ 22. Остальные входы всех

элементов «И, а также вход установкн в «О

Если используется алгоритм, предусматривающий сравнение реакции схемы только с реакцией исправной схемы, то с помощью установки соответствующей информации на щинах 9 первым коммутатором 1 и дешифратором 3 о5ес е л-1вается подключение выхода 8 схемы сравксниг: к требуемому разряду регистра 4 кода неисправности. Далее по команде с выходов 12 формирователей микрокоманд в выбранный разряд записывается результат сравнения. Так заполняются все разряды регистра 4.

Если используется алгоритм, предусматривающий сравнение реакции схемы с п эталонными реакциями, то предлагаемое устройство работает следующим образом. Реакция контролируемой схемы в i-TOM такте поочередно сравнивается с каждой нз п эталонных реакций для этого такта и результаты сравнения записываются рассмотренным выше способом в п разрядов той части регистра 4, которая связана со входами второго коммутатора 5. Поскольку эта часть разрядов гасится только в начале каждой подпрограммы теста, то конечное состояние фу /-ГО разряда этой части (/ 1,2,.../г) после выполнения сравнения для к-тых тактов определяется формулой

сру : V где d -результат сравнения в

те i (di равен «1 при неравенстве и «О при

равенстве).

Перед сравнением в /-том такте сигналом с выходов 12 формирователей микрокоманд первый 13 и второй 14 триггеры устанавливаются соответственно в «О и «1. Одновременно с записью результата сравнения в регистр 4, в триггер 13 записывается инверсия этого -результата м, таким образом, его состояние г|;; после окончания сравнения в I-TCM

п

такте определяется формулой j : / d.

/-1

По окончании сравнения в г-том такте соответствующей командой опрашивается состояние триггеров 13 и 14 на элементе 15, и если триггер 13 оказывается в нулевом ноложении, вызывается останов программы. Триггер 13 при этом индицирует неравенство реакции контролируемой схемы в такте / ни одной из п эталонных реакций для этого такта. После окончания сравнения для всех тактов, на которые рассчитана данная подпрограмма теста, по сигналам с выходов 12 формирователей микрокоманд триггерь 13 и 14 снова устанавливаются в исходное состояние и п раз изменяется состояние счетчика 6 путем добавления единицы, начиная с состояния «О. При этом второй коммутатор 5 обеспечивает носледовательное подключение п разрядов регистра 4, хранящих результаты сравнения выполняемой подпрограммы, к вспомогательному регистру 2. После подключения каждого нового разряда на входы регистра 2 и элемента «П 17 триггера 13 подается синхронизирующий сигнал. Если на выходе второго коммутатора

5 «О (что соответствует наличию «О в подключенном разряде регистра 4), то состояние счетчика 6 (т. е. двоичный номер этого разряда) передается во вспомогательный регистр 2. После завершения п циклов счетчика б на шинах 9 устанавливается информация, обеспечивающая поочередное подключение первым коммутатором / и дешифратором 3 выходов вспомогательного регистра 2 к требуемым разрядам регистра 4 кода неисправности. По командам с выходов 12 формирователей микрокоманд состояние регистра 2 поразрядно записывается на требуемое место регистра 4, той его части, которая не связана со входами второго коммутатора 5 (в последней подпрограмме теста запись возможна и в другую часть). Таким .образом, результат сравнения на любой подпрограмме теста преобразуется из д-разрядного кода с постоянным весом п-1 в неизбыточный код разрядности log 2Положение разряда, с которого начинается код любой подпрограммы в регистре 4 и число разрядов вспомогательпого регистра 2, которые записываются в регистр 4, задается программой. Этим обеспечивается неизбыточное представление всего кода неисправности в регистре 4 при изменении п (п зависит от особенностей контролируемой схемы и используемого теста). Однако максимальное значение в пределах одной подпрограммы ограничено числом разрядов регистра 4, связанных со вторым коммутатором 5.

Если Р - число подпрограмм в тесте, то экономия Q в числе разрядов регистра кода неисправности при одинаковом я для всех подпрограмм составляет Q(P-I) (п-log 2).

По синхронизирующему сигналу, воздействующему в каждом цикле счетчика 6 на вход элемента «И J7, в триггер 13 записывается инверсия состояния выхода второго коммутатора 5. Конечное состояние Ф (после п циклов счетчика 6) этого триггера определяп

ется формулой ф f Dj.

Иными словами он окажется в состоянии «1, если реакция контролируемой схемы за к тактов равна хотя бы одной из п эталонных реакций. Указанный синхронизирующий сигнал подается одновременно на элемент «И 18 триггера М. При этом триггер 14 окажется в состоянии «О, если равеиство обнаружено более чем для одной эталонной реакции. Отличие |Состоя;Ния триггеров 13 и 14 от «1 будет обнаружено при подаче сигнала на элемент «И 15 и вызовет останов программы.

Предмет изобретения

1. Устройство для кодирования результатов программного контроля, содержащее регистр кода неисправности и дешифратор, отличающееся тем, что, с целью сжатия информации и расширения логических возможностей

устройства, оно содержит коммутаторы, счетчик, вспомогательный регистр и схему нрерывания нрограммы,,.причем входы первого коммутатора связаны;С вь1}{одом вспомогательио|о регистра ;И 1}нфорк1ационными шинами,

. .|ыход.., э-цого-..ко.мутатора через дешифратор г1рД{Уючен.; к. реристру кода неисправности, вкфды в.тррого коммутатора соединены со счетчиком и вспомогательным регистром, связанными между собой, а также с частью выходов регистра кода неисправности, выход

, данного коммутатора подключен к вспомогательному регистру и схеме прерывания программы.

2. Устройство по п. 1, отличающееся тем, что, с целью сокращения оборудования, схема прерывания программы содержит триггеры, логические элементы и элемент задержки,

причем единичный вход одного из триггеров через элемент «ИЛИ, связанный с двумя элементами «И, нодключен к инвертору; единичный выход этого триггера подсоединен непосредственно и через элемент задержки

ко входам элементов «И, вход одного из которых подключен к инвертору, выход этого элемента связан с нулевым входом второго трИггера, единичный выход которого подсоединен -к элементу «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

Огпв

риг.2

Даты

1969-01-01—Публикация