Изобретение относится к вычислительной технике и может быть использовано нри построении буферных заноминающих устройств.

Цель изобретения - новышение быстродействия устройства.

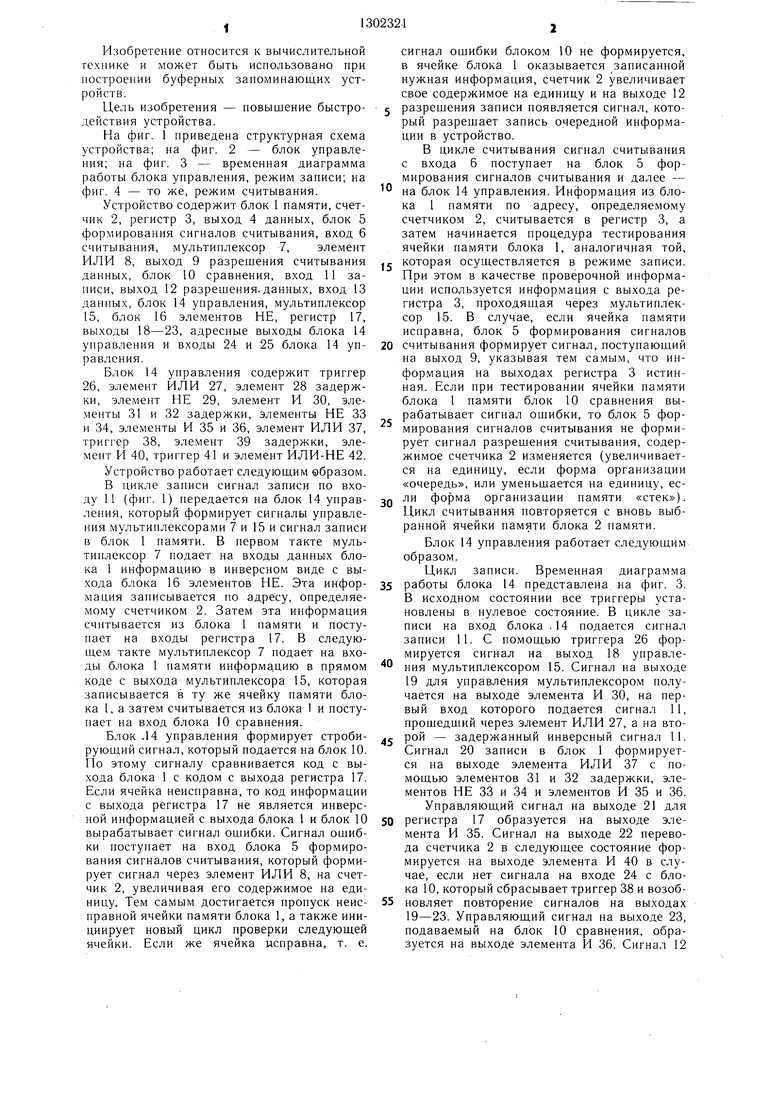

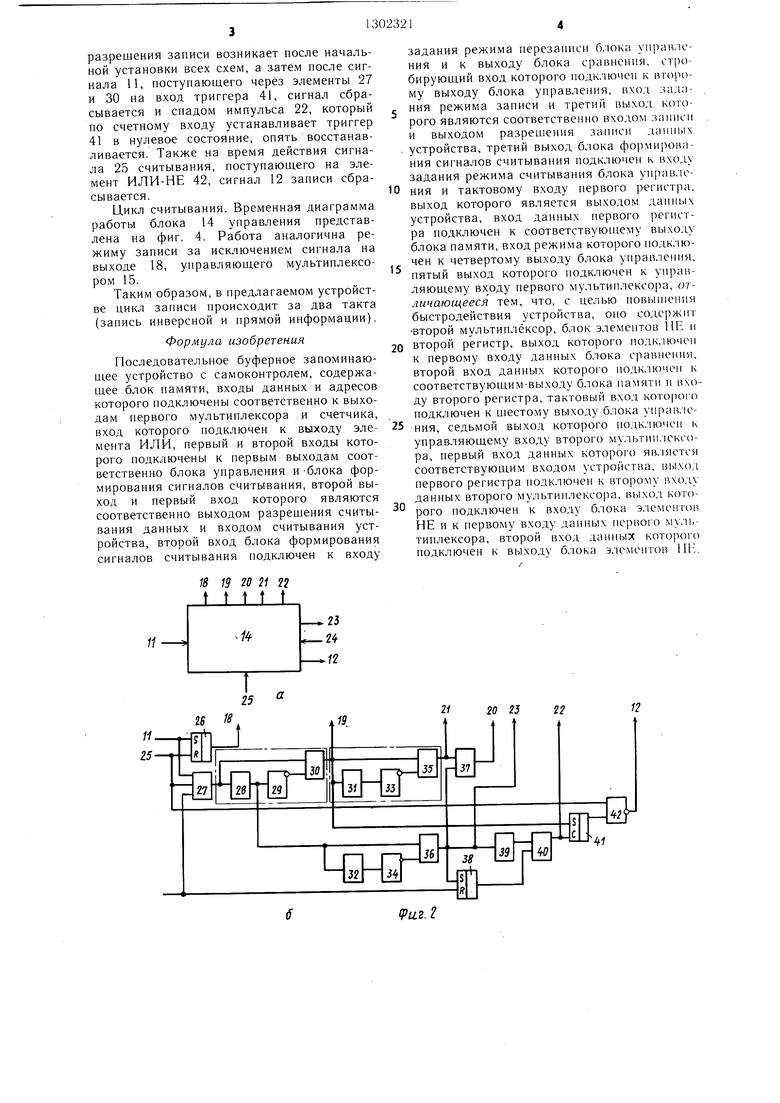

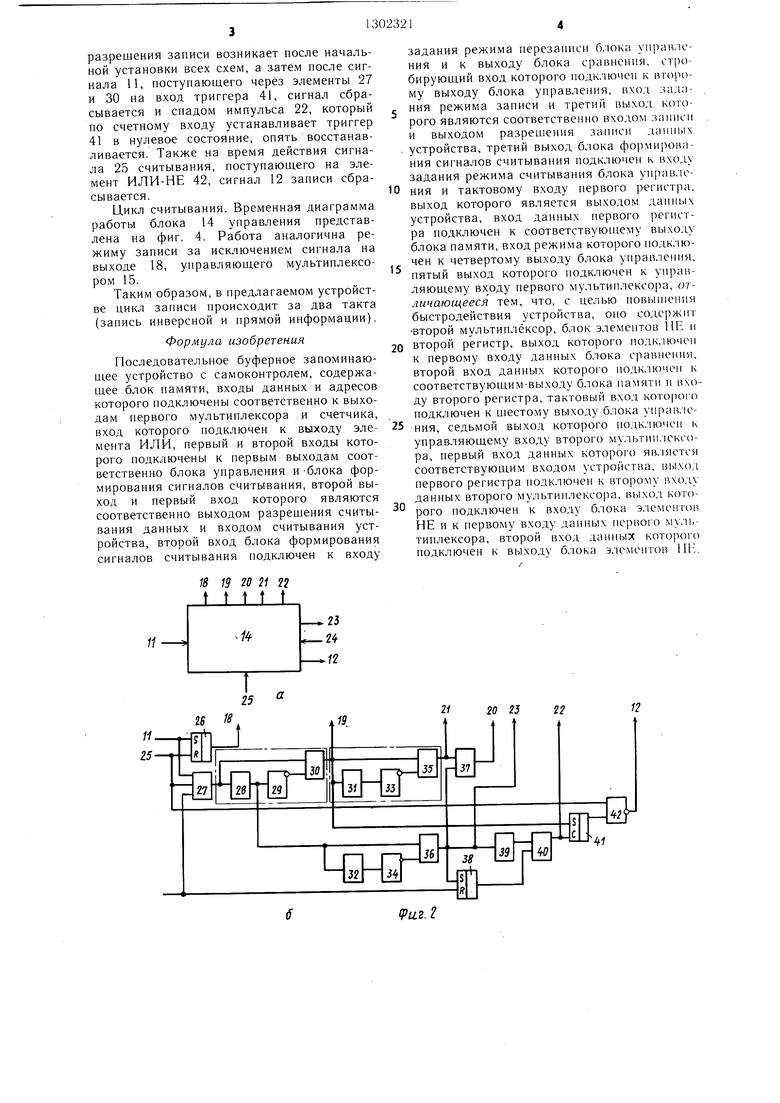

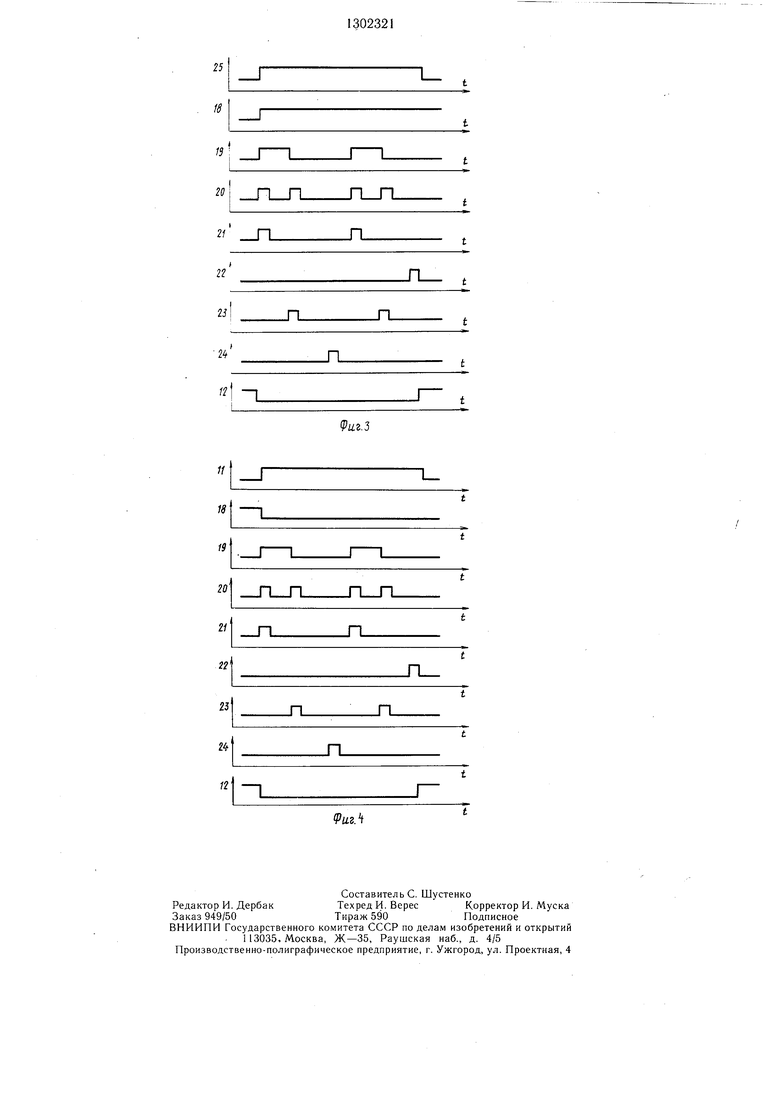

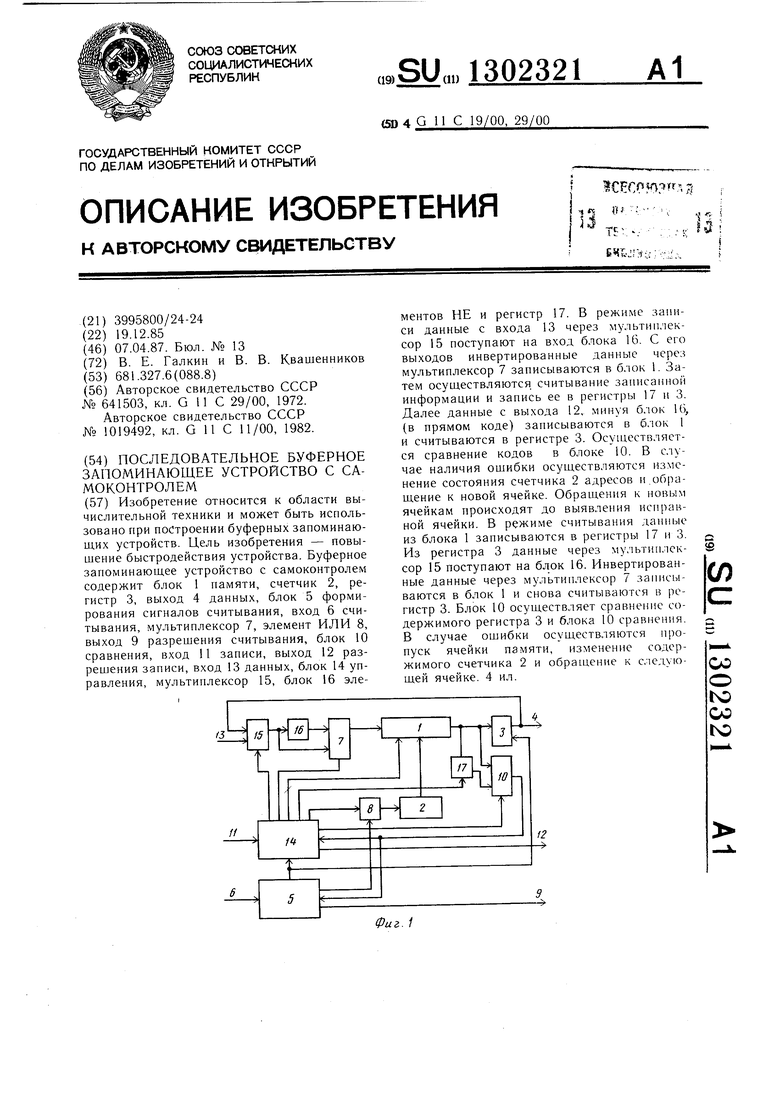

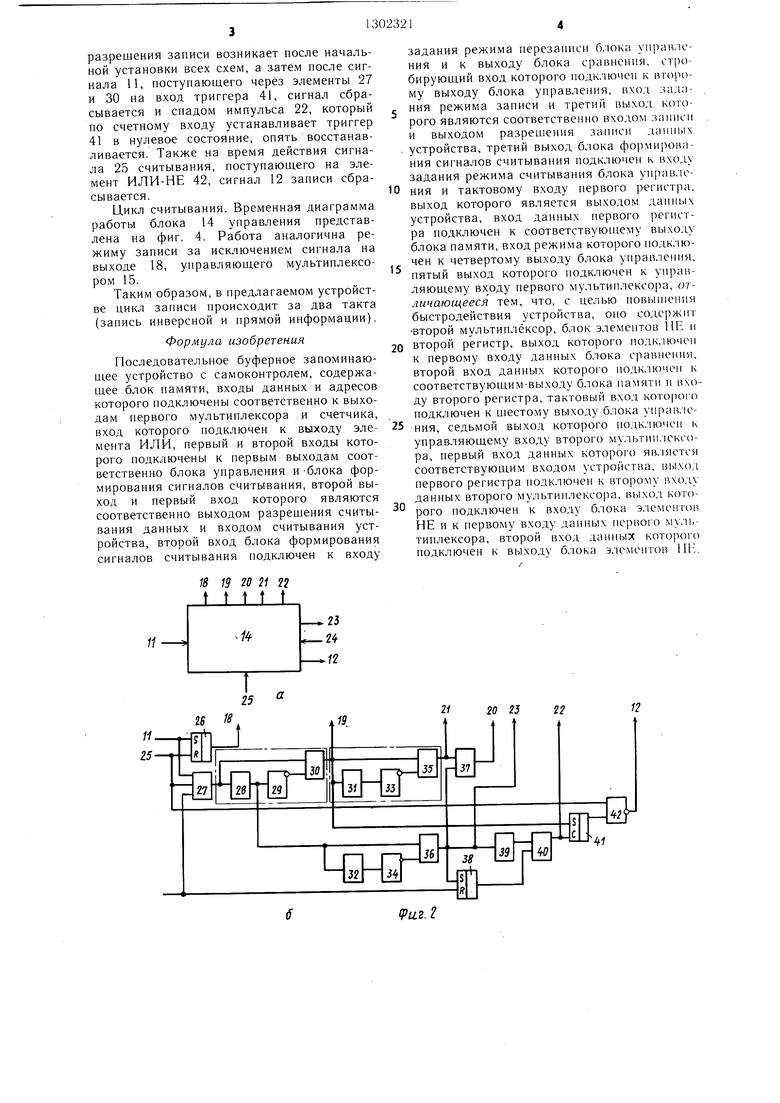

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - блок управления; на фиг. 3 - временная диаграмма работы блока управления, режим записи; на фиг. 4 - то же, режим считывания.

Устройство содержит блок 1 памяти, счетчик 2, регистр 3, выход 4 данных, блок 5 формирования сигналов считывания, вход 6 считывания, мультиплексор 7, элемент ИЛИ 8, выход 9 разрешения считывания данных, блок 10 сравнения, вход 11 записи, выход 12 разрешения.данных, вход 13 данных, блок 14 управления, мультиплексор 15, блок 16 элементов НЕ, регистр 17, выходы 18-23, адресные выходы блока 14 управления и входы 24 и 25 блока 14 управления.

Блок 14 управления содержит триггер 26, элемент ИЛИ 27, элемент 28 задержки, элемент НЕ 29, элемент И 30, элементы 31 и 32 задержки, элементы НЕ 33 и 34, элементы И 35 и 36, элемент ИЛИ 37, триггер 38, элемент 39 задержки, элемент И 40, триггер 41 и элемент ИЛИ-НЕ 42.

Устройство работает следуюшим ебразом.

В цикле записи сигнал записи по входу 11 (фиг. 1) передается на блок 14 управления, который формирует сигналы управления мультиплексорами 7 и 15 и сигнал записи в блок 1 памяти. В первом такте мультиплексор 7 подает на входы данных блока 1 информацию в инверсном виде с выхода блока 16 элементов НЕ. Эта информация занисывается но адресу, определяемому счетчиком 2. Затем эта информация считывается из блока 1 памяти и поступает на входы регистра 17. В следую- шем такте мультиплексор 7 подает на входы блока 1 памяти информацию в прямом коде с выхода мультиплексора 15, которая записывается в ту же ячейку памяти блока 1, а затем считывается из блока 1 и посту- 1ает на вход блока 10 сравнения.

Блок .14 управления формирует строби- рующий сигнал, который подается на блок 10. Но этому сигналу сравнивается код с выхода блока 1 с кодом с выхода регистра 17. Если ячейка неисправна, то код информации с выхода регистра 17 не является инверсной информацией с выхода блока 1 и блок 10 вырабатывает сигнал ошибки. Сигнал ошибки поступает на вход блока 5 формирования сигналов считывания, который формирует сигнал через элемент ИЛИ 8, на счетчик 2, увеличивая его содержимое на единицу. Тем самым достигается пропуск неисправной ячейки памяти блока 1, а также инициирует новый цикл проверки следующей ячейки. Если же ячейка исправна, т. е.

сигнал ошибки блоком 10 не формируется, в ячейке блока 1 оказывается записанной нужная информация, счетчик 2 увеличивает свое содержимое на единицу и на выходе 12

разрешения записи появляется сигнал, который разрешает запись очередной информации в устройство.

В цикле считывания сигнал считывания с входа 6 поступает на блок 5 формирования сигналов считывания и далее -

на блок 14 управления. Информация из блока 1 памяти по адресу, определяемому счетчиком 2, считывается в регистр 3, а затем начинается процедура тестирования ячейки памяти блока 1, аналогичная той,

- которая осуществляется в режиме записи. Нри этом в качестве проверочной информации используется информация с выхода регистра 3, проходящая через мультиплексор 15. В случае, если ячейка памяти исправна, блок 5 формирования сигналов

0 считывания формирует сигнал, поступающий на выход 9, указывая тем самым, что информация на выходах регистра 3 истинная. Если при тестировании ячейки памяти блока 1 памяти блок 10 сравнения вырабатывает сигнал ошибки, то блок 5 формирования сигналов считывания не формирует сигнал разрешения считывания, содержимое счетчика 2 изменяется (увеличивается на единицу, если форма организации «очередь, или уменьшается на единицу, есQ ли форма организации памяти «стек). Цикл считывания повторяется с вновь выбранной ячейки памяти блока 2 памяти.

Блок 14 управления работает следующим образом.

Цикл записи. Временная диаграмма

работы блока 14 представлена на фиг. 3. В исходном состоянии все триггеры установлены в нулевое состояние. В цикле записи на вход блока , 14 подается сигнал записи 11. С помощью триггера 26 формируется сигнал на выход 18 управле ния мультиплексором 15. Сигнал на выходе 19 для управления мультиплексором получается на выходе элемента И 30, на первый вход которого подается сигнал 11, прошедший через элемент ИЛИ 27, а на вто5 рой - задержанный инверсный сигнал 11. Сигнал 20 записи в блок I формируется на выходе элемента ИЛИ 37 с помощью элементов 31 и 32 задержки, элементов НЕ 33 и 34 и элементов И 35 и 36. Управляющий сигнал на выходе 21 для

0 регистра 17 образуется на выходе элемента И 35. Сигнал на выходе 22 перевода счетчика 2 в следующее состояние формируется на выходе элемента И 40 в случае, если нет сигнала на входе 24 с блока 10, который сбрасывает триггер 38 и возоб5 новляет повторение сигналов на выходах 19-23. Управляющий сигнал на выходе 23, подаваемый на блок 10 сравнения, образуется на выходе элемента И 36. Сигнал 12

разрешения записи возникает после начальной установки всех схем, а затем после сигнала 11, поступающего через элементы 27 и 30 на вход триггера 41, сигнал сбрасывается и спадом импульса 22, который по счетному входу устанавливает триггер 41 в нулевое состояние, опять восстанавливается. Также на время действия сигна- ,ча 25 считывания, поступающего на элемент ИЛИ-НЕ 42, сигнал 12 записи сбрасывается.

Цикл считывания. Временная диаграмма работы блока 14 управления представлена на фиг. 4. Работа аналогична режиму записи за исключением сигнала на выходе 18, управляющего мультиплексором 15.

Таким образом, в предлагаемом устройстве цикл записи происходит за два такта (запись инверсной и прямой информации).

Формула изобретения

Последовательное буферное запоминаю- Hiee устройство с самоконтролем, содержащее блок памяти, входы данных и адресов которого подключены соответственно к выходам первого мультиплексора и счетчика, вход которого подключен к выходу элемента ИЛИ, первый и второй входы которого подключены к первым выходам соответственно блока управления и-блока формирования сигналов считывания, второй выход и первый вход которого являются соответственно выходом разрещения считывания данных и входом считывания устройства, второй вход блока формирования сигналов считывания подключен к входу

11

.23 .24 12

задания режима аерезаннси блока управления и к выходу блока сравнения, стро- бирующий вход которого подключен к второму выходу блока управления, вход :ui.i;i- ния режима записи и третий выход которого являются соответственно входом записи и выходом разрешения записи данных устройства, третий выход блока формирования сигналов считывания подключен к входу задания режима считывания блока управления и тактовому входу первого регистра, выход которого является выходом данных устройства, вход данных нервого регистра подключен к соответствую1нему выходу блока памяти, вход режима которого подключен к четвертому выходу блока управления, пятый выход которого юдключен к унрав- ляющему входу нервого мультиплексора, ог- личающееся тем, что, с целью новышення быстродействия устройства, оно содержит второй мультиплексор, блок элементов 11Е н второй регистр, выход которого нодключен к первому входу данных блока сравнения, второй вход данных которого нодключен к соответствующим-выходу блока памяти и входу второго регистра, тактовый вход которого подключен к шестому выходу блока унран. ю- ния, седьмой выход которого нодк.чючен к управляющему входу второго мультиплексора, первый вход данных которого яв.пяется соответствующим входом устройства, выход первого регистра подключен к второму входу данных второго мультинлексора, выход которого подключен к входу блока элеменгов НЕ и к первому входу данных lepBoro мул1, типлексора, второй вход данных которого подключен к выходу блока элементов 11Н.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1019492A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1987 |

|

SU1444800A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении буферных запоминающих устройств. Цель изобретения - повышение быстродействия устройства. Буферное запоминающее устройство с самоконтролем содержит блок 1 памяти, счетчик 2, регистр 3, выход 4 данных, блок 5 формирования сигналов считывания, вход 6 считывания, мультиплексор 7, элемент ИЛИ 8, выход 9 разрешения считывания, блок 10 сравнения, вход И записи, выход 12 разрешения записи, вход 13 данных, блок 14 управления, мультиплексор 15, блок 16 элементов НЕ и регистр 17. В режиме записи данные с входа 13 через мультиплексор 15 поступают на вход блока 16. С его выходов инвертированные данные через мультиплексор 7 записываются в блок 1. Затем осуществляются, считывание записанной информации и запись ее в регистры 17 и 3. Далее данные с выхода 12, минуя блок 16, (в прямом коде) записываются в блок 1 и считываются в регистре 3. Осуществляется сравнение кодов в блоке 10. В случае наличия ошибки осуществляются изменение состояния счетчика 2 адресов и обращение к новой ячейке. Обрап ения к новым ячейкам происходят до выявления исправной ячейки. В режиме считывания данные из блока 1 записываются в регистры 17 и 3. Из регистра 3 данные через мультиплексор 15 поступают на блок 16. Инвертированные данные через мультиплексор 7 защк ы- ваются в блок 1 и снова считываются в регистр 3. Блок 10 осуществляет сравнение содержимого регистра 3 и блока 10 сравне1П1я. В случае ошибки осуществляются пропуск ячейки памяти, изменение содержимого счетчика 2 и обращение к следующей ячейке. 4 ил. (О (Л оо о ю со Фиг. 1

IS 18

2i20 23

.

г/ П

2Л

24

П

20

21

гг.

22

23

п

24

гг

л

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU641503A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1019492A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-07—Публикация

1985-12-19—Подача