1

Изобретение относится к автомати ке и вычислительной технике и предназначено для построения кваэйстатических регистров с параллельно-последовательной записью информации.

Известны регистры сдвига на МДПтранзисторах, в которых синхронная запись в разрядные ячейки осуществляется только при отсутствии и-актовых сигti ал ОБ на соответствующих шинах

Наиболее близким по технической сути к изобретению является регистр сдвига, содержащий квазистатический триггер, состоящий из двух последовательно соединенных инверторов, вход и выход которых соединены с первым согласующим каскадом, вход первого инвертора связан через -второй согласующий каскад с входной шиной, а выход - с третьим согласующим каскадом, входы согласующих каскадов соответственно соединены с первыми управлякндими шинами, и третий инвертор 2.

Однако эти устройства не позволяют осуществить построение регистров сдвига с парс1ллельно-последовательной записью.

Цель изобретения - расширение области применения регистра.

Для этого устройство содержит три ключа, первый из которых соединен с третьим согласующим каскадом, третьим инвертором и вторым ключом,, входы первого и второго ключей соединены со вторыми управляющими шинами, третий ключ связан с выходом третьего инвертора и кодовой шиной.

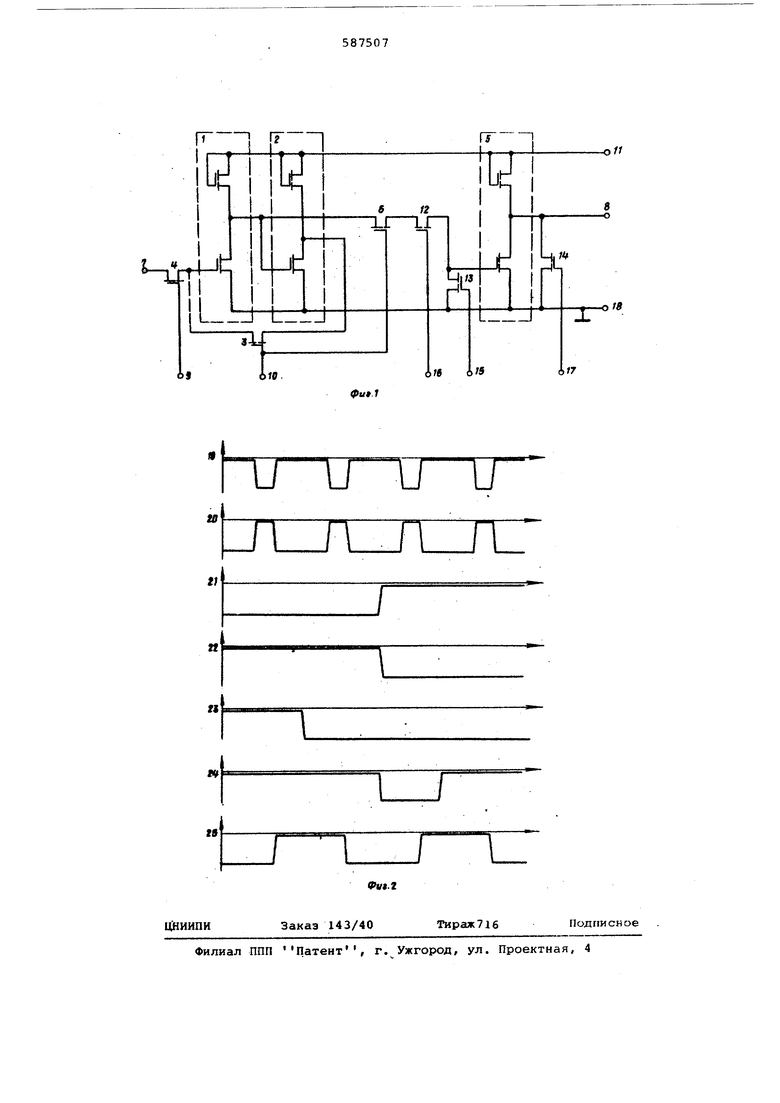

На фиг. 1 представлена принципиальная схема предложенного регистра на фиг. 2 - временные диаграммы его работы.

Регистр сдвига содержит квазистатический триггер с одной прерывающейся

связью, состоящий if3 двух последовательно соединенных инверторов 1 и 2 и первого согласующего каскада 3, второго согласующего каскада 4, третий инвертор 5, третий согласующий каскад

6, входную 7 ивыходную-8 шины, первые управляющие шины 9 и 10, соответственно, шину питания 11, ключи 12, 13 и 14, вторые управляющие шины 15 и 16, кодовую шину 17 и общую шину

питания 8.

Принцип работы регистра сдвига поясняется временными диаграммами напряжений и выходных сигналов для случая применения р-канальных МДП-транзисторов и питания схемы от источника отрицательного напряжения, где 19 и 20первые управляющие сигналы, 21 и 22 вторые управляющие сигналы, 23 - сигиал на входной шине 7, 24 - сигнал по кодовой шине 17 и 25 - сигнгш на выходной шине 8.

В режиме последовательной ааписи информации на шину 16 подается высокий .уровень отрицательного напряжения, ключ 12 в открытом состоянии, а на шины 15 и 17 - нулевой уровень напряжения, обеспечивающий запирание ключей 13 и. 14 .

С приходом первого управляющего сигнала на шины 9 и 10 согласующие каскады 3 и б закрываются. При этом разрывается одна перекрестная связь кваэистатического триггера и отключается вход третьего инвертора 5 от выхода первого инвертора 1, что обеспечивает на выходной шине 8 поддержание уровня напряжения, соответствующего состоянию ячейки до поступления тактовых сигналов, благодаря заряду, сохраняющемуся на входной паразитной емкости третьего инвертора 5; открыва ется второй согласукяций каскад 4, через который: сигнал, присутствующий на входной шине 7, поступает на вход инвертора 1. По окончании Первого управляющего сигнала закрывается второй согласующий каскад 4 и открываются, согласующие каскады 3 и б, что обеспечивает перекрестное соединение инвертора 1 и 2, образующее триггер, и подключение третьего инвертора 5 к выходу первого инвертора 1, При этом на выходной шине 8 устанавливается уровень напряжения, соответствующий новому логическому состоянию, записанному в ячейку во время действия тактовых сигналов.

В режиме параллельной записи кода на шину 16 подается нулевой уровень напряжения, запирающий .ключ 12, а на шину 15 - сигнал разрешения записи кода (высокий уровень отрицательного напряжения), открывающий ключ 13. При этом вход инвертора 5 отключен от выхода инвертора 1 и через ключ 13 подключен к общей шине. Так как нижний транзистор третьего инвертора в этом случае будет заперт, то-уровень напряжения на выходной шине 8 будет определяться только состоянием ключа 14, который управляется сигналом По кодовой шине 17. Таким образом, независимо от

Состояния квазистатического триггера на выходной шине В ячейки устанавливается логический уровень, соответствующий инвертированному кодовому сигналу 24 на кодовой шине 17, который при поступлении тактовых сигналов переписывается в следующую ячейку.

Кодовый сигнал на шину 17 должен подаваться только при наличии на вторых управляющих шинах 16 и 15 инверсного и прямого сигналов разрешения адресного опроса. В режиме последовательного опроса «а кодовую шину 17 подается нулевой уровень напряжения, соответствующий логическому нулю.

На фиг. 2 первые два тактовых сигнала соответствуют режиму последовательной записи информации, а дв последних - режиму пар.аллельной записи информации в ячейку.

Для изготовления регистра с параллельно-последовательной записью информации на основе предлагаемой ячейки можно использовать, любую стандартную технологию МДП-структур с р-или п каналом.

Формула изобретения

Регистр сдвига, содержащий квазистатический триггер, состоящий из двух последовательно соединенных инверторов, вход и выход которых соединены с первым согласующим каскадом, вход первого инвертора связан через второй согласуюоЩй каскад с входной шиной, а выход с третьим согласующим каскадом, входрл : согласующих каскадов соответственно соединены с первыми управляющими шинами, и третий инвертор, отличающийс я тем, что, с целью расиирения области его применения, он содержит три ключа, первый из которых соединен с третьим согласующим каскадом, третьим .инвертором и BToptiM ключом, входы первого и второго ключей соединены со вторыми управляющими-шинами, третий ключ связан с выходом третьего инвертора и кодовой шиной.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство №342223 кл. Q 11 С 19/28, 06.72.

2.Патент США №3406346, кл. 328-37, 20.04.66.

rr-п F-I

ГГ

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти для регистра сдвига | 1979 |

|

SU832600A1 |

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1285392A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ И МОБИЛЬНЫЙ ТЕРМИНАЛ | 2009 |

|

RU2447517C1 |

| Многоканальный коммутатор | 1984 |

|

SU1220123A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

Авторы

Даты

1978-01-05—Публикация

1976-09-28—Подача