(54) РЕЗЕРВИРОВАННОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

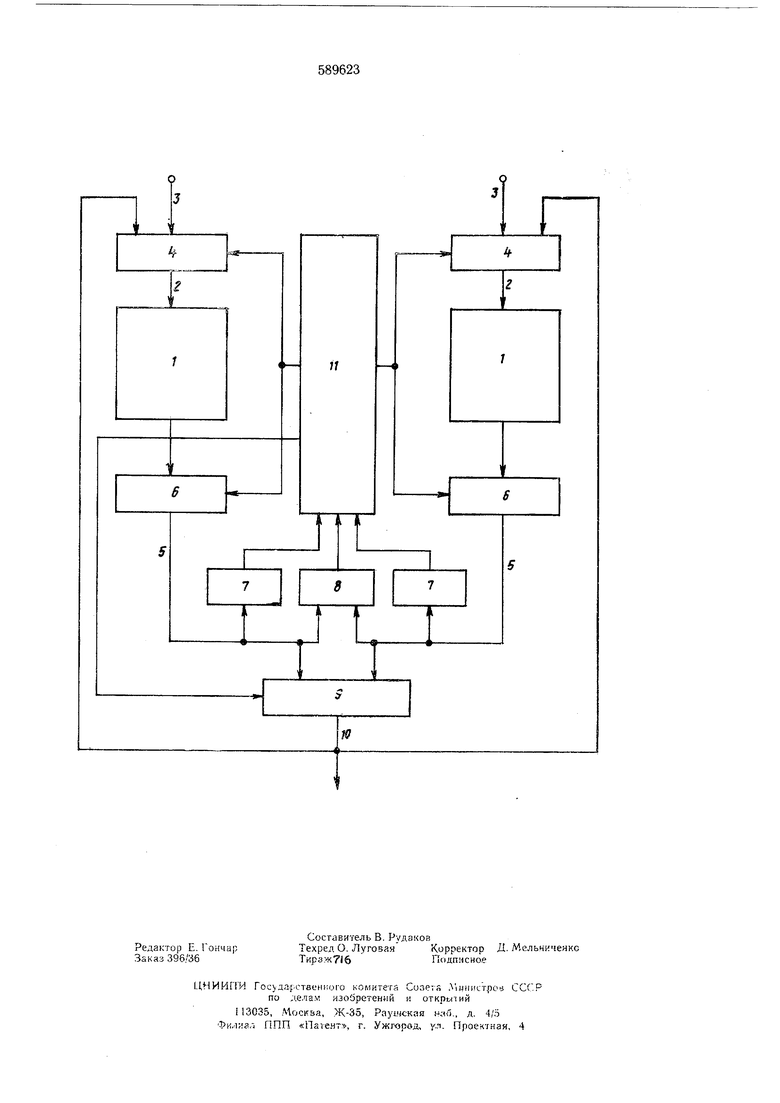

коммутаторы 4 подключены к соответствующим входам накопителей 1. Аналогично выходы накопителя 1 через выходные коммутаторы 6 подключены к выходам 5 этих коммутаторов. При считывании сигналы информационных слов проходят на блоки 7 свертки и блок 8 поразрядного сравнения. Если соответственный блок свертки не обнаруживает ошибки в считанном слове, то на его выходе вырабатывается информация об отсутствии ошибки и блок 11 выдает сигнал коммутатору 9 на пропуск на выход 10 информации из соответствуюш,его накопителя 1.

При возникновении в первом накопителе 1 (левый на чертеже) одиночной ошибки блок управления II разрешает пропуск на выход 10 информационного слова -с второго накопителя 1. При устойчивом повторении ошибки при считывании информации в одном и том же разряде из накопителей блок 11 запоминает номер отказавшего накопителя и номер отказавшего разряда. Номер отказавшего накопителя определяется при помоши блоков свертки 7, номер отказавшего разряда - при помощи блока 8 поразрядного сравнения. Блок 11 вырабатывает сигнал о переключении по которому соответствующий коммутатор 4 подключает входную шину отказавшего оазряда к входной шине контрольного разряда соответствующего накопителя 1. По этому же сигналу выходной коммутатор 6 неисправного накопителя 1 подключает шину контрольного разряда к выходной шине неисправного разряда. После переключения блок 11 осуществляет перезапись всей информации из исправного накопителя 1 в неисправный. В процессе перезаписи информация неисправного разря;,а записывается в разряд, где ранее хранилась контрольная информация. Одновременно отключается соответствующий блок свертки 7. В результате перезаписи в этом накопителе восстанавливается вся информация за исключением контрольного оазряда.

Если в процессе дальнейшей работы блок 8 опять обнаружит несовпадение разрядов в информационных словах, поступающих с обоих накопителей (произойдет еще один отказ), то

сигнал от блока свертки 7, связанный с вторым накопителем i там, где этот блок не был отключен, покажет, есть ли искажение информации во втором накопителе 1. Если такое искажение есть, то считается, что в первом накопителе 1 информация не искажена и блок 11 через выходной коммутатор 6 пропускает эту информацию на- выход 10 коммутатора 9. Если блок свертки 7 не отмечает искажения, то считается неискаженной информация второго накопителя, которая и передается на выход 10 коммутатора 9.

Таким образом, описанное устройство позволяет при простом потоке отказов исправлять две ошибки. При использовании не двух, а большего числа (Р) накопителей в таком

устройстве исправляется 2(Р-1) ошибки, что в два раза превышает кратность ошибок, исправляемых в обычных Р-канальных устройствах с контролем в каждом канале.

Формула изобретения

Резервированное оперативное запоминающее устройство, содержащее накопители блок управления, подключенный к блокам свертки по модулю два, блоку поразрядного сравнения и коммутатору, отличающееся теМ) что, с целью повышения надежности устройства, оно содержит входные и выходные ко.ммутаторы, управляющие входы которых подключены к вы.ходам блока управления информационные входы входных коммутаторов соединены соответственно с входами устройства и выходом коммутатора, а выходы - с входами соответствующих накопителей входы выходных ко.ммутаторов подключены соответственно к выхода.м накопителей, а выходы - к входам соответствующих блоков свертки по модулю два и входам блока поразрядного сравнения и коммутатора. Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР 439020, кл G 11 С 29/00, 1972.

0

2.Патент США № 3685015, кл. 340-141.1, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1982 |

|

SU1061175A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1037348A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1381597A1 |

| Запоминающее устройство с коррекцией модульных ошибок | 1989 |

|

SU1633461A1 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Устройство для контроля блоков памяти | 1979 |

|

SU771733A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

Авторы

Даты

1978-01-25—Публикация

1975-10-08—Подача