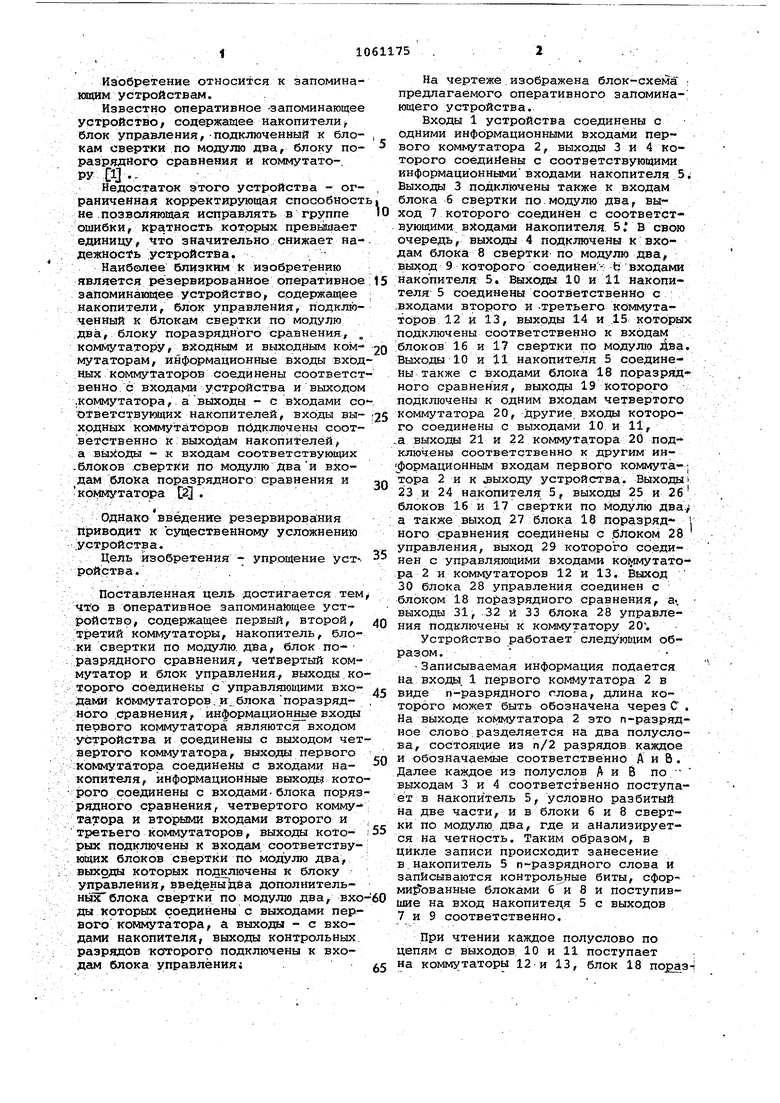

Изобретение относится к запоминающим устройствам. : Известно оперативное -запоминающее устройство/ содержащее накопители, блок управления/-подключенный к блокам свертки по модулю два, блоку по разрядйого сравнения и коммутато-. ру тНедостаток этого устройства - ограниченная корректирующая способност не позволяющая исправлять в группе ошибки, кратность которых превышает единицу, что значительно снижает надежность устройства. Наиболее близким к изобретению является резервированное оперативное запоминающее устройство, содержащее накопители, блок управления, подключенный к блокам свертки по модулю два, блоку поразрядного сравнения, „ коммутатору г входным и выходным коммутаторам, информационные входы вход ных коммутаторов соединены соответст венно:с входами устройства и выходом .коммутатора,. а выходы - с входами со ОТветствующих накопителей, входы выхрдных коммутаторов пс5дключены соответственно К выходам накопителей, а выводы - к входам соответствующих .блоков .свертки по модулю дваи блока поразрядного сравнения и коммутатора 121. ; Одйако введение резервирования приводит к существенному усложнению .устройства. Цель изобретения - упрощение Уcт ройства. Поставленная цель достигается тем в оперативное запоминающее устройство, содержащее первый, второй, третий коммутаторы, накопитель, блоки свертки по модулю, два, блок по- разрядного сравнения, четвертый коммутатор и блок управления., выходы. ко торого соединены с управляющими вхо- дами коммутаторов, и..блока поразрядного .сравнения, информационные входы первого коммутатора являются входом устройства и ооедийены с выходом чет вертого коммутатора, выходы первого :коммутатора соединены с входам накопителя, информационные выходи кото рого соединены с входами-блока поряз рядного сравнения, четвертого коммутатора и вторыми входами второго и третьего коммутаторов, выходы которых подключены к входам соответствующих блоков CBepiTKH по МОДУ.ЛЮ два, выходы которых подключены к блоку управлейий, ввёДе|шЬйа дополнительны1Гблока свертки по модулю два, вхо ды которых соединены с выходами первого коммутатора, а выходы - с входами накопителя, выходы контрольных. разрядов которого подключены к вхоДс1М блока управления; На чертеже.изображена блок-схема ; предлагаемого оперативного запоминающего устройства. Входы 1 устройства соединены с одними информационными входами первого коммутатора 2, выходы 3 и 4 которого соединены с соответствующими информационными входами накопителя 5 Выходы 3 подключены также к входам блока 6 свертки по.модулю два, выход 7 которого соединен с соответствующими входами Накопителя 5 . В свою очередь, выходы 4 подключены к;входам блока 8 свертки по МОДУ.ШО Два, выход 9 которого соединен:-: Ь входами накопителя 5. Выходы 10 и 11 накопителя 5 соединены соответственно с ;входами второго и-третьего коммутатЪррв 12 и 13, выходы 14 и .15 которых подключены соответственно к входам блоков 16 и 17 свертки по модулю д|ва. ВыХодыЮ и 11 накопителя 5 соединены также с входами блока 18 поразрядного орав нения, выходы 19 которого подключены к одним входам четвертого коммутатора 20, другие входы которого соединены с выходами 10 и 11, :а выхода 21 и 22 коммутатора 20 подключены соответственно к другим ин формационным входам первого крммута-: ора 2 VI к выходу устройства. Выходы 23 и 24 накопителя. 5, выходы 25 и 2б блоков 16 и 17 свертки по модулю два.; а также выход 27 ;блока 18 поразряд- I ного сравнения соединены с .блоком 28 управления, выход 29 которого со.единен с управляющими входами ко: шутатора 2 и коммутаторов 12 и 13. Выход 30 блока 28 управления соединен с блоком 18 по азрядного сравнения, а. выходы 31, 32 и 33 блока 28 управления подключены к коммутатору 20. Устройство работает следующим образом. ; -Записываемая информация подается На входы. 1 первого коммутатора 2 в виде п-разрядного г;лова, длина которого может быть обозначена через С . На выходе ко1у1мутатора 2 зто п-разрядное слово разделяется на два полуслова, состоящие из п/2 разрядов каждое и обозначаемые соответственно А и В. Далее каждое из полуслов А и В по выходам 3 и 4 соответственно поступает в накопитель 5, условно разбитый на две части, и в блоки б и 8 свертки по модулю, два, где и анализируется на четность. Таким образом, в цикле записи происходит занесение в накопитель 5 п-разрядного слова и записываются контрольные биты, сфор ми ованные блоками б и 8 и поступившие на вход накопитедя 5 с выходов 7 и 9 соответственно. При чтении каждое полуслово по цепям с выходов. 10 и 11 поступает на коммутаторы 12-и 13, блок 18 по аз-рядного сравнения и входы коммутатора 20,-По цепи с выхода 29 блока 2.8 управления поступает сигнал/ разрешающий прохождение считанной информации через коммутаторы 12 и 13 собт ветственно на выходы 14 и 15.Блоки 16 и 17 свертки осуществляют форми- рование контрольных битов, поступавющих затем по выходам 25 и 26 в блок 28 управления. Контрольные биты, поступающие с блоков 16 и 17, сравниваются в блоке 28 управления с контрольными битами, считанными из накопителя 5 по цепям с выходов 23 и 24. Блок управления осуществляет попарь ное сра.внение сигналов, поступивших по .цепям с выходов 123-25 и 24-26 Если по своей логической значимости они равны, то блЬк 28 управления по цепи с выхода 31 выдает сигнал, по которому считанная информации поступает на выход 22 устройства ,

Предположим, что в слове А при чтении произошел сбой, тогда при сравнении сигналов с выходов 23-25 и 24-26 в блоке управления последний вырабатывает сигнал на выходе 32, ПО которому запрещается выдача информации на выход 22 и разрешаетс я прохождение считанной информации через коммутатор 20 и на выход 21.Так как.сбой произошел в слове А , :а Олово В не искажено, то через коммутатор 20 и выход 21 слово в поЧзгупает на другие информационнее выxo;eii коммутатора 2, с выхода 3 которого слово В поступает параллельно на вход бЯока 6 свертки по модулю два и На вход первой части накопителя 5, где ранее записанное слово А заменяется на слово в . во второй части накопителя слово Б сохраняется. Блок 6 формирует контрольный бит, поступающий по цепи 5 выхо:да 7 на вход первой части накопите ля.5. После того как запись контрбЙ ного бита и слова Б в первой части накопителя 5 заканчивается, осуществляется считывание информации из обе. их частей накопителя.Теперь уже логические значения контрольных битов,

находящиеся в каждой из частей накопителя, совпадают, также как и записанные в них слова (слово 6 ).

Считываемая информация через коммутаторы 12 и 13 поступают на блоки

0 16 и 17 свертки по модулю два, с выходов 25 и 26 которых сформированные контрольные биты поступают на блок 28 управления, где сравнивается с контрольными битами, считанными из

5 накопителя 5 ITO цепям с выходов 23 и 24. Блок 28 управления сигналом по цепи с выхода 30 подключает блок 18 поразрядного сравнения, который осуществляет поразрядное сравнение слов В , поступивших из каждой части на0копителя 5. Поразрядное сравнение выявляет неисправный разряд первой Накопителя. Сигналы с выхода блока 1В по цепи с выхода 19 посту5 пают на вход коммутатора 20, на вход управления которого поступает сигнал с выхода 33 блока 28 управления. По этим сигналам в коммутаторе 20 осуществляется коррекция хранящейся в нем 11ё|рвоначальной искаженной ин0формации сЛова А , поскольку известны искаженный разряд и логическое ; значение искаженного разряда. .

Скорректированная информация с коммутатора 20 по цепи с выхода 21 ;поступает на перезапись в первую часть накопителя 5, после чего блок 28 управления по цепи с выхода 31 разрешает прохождение скорректирован40 ной информации на выход 22 устройства. В процессе перезапиОй скоррёк тированной информации, последняя записываетоя в разряд, где ранее хранилась контрольная информация.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное оперативное запоминащее устройство | 1975 |

|

SU589623A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1984 |

|

SU1215139A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1211811A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Устройство для обнаружения и локализации ошибок при передаче информации | 1982 |

|

SU1051541A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1991 |

|

SU1837364A1 |

ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО,,содержащее первый, второй, третий коммутаторы, накопитель, блоки свертки по модулю два, блок поразрядного сравнения, четвертый коммутатор и блок управления, выходы которого соединены с управляющими входами, коммутаторов и блока по-, разрядного сравнения,информационные входы первого коммутатора являются входом устройства и Соединены с выходом четвертого коммутатора, выходы первого коммутатора соединены с входами накопителя, информационные выходы которого соединены с входами блока поразрядного сравнения, четвертого коммутатора и вторыми входами второго и третьего коммутаторов,, выхода которых подключены к входам соответствующих блоков свертки по модулю два,, выхода которых подключены к блоку управления, отличающееся тем, что, с целью упрощения устройства, оно содержит два дополнительных блока свертки по модулю два, входы которых соединены с выходами первого коммутатора, а выходы - с входами накопителя, выхо(Л ды контрольных разрядов которого подключены к входам блока управления. о: - ел

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Полу генеративная топка для сжигания влажного торфа | 1921 |

|

SU368A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР | |||

| Кирпичная или каменная кладка с изоляционными прослойками | 1926 |

|

SU5896A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-12-15—Публикация

1982-08-04—Подача