со 00

ел

со

Изобретение относится к вычислительной технике и автоматике и может быть использовано при создании запоминающих устройств.

Цель изобретения - повышение надежности постоянного запоминающего устройства.

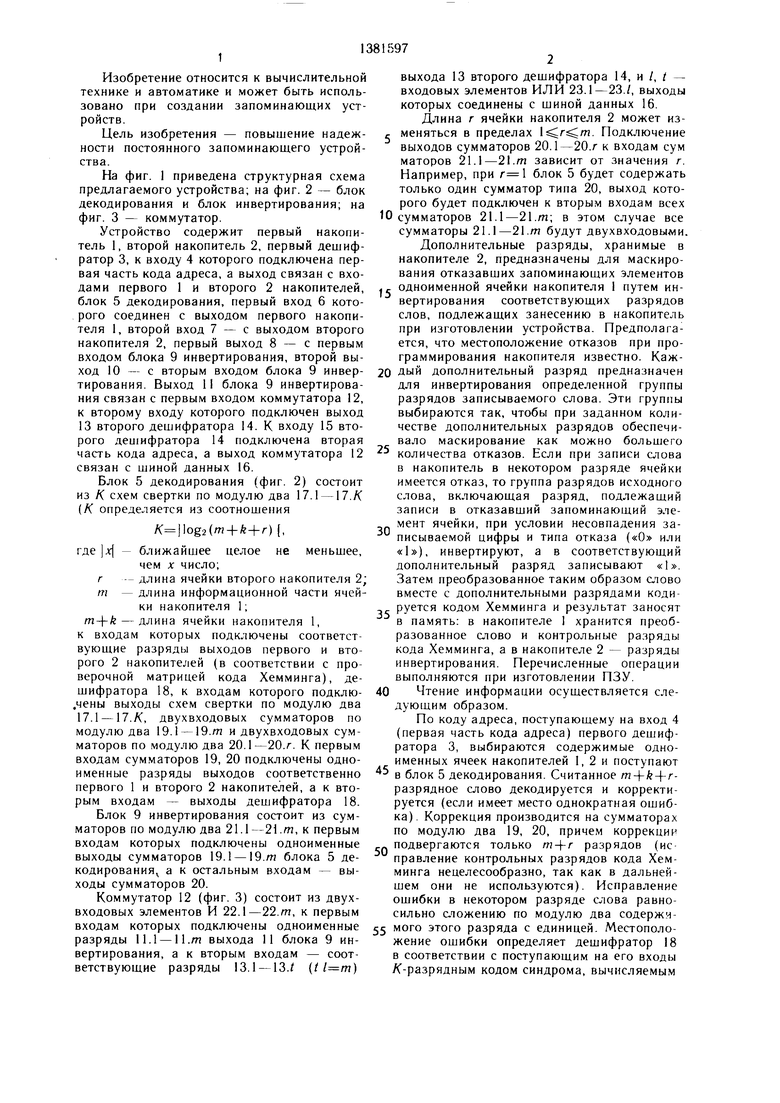

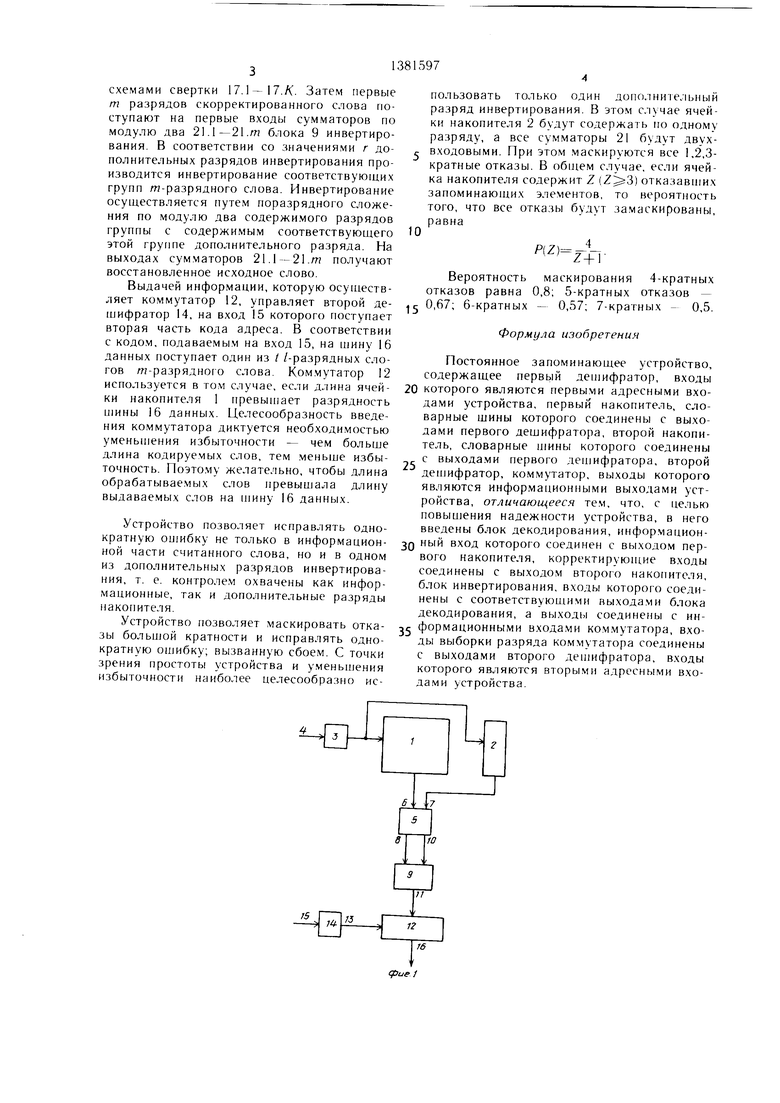

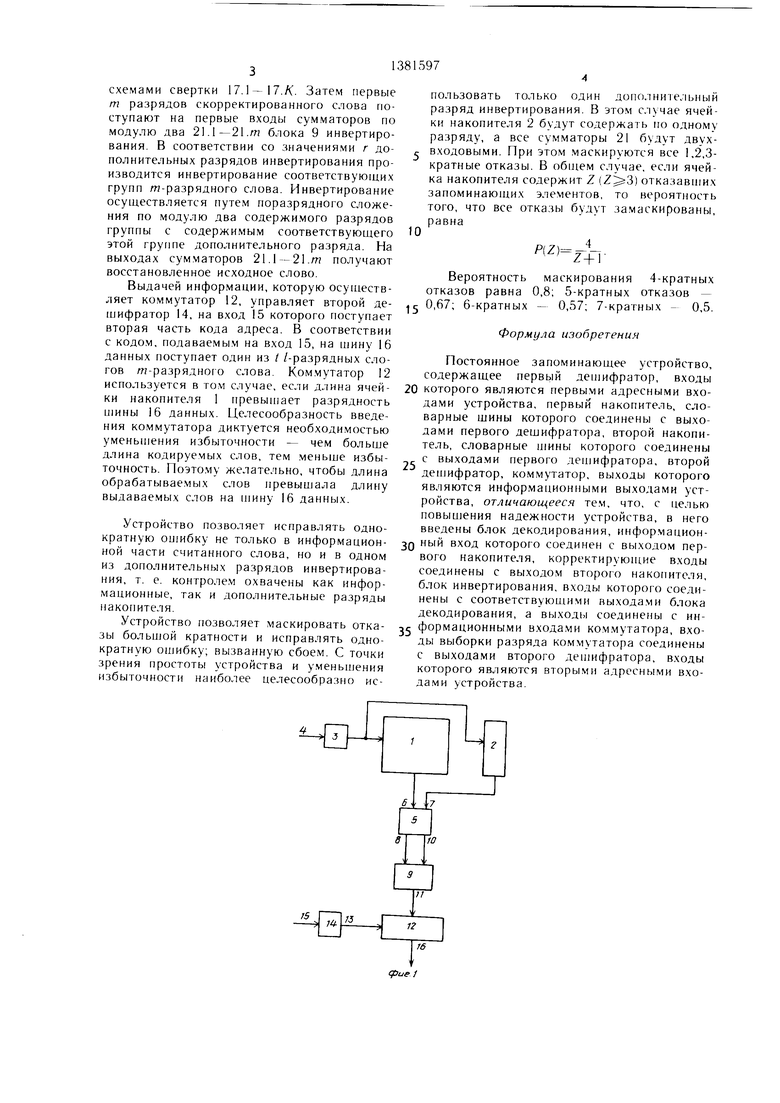

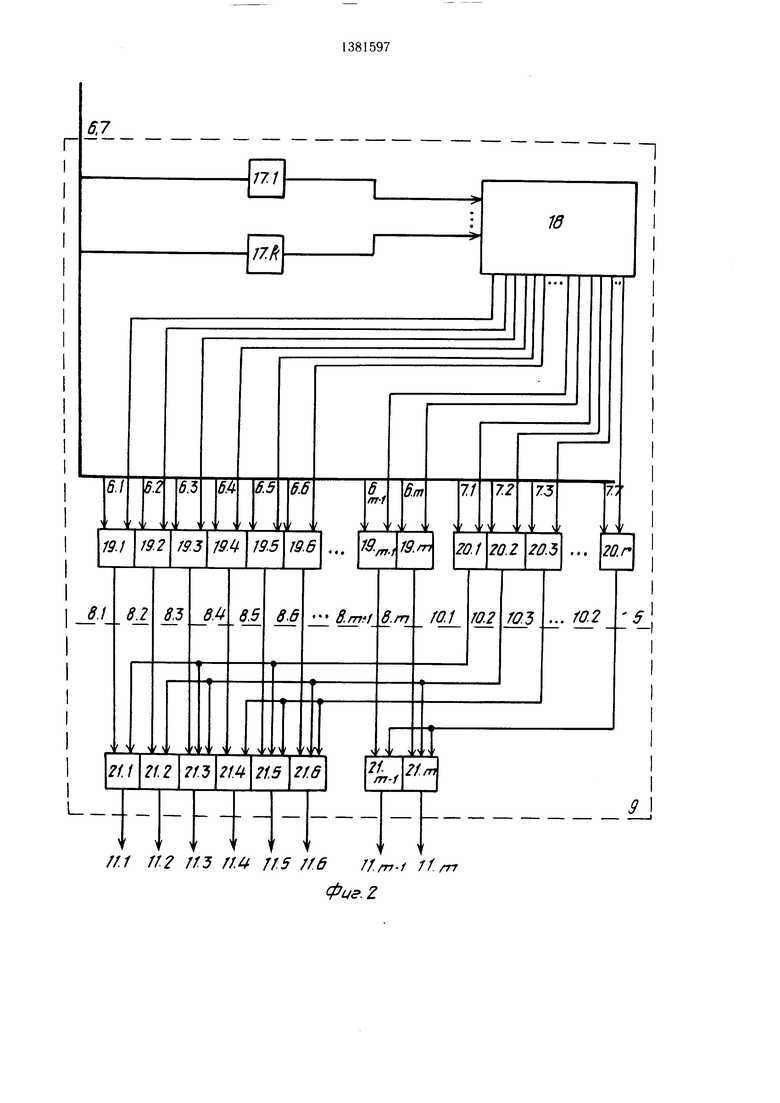

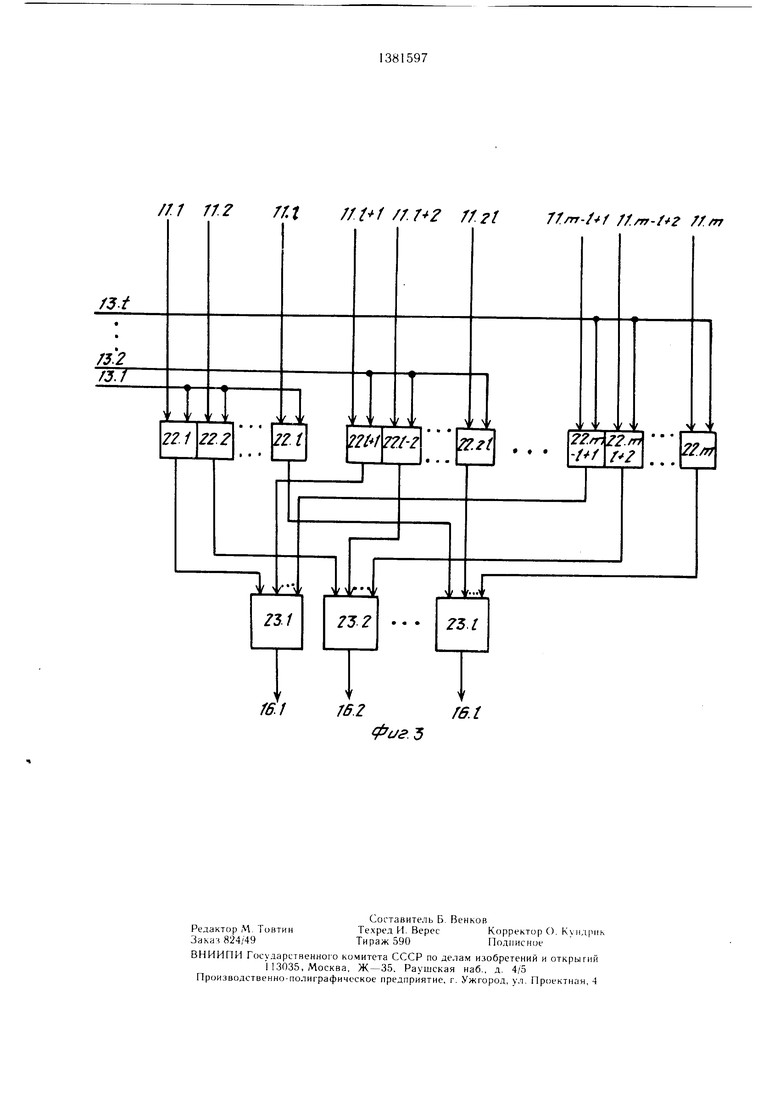

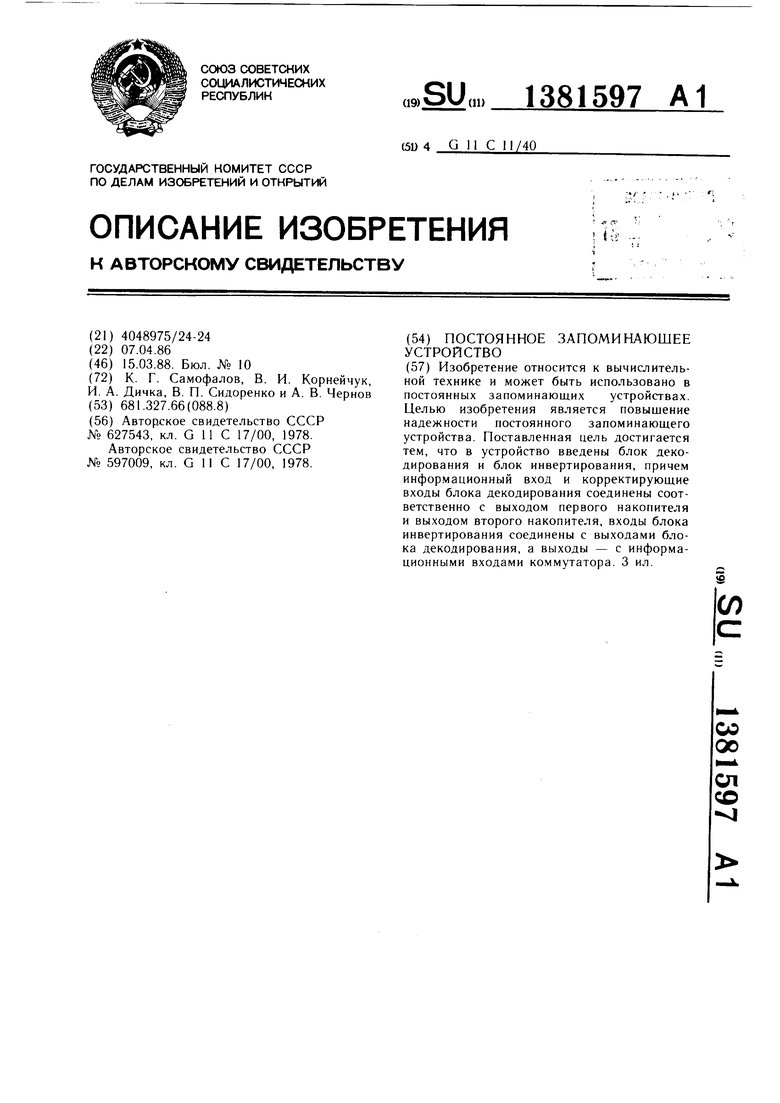

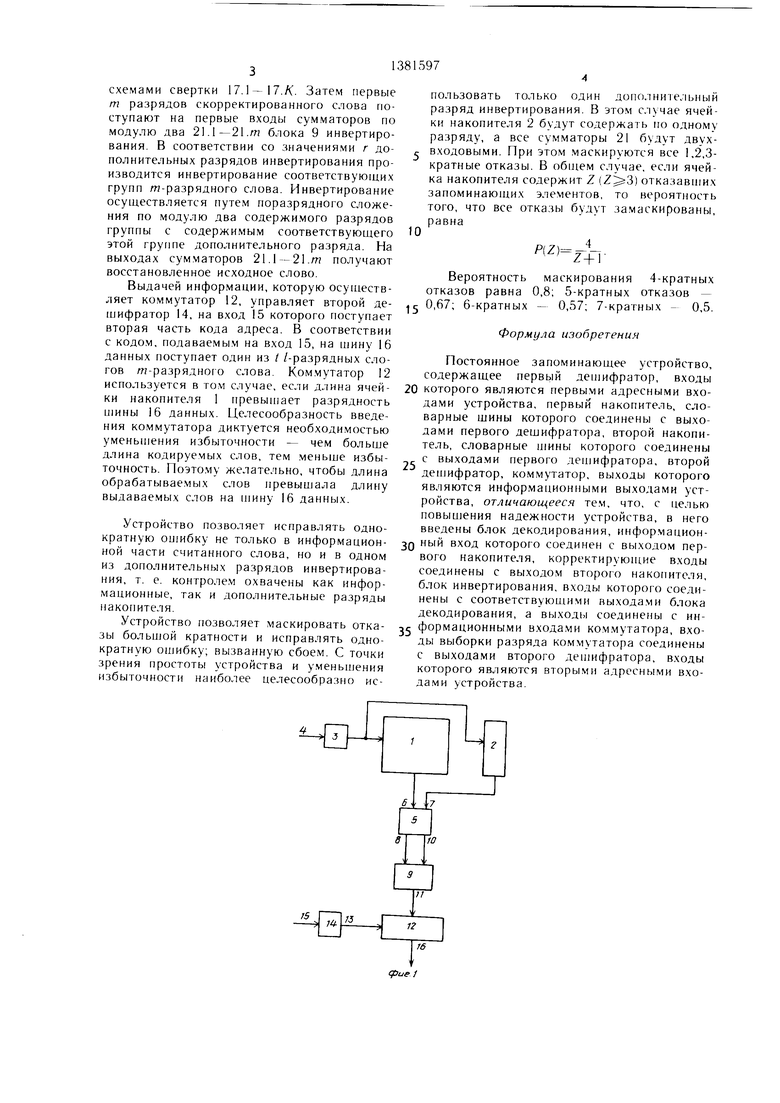

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - блок декодирования и блок инвертирования; на фиг. 3 - коммутатор.

Устройство содержит первый накопитель 1, второй накопитель 2, первый дешифратор 3, к входу 4 которого подключена первая часть кода адреса, а выход связан с входами первого 1 и второго 2 накопителей, блок 5 декодирования, первый вход 6 которого соединен с выходом первого накопителя 1, второй вход 7 - с выходом второго накопителя 2, первый выход 8 - с первым входом блока 9 инвертирования, второй выход 10 - с вторым входом блока 9 инвертирования. Выход 11 блока 9 инвертирования связан с первым входом коммутатора 12, к второму входу которого подключен выход 13 второго дешифратора 14. К входу 15 второго дешифратора 14 подключена вторая часть кода адреса, а выход коммутатора 12 связан с шиной данных 16.

Блок 5 декодирования (фиг. 2) состоит из К схем свертки по модулю два 17.1 - 17.Л (К определяется из соотношения

(m + fe+r),

где л| - ближайшее целое не меньшее, чем X число;

г - длина ячейки второго накопителя 2;

ш - длина информационной части ячейки накопителя 1;

ш-ffc - длина ячейки накопителя 1, к входам которых подключены соответствующие разряды выходов первого и второго 2 накопителей (в соответствии с проверочной матрицей кода Хемминга), дешифратора 18, к входам которого подклю- .чены выходы схем свертки по модулю два 17.1 -17.Л, двухвходовых сумматоров по модулю два 19.1 - 19.ш и двухвходовых сумматоров по модулю два 20.1-20.л. К первым входам сумматоров 19, 20 подключены одноименные разряды выходов соответственно первого 1 и второго 2 накопителей, а к вторым входам - выходы дешифратора 18.

Блок 9 инвертирования состоит из сумматоров по модулю два 21.1-21.от, к первым входам которых подключены одноименные выходы сумматоров 19.1 -19.т блока 5 декодирования,, а к остальным входам - выходы сумматоров 20.

Коммутатор 12 (фиг. 3) состоит из двухвходовых элементов И 22.1-22.ш, к первым входам которых подключены одноименные разряды 11.1 - .т выхода 11 блока 9 инвертирования, а к вторым входам - соответствующие разряды 13.1 - 13. (t )

5

5

выхода 13 второго дешифратора 14, и /, / - входовых элементов ИЛИ 23.1-23./, выходы которых соединены с шиной данных 16.

Длина г ячейки накопителя 2 может из- г меняться в пределах . Подключение выходов сумматоров 20.1-20.г к входам сум маторов 21.1-21.ш зависит от значения г. Например, при блок 5 будет содержать только один сумматор типа 20, выход которого будет подключен к вторым входам всех

10 сумматоров 21.1-21.ш; в этом случае все сумматоры 21.1-21.ш будут двухвходовыми. Дополнительные разряды, хранимые в накопителе 2, предназначены для маскирования отказавших запоминаюших элементов одноименной ячейки накопителя 1 путем инвертирования соответствующих разрядов слов, подлежащих занесению в накопитель при изготовлении устройства. Предполагается, что местоположение отказов при программирования накопителя известно. Каж0 ДЬ1Й дополнительный разряд предназначен для инвертирования определенной группы разрядов записываемого слова. Эти группы выбираются так, чтобы при заданном количестве дополнительных разрядов обеспечивало маскирование как можно большего количества отказов. Если при записи слова в накопитель в некотором разряде ячейки имеется отказ, то группа разрядов исходного слова, включающая разряд, подлежащий записи в отказавший запоминающий элемент ячейки, при условии несовпадения записываемой цифры и типа отказа («О или «1), инвертируют, а в соответствующий дополнительный разряд записывают «1. Затем преобразованное таким образом слово вместе с дополнительными разрядами кодируется кодом Хемминга и результат заносят в память: в накопителе 1 хранится преобразованное слово и контрольные разряды кода Хемминга, а в накопителе 2 - разряды инвертирования. Перечисленные операции выполняются при изготовлении ПЗУ.

Чтение информации осуществляется следующим образом.

По коду адреса, поступающему на вход 4 (первая часть кода адреса) первого дешифратора 3, выбираются содержимые одноименных ячеек накопителей I, 2 и поступают

- в блок 5 декодирования. Считанное разрядное слово декодируется и корректируется (если имеет место однократная ошибка). Коррекция производится на сумматорах по модулю два 19, 20, причем коррекции подвергаются только разрядов (ис правление контрольных разрядов кода Хемминга нецелесообразно, так как в дальнейшем они не используются). Исправление ошибки в некотором разряде равносильно сложению по модулю два содержи5 мого этого разряда с единицей. Местоположение ошибки определяет дешифратор 18 в соответствии с поступающим на его входы /(-разрядным кодом синдрома, вычисляемым

0

5

0

0

схемами свертки 17.1- 17./(. Затем первые т разрядов скорректированного слова поступают на первые входы сумматоров по модулю два 21.1-2.т блока 9 инвертирования. В соответствии со значениями г дополнительных разрядов инвертирования производится инвертирование соответствующих групп т-разрядного слова. Инвертирование осуществляется путем поразрядного сложения по модулю два содержи.мого разрядов группы с содержимым соответствующего этой группе дополнительного разряда. На выходах сумматоров 21.1 -21.m получают восстановленное исходное слово.

Выдачей информации, которую осун|ествпользовать только один дополнительный разряд инвертирования. В это.м случае ячейки накопителя 2 будут содержать по одному разряду, а все сумматоры 21 будут двух- г входовыми. При этом маскируются все 1,2,3- кратные отказы. В обп1ем случае, если ячейка накопителя содержит Z () отказавн1их запоминающих элементов, то вероятность того, что все отказы будут за.маскированы, равна

10

(

Вероятность маскирования 4-кратных отказов равна 0,8; 5-кратных отказов - ляет коммутатор 12, управляет второй де- 0,67; 6-кратных - 0,57; 7-кратных - 0,5. щифратор 14, на вход 15 которого поступает

вторая часть кода адреса. В соответствииФормула изобретения

с кодом, подаваемыми на вход 15, на щину 16 данных поступает один из / /-разрядных слогов /п-разрядног о слова. Ком.мутатор 12 используется в то.м случае, если длина ячейки накопителя I нревьпнает разрядность щины 16 данных. Целесообразность введения коммутатора диктуется необходимостью уменыпения избыточности - чем больще длина кодируемых слов, тем меньще избыточность. Поэтому желательно, чтобы длина обрабатываемых слов нревыщала длину выдаваемых слов на IHHHV 16 данных.

25

Постоянное запоминающее устройство, содержащее первый денжфратор, входы

20 которого являются первыми адресными входами устройства, первый накопитель, словарные шины которого соединены с выходами первого дешифратора, второй накопитель, словарные шины которого соединены с выходами первого дец ифратора, второй дешифратор, коммутатор, выходы которого являются информационными выходами устройства, отминающееся тем, что, с целью повышения надежности устройства, в него введены блок декодирования, инфор.мационУстройство позволяет исправлять однократную ошибку не только в информационной части считанного слова, но и в одном из дополнительных разрядов инвертирования, т. е. контролем охвачены как информационные, так и дополнительные разряды накопителя.

Устройство позволяет маскировать отказы большой кратности и исправлять однократную ошибку; вызванную сбоем. С точки зрения простоты устройства и уменьшения избыточности наиболее целесообразно использовать только один дополнительный разряд инвертирования. В это.м случае ячейки накопителя 2 будут содержать по одному разряду, а все сумматоры 21 будут двух- входовыми. При этом маскируются все 1,2,3- кратные отказы. В обп1ем случае, если ячейка накопителя содержит Z () отказавн1их запоминающих элементов, то вероятность того, что все отказы будут за.маскированы, равна

(

5

Постоянное запоминающее устройство, содержащее первый денжфратор, входы

0 которого являются первыми адресными входами устройства, первый накопитель, словарные шины которого соединены с выходами первого дешифратора, второй накопитель, словарные шины которого соединены с выходами первого дец ифратора, второй дешифратор, коммутатор, выходы которого являются информационными выходами устройства, отминающееся тем, что, с целью повышения надежности устройства, в него введены блок декодирования, инфор.мацион0 ный вход которого соединен с выходом первого накопителя, корректирующие входы соединены с выходом второго накопителя, блок инвертирования, входы которого соединены с соответствующими выходами блока декодирования, а выходы соединены с инг формационными входами коммутатора, входы выборки разряда коммутатора соединены с выходами второго дешифратора, входы которого являются вторыми адресными входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Запоминающее устройство | 1990 |

|

SU1794261A3 |

| Запоминающее устройство | 1990 |

|

SU1801227A3 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1152042A1 |

| Запоминающее устройство с коррекцией информации | 1982 |

|

SU1070610A1 |

| Запоминающее устройство | 1990 |

|

SU1753491A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1363312A1 |

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

Изобретение относится к вычислительной технике и может быть использовано в постоянных запоминающих устройствах. Целью изобретения является повышение надежности постоянного запоминающего устройства. Поставленная цель достигается тем, что в устройство введены блок декодирования и блок инвертирования, причем информационный вход и корректирующие входы блока декодирования соединены соответственно с выходом первого накопителя и выходом второго накопителя, входы блока инвертирования соединены с выходами блока декодирования, а выходы - с информационными входами коммутатора. 3 ил.

/// Jr //5 /f.U rf.5 /f6 Itm-i 71. т

Фиг.г

//; rt2

т

/ft i/rr- z п. 21

fff.f

7Tm-f f ///7г-Л 7/т

| Постоянное запоминающее устройство | 1977 |

|

SU627543A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU597009A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

Авторы

Даты

1988-03-15—Публикация

1986-04-07—Подача