Изобретение относится к вычислительной технике и может быть использовано для повышения надежности запоминающих устройств, выполненных на интегральных микросхемах.

Цель изобретения -- повышение надежности устройства.

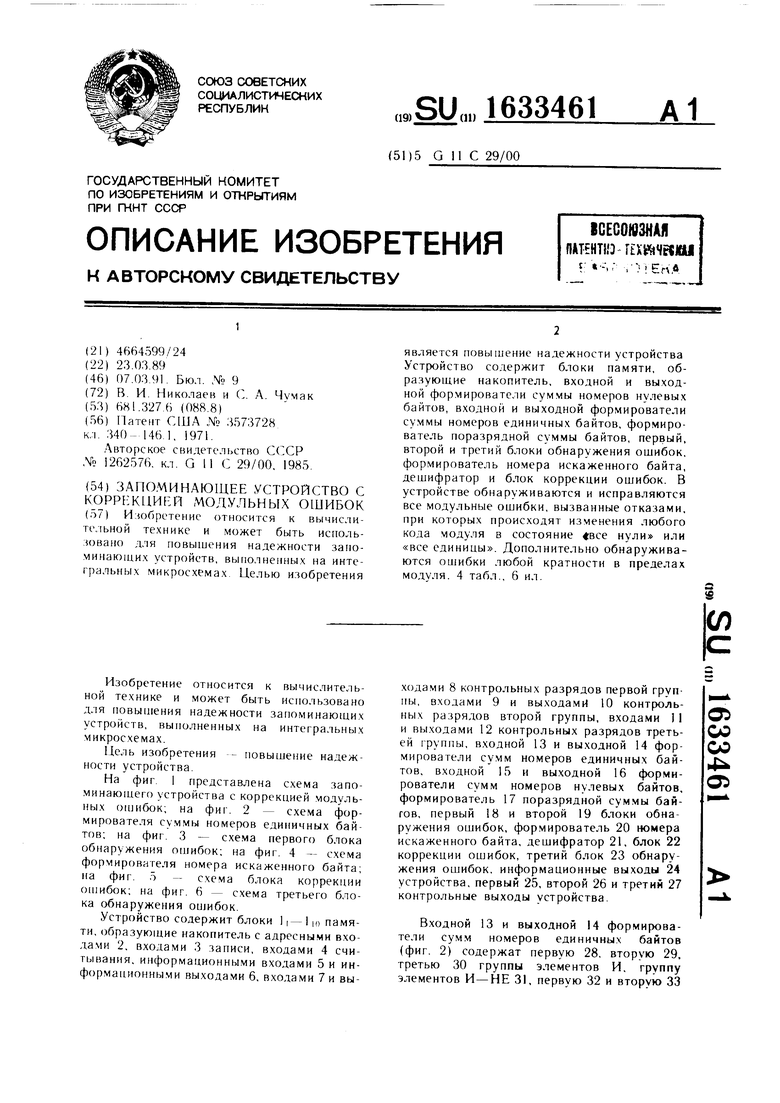

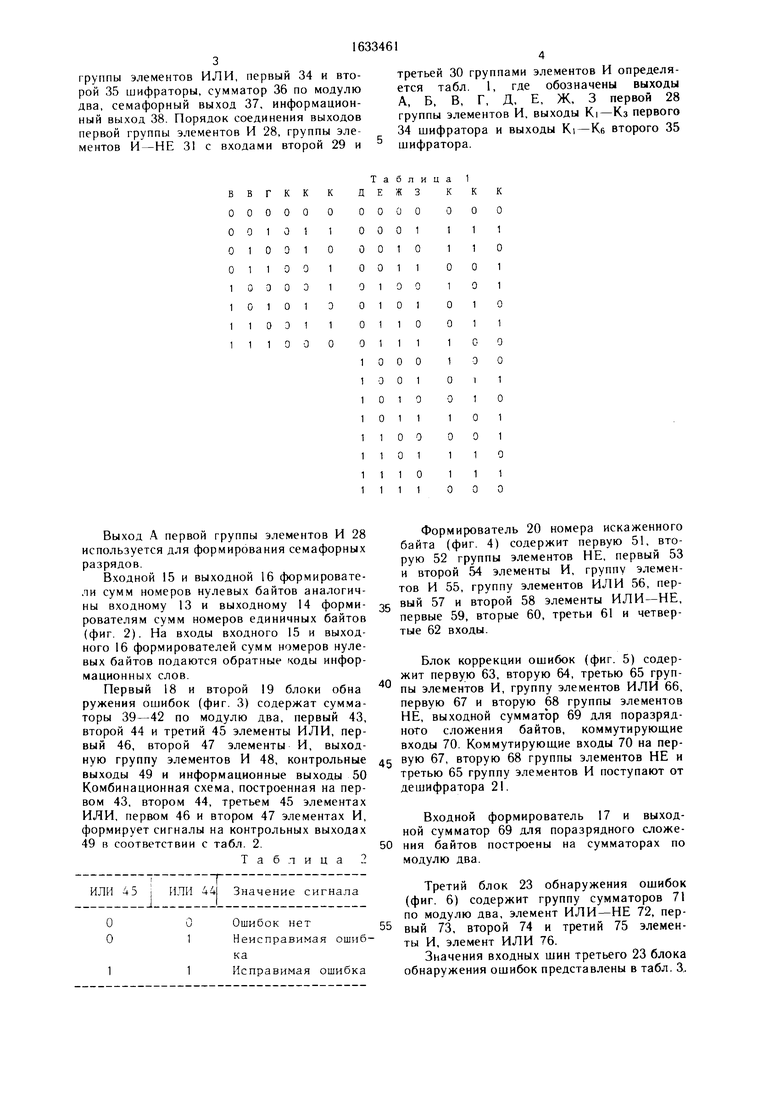

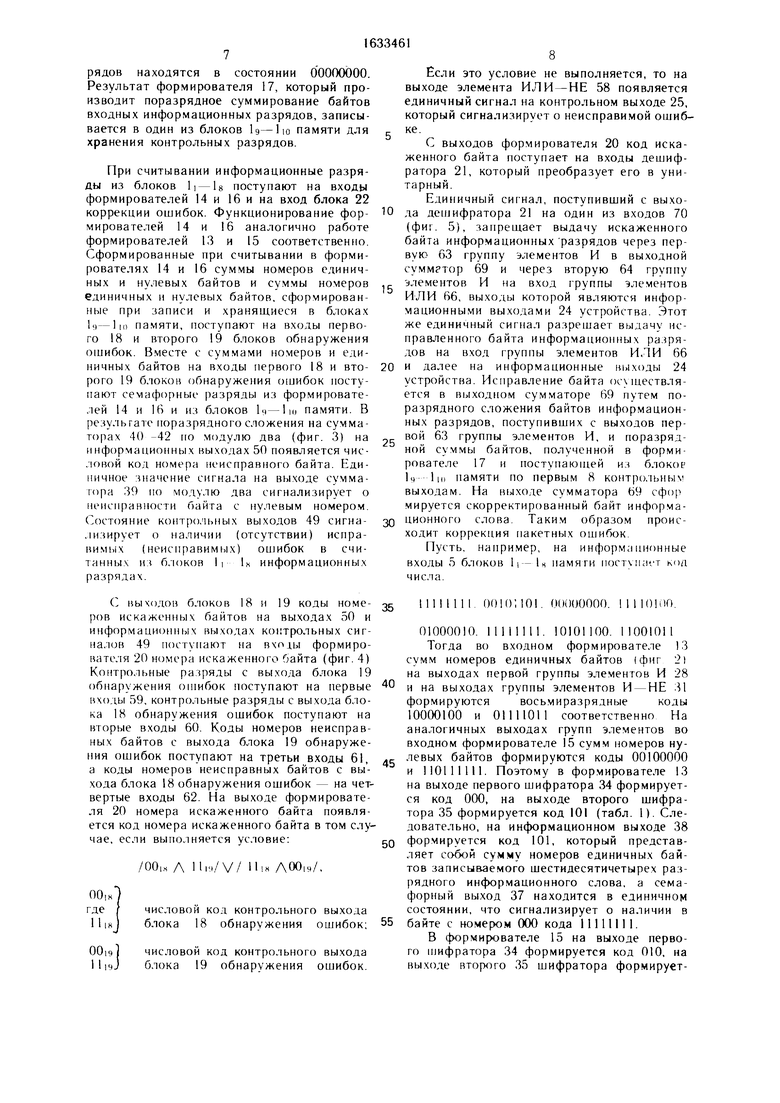

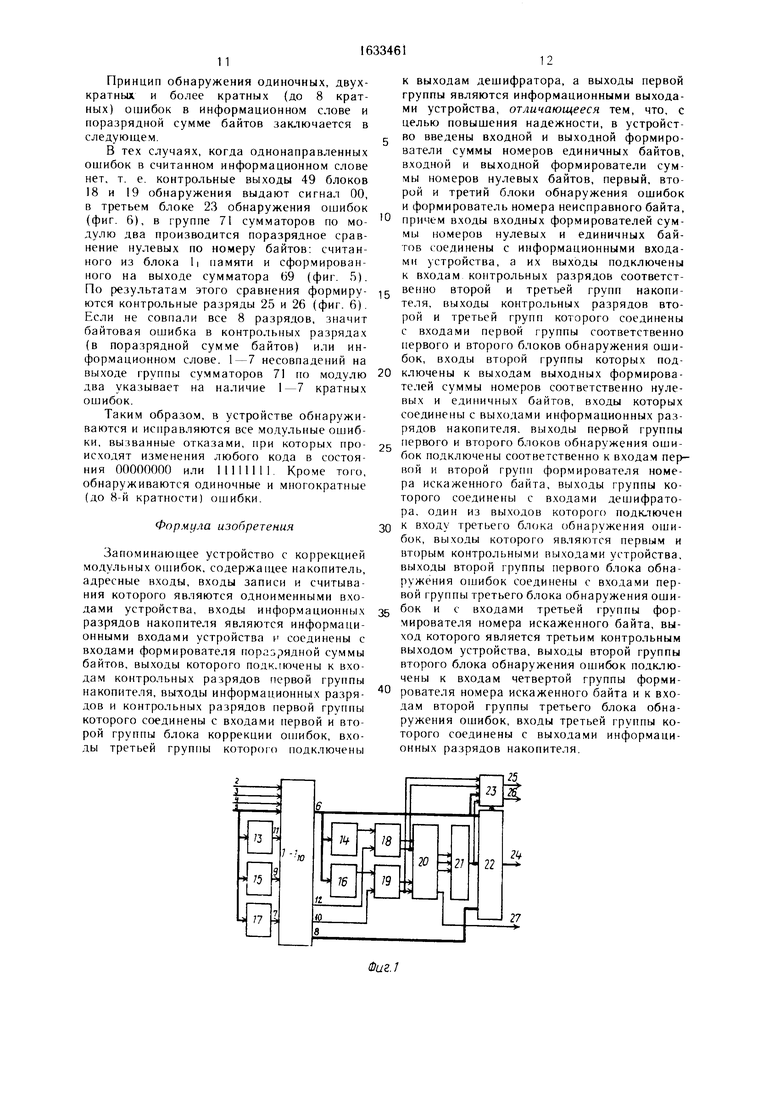

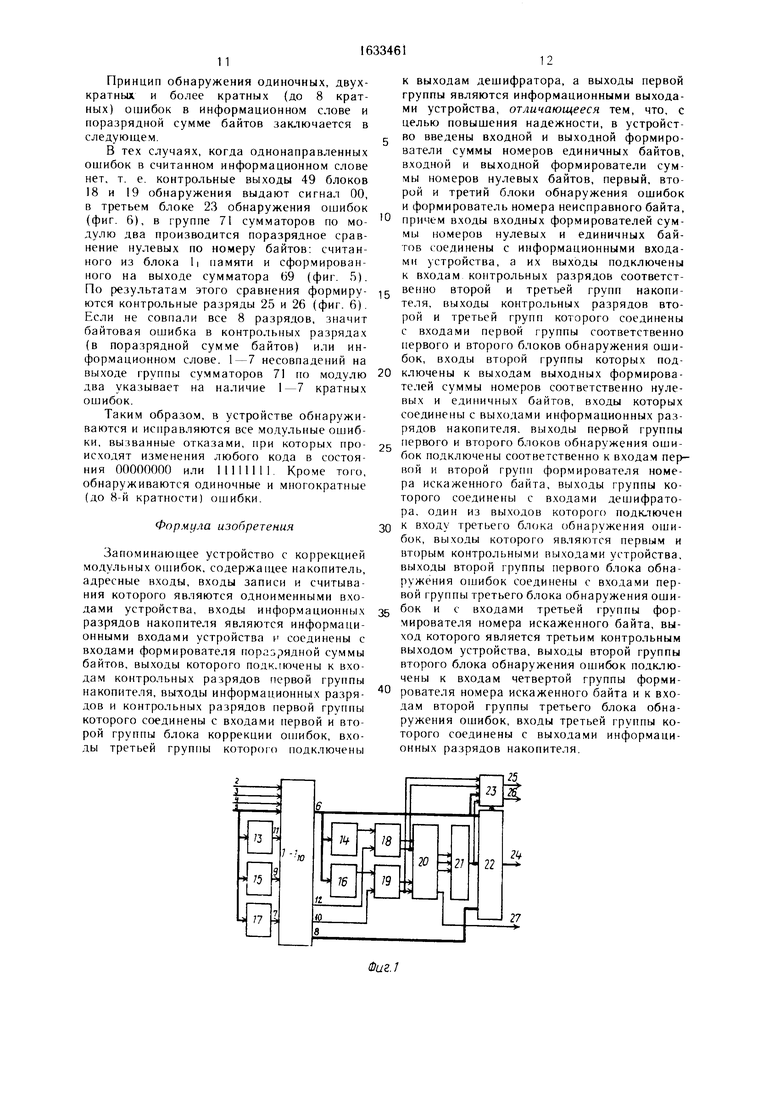

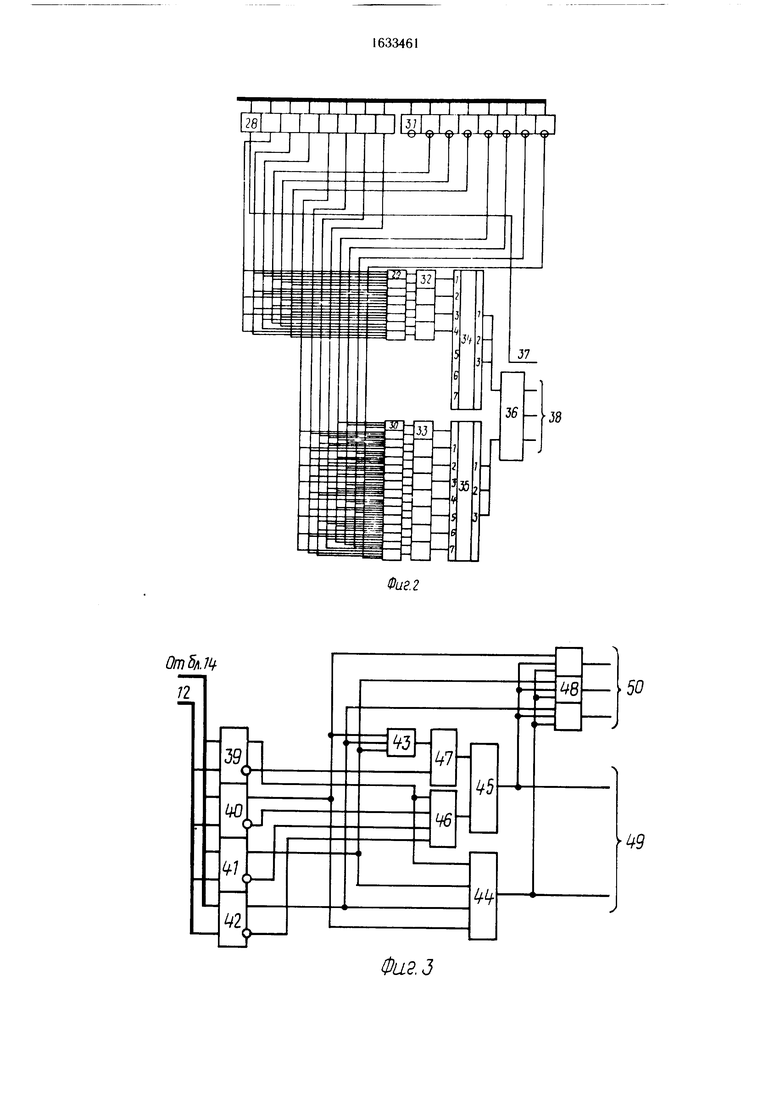

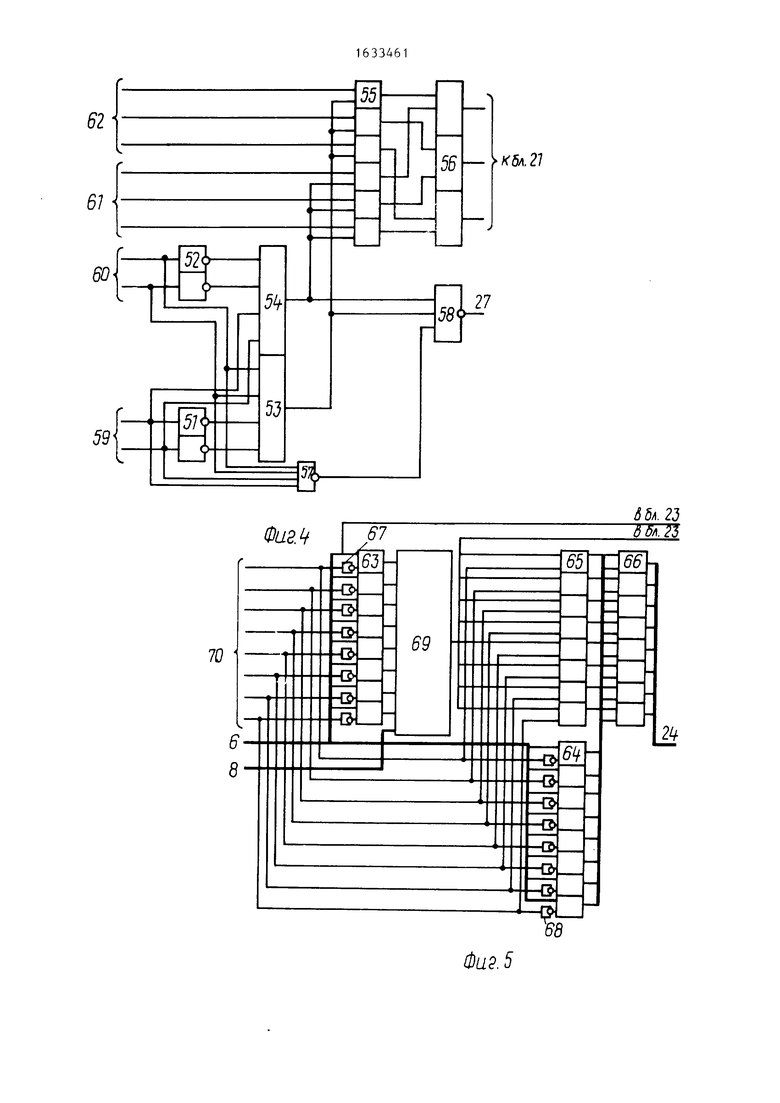

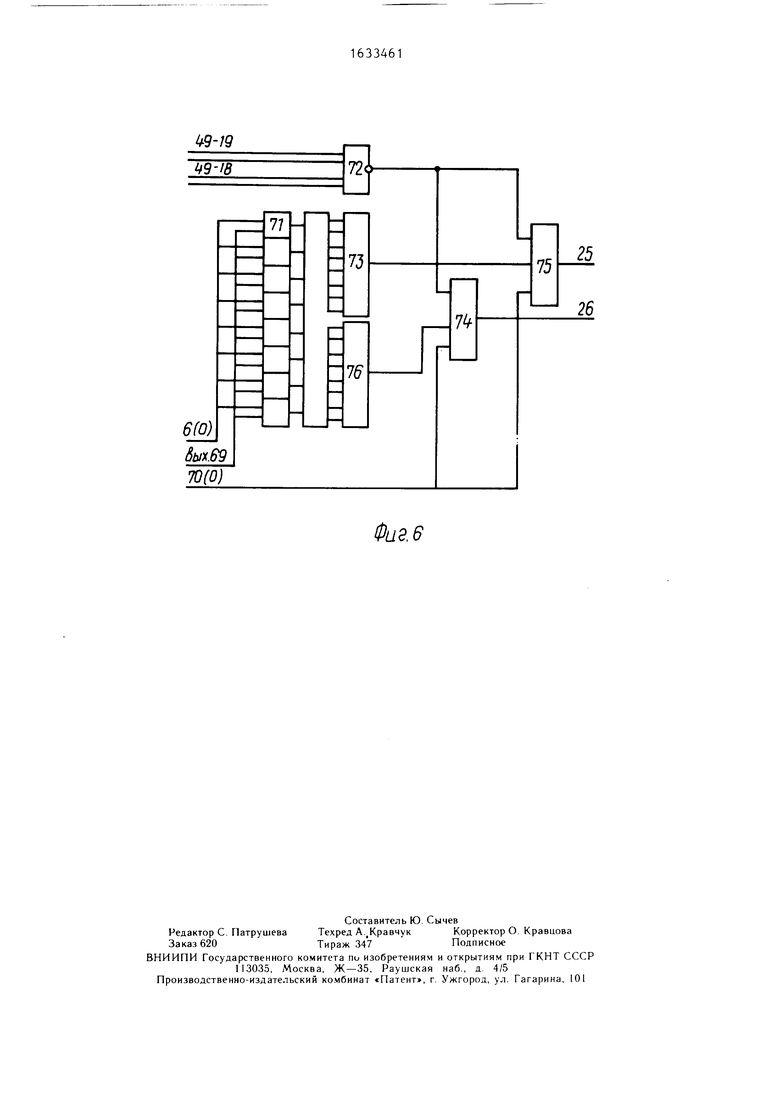

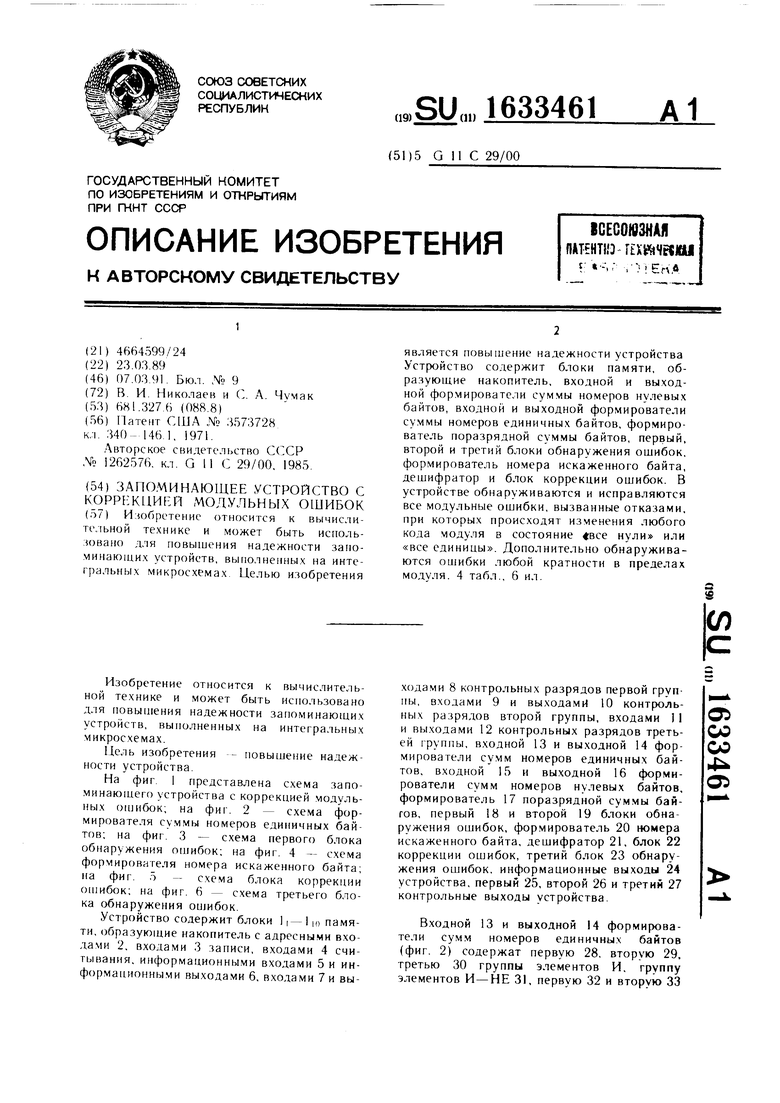

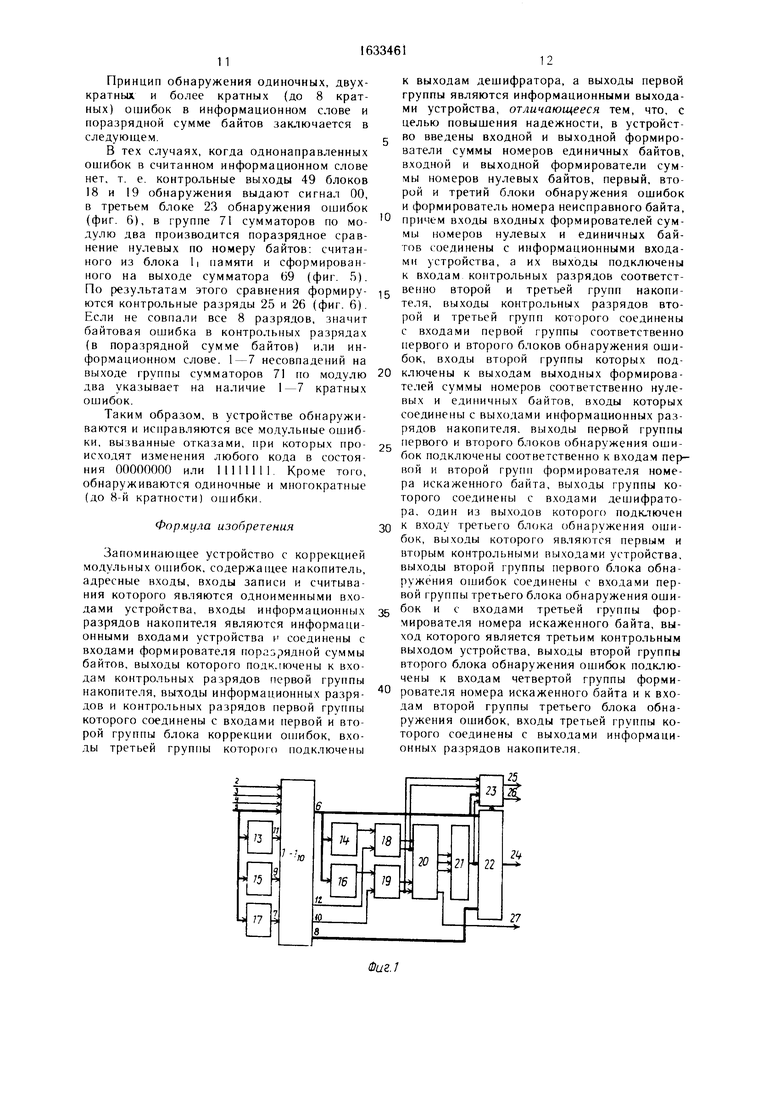

На фиг 1 представлена схема запоминающего устройства с коррекцией модульных ошибок; на фиг. 2 - схема формирователя суммы номеров единичных байтов; на фиг. 3 - схема первого блока обнаружения ошибок; на фиг. 4 - схема формирователя номера искаженного байта; на фиг. 5 - схема блока коррекции ошибок; на фиг. 6 - схема третьего блока обнаружения ошибок.

Устройство содержит блоки 1,- 1 ю памяти, образующие накопитель с адресными входами 2. входами 3 записи, входами 4 считывания, информационными входами 5 и информационными выходами 6, входами 7 и выходами 8 контрольных разрядов первой группы, входами 9 и выходами 10 контрольных разрядов второй группы, входами 1 1 и выходами 12 контрольных разрядов третьей группы, входной 13 и выходной 14 формирователи сумм номеров единичных байтов, входной 15 и выходной 16 формирователи сумм номеров нулевых байтов, формирователь 17 поразрядной суммы байтов, первый 18 и второй 19 блоки обнаружения ошибок, формирователь 20 номера искаженного байта, дешифратор 21, блок 22 коррекции ошибок, третий блок 23 обнаружения ошибок, информационные выходы 24 устройства, первый 25, второй 26 и третий 27 контрольные выходы устройства.

Входной 13 и выходной 14 формирователи сумм номеров единичных байтов (фиг. 2) содержат первую 28. вторую 29, третью 30 группы элементов И, группу элементов И - НЕ 31, первую 32 и вторую 33

О

со со

Јь

О

группы элементов ИЛИ, первый 34 и второй 35 шифраторы, сумматор 36 по модулю два, семафорный выход 37, информационный выход 38. Порядок соединения выходов первой группы элементов И 28, группы элементов И-НЕ 31 с входами второй 29 и

шифратора.

третьей 30 группами элементов И определяется табл. 1, где обозначены выходы А, Б, В, Г, Д, Е, Ж, 3 первой 28 группы элементов И, выходы Ki-Кз первого 34 шифратора и выходы Ki-Кб второго 35

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Формирователь кода маски | 1987 |

|

SU1501169A1 |

| Устройство для обнаружения и исправления ошибок | 1982 |

|

SU1149263A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2448359C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ПРОИЗВОЛЬНЫХ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2450331C1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 1999 |

|

RU2210805C2 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Устройство для контроля информации на четность | 1985 |

|

SU1339898A1 |

Выход А первой группы элементов И 28 используется для формирования семафорных разрядов.

Входной 15 и выходной 16 формирователи сумм номеров нулевых байтов аналогичны входному 13 и выходному 14 формирователям сумм номеров единичных байтов (фиг. 2). На входы входного 15 и выходного 16 формирователей сумм номеров нулевых байтов подаются обратные чоды информационных слов.

Первый 18 и второй 19 блоки обна ружения ошибок (фиг. 3) содержат сумматоры 39-42 по модулю два, первый 43, второй 44 и третий 45 элементы ИЛИ, первый 46, второй 47 элементы И, выходную группу элементов И 48, контрольные выходы 49 и информационные выходы 50 Комбинационная схема, построенная на первом 43, втором 44, третьем 45 элементах ИЛИ, первом 46 и втором 47 элементах И, формирует сигналы на контрольных выходах 49 в соответствии с табл. 2.

Таблица 2

ка

Исправимая ошибка

Таблица 1

Формирователь 20 номера искаженного байта (фиг. 4) содержит первую 51, вторую 52 группы элементов НЕ, первый 53 и второй 54 элементы И, группу элементов И 55, группу элементов ИЛИ 56, пер- 5 вый 57 и второй 58 элементы ИЛИ-НЕ, первые 59, вторые 60, третьи 61 и четвертые 62 входы.

Блок коррекции ошибок (фиг. 5) содержит первую 63, вторую 64, третью 65 группы элементов И, группу элементов ИЛИ 66, первую 67 и вторую 68 группы элементов НЕ, выходной сумматор 69 для поразрядного сложения байтов, коммутирующие входы 70. Коммутирующие входы 70 на пер- 5 вую 67, вторую 68 группы элементов НЕ и третью 65 группу элементов И поступают от дешифратора 21.

Входной формирователь 17 и выходной сумматор 69 для поразрядного сложе- 0 ния байтов построены на сумматорах по модулю два.

Третий блок 23 обнаружения ошибок (фиг. 6) содержит группу сумматоров 71 по модулю два, элемент ИЛИ-НЕ 72, пер- вый 73, второй 74 и третий 75 элементы И, элемент ИЛИ 76.

Значения входных шин третьего 23 блока обнаружения ошибок представлены в табл. 3.

Таблица 3

Обозначение в, ода

Откуда считываются значения

С контрольных выходов

49 второго 19 блока обнаружения ошибок

С контрольных выходов

49 первого 18 блока обнаружения ошибок

С нулевого по номеру байта информационного выхода 6

С выхода сумматора 69

С нулевого по номеру из коммутирующих входов 70

Выходы 25 и 26 третьего блока 23 обнаружения ошибок являются первым 25 и вторым 26 контрольными выходами ст- ройства

Сигналы на выходах 25 и 26 форми руются в соответствии с табл 4

Таблица 4

Байтовая ошибка в первом контрольном байте.

1,2,3,4,5,6 ипи 7 - кратная ошибка

Работу рассмотрим на примере устройства, выполненного на базе восьмиразрядных блоков памяти и предназначенного для хра нения шестидесятичетырех разрядных информационных слов При записи информационного слова в блоки памяти определяются байты этого слова с кодами 00000000 и 11111111 и отдельно суммируются номера этих байтов Если код 00000000 или 11111111 содержится в байте с номером 000, то выставляется единичный сигнал на одной из двух позиций контрольных разрядов, указывающих на наличие в байте с номером 000 кодов 00000000 или 11111111

Для хранения контрольных разрядов потребуется два байта один байт контрольных разрядов используется для хранения поразрядной суммы байтов информа ционного слова, второй байт - для хранения суммы номеров байтов, код которых состоит из единиц (три разряда), суммы но меров байтов, код которых состоит из нулей (три разряда), а также для хра

0

5

0

5

0

5

0

5

нения двух контрольных разрядов, указавших на наличие в байте с номером 000 кодов 00000000 или 11111111

При записи информационного слова в блоки 1| - la памяти формируются поразрядная сумма байтов информационного слова и суммы номеров единичных и нулевых байтов, которые записываются в бло.ки lj 110 памяти

При считывании информационно ч слова из блоков 1|-lg памяти формируются суммы номеров единичных и нулевых байтов, которые в блоках обнаружения ошибок суммируются по модулю два со считанными из блока памяти суммами единичных и нулевых байтов

Если, например, в результате отказа из блоков 1, -18 вместо записанного байта информационного слова считывается константа 11111111, то на выходе первого 18 блока обнаружения ошибок формируется номер этого байта

Этот номер искаженного байта через формирователь 20 номера искаженного байта по ступает на дешифратор 21 Единичный сигнал, сформированный в результате дешифрации, заблокирует выдачу искаженного байта Вместо искаженного байта выдается истинный байт информации, полученной в результате поразрядного суммирования по модулю два исправных байтов и считанной из блока памяти порязрядной суммы байтов

Устройство работает следующим образом

При записи коды чисел по входам 5 поступают на информационные входы блоков li- IN и на входы формирователей 13, 15 и 17, формирование контрольных раз рядов Ki - Кь в формирователях 13 и 15 происходит в соответствии с табл 1, которая указывает последовательность получения контрольных разрядов Ki - Kh в режимах записи и считывания

Например, если в единичном состоянии на ходится только нулевой, второй и пятый байты информационных разрядов, т е их состояние соответствует коду 11111111, то на выходе первой группы элементов И 28 формируется код 10010100, на выходе группы элементов И -НЕ 31 формируется код 01101011 (фиг 2) В результате этого на выходе первого шифратора 34 формируются сигналы Ki - Кз, код которых 011, и на выходе второго шифратора 35 формируются сигналы К4-КБ, код которых 101 Эти контрольные разряды Ki - К5 и К4-Кб складываются по модулю два в сумматоре 36, на информационном 38 выходе которого формируется сумма номеров единичных байтов 110 Единичное состояние семафорно го выхода 37 сигнализирует об едичнич- ном состоянии байта с номером 000

Ааналогична работа формирователя 15

суммы номеров нулевых байтов, если один или несколько байтов информационных разрядов находятся в состоянии 00000000. Результат формирователя 17, который производит поразрядное суммирование байтов входных информационных разрядов, записывается в один из блоков 1э-1 ю памяти для хранения контрольных разрядов

При считывании информационные разряды из блоков 1 - Is поступают на входы формирователей 14 и 16 и на вход блока 22 коррекции ошибок Функционирование формирователей 14 и 16 аналогично работе формирователей 13 и 15 соответственно Сформированные при считывании в формирователях 14 и 16 суммы номеров единичных и нулевых байтов и суммы номеров единичных и нулевых байтов, сформированные при записи и хранящиеся в блоках 1) - ho памяти, поступают на входы перво го 18 и второго 19 блоков обнаружения ошибок Вместе с суммами номеров и единичных байтов на входы первого 18 и второго 19 блоков обнаружения ошибок поступают семафорные разряды из формирователей 14 и 16 и ш блоков 1ч-IID памяти В результате поразрядного сложения на сумма торах 40 -42 по модулю два (фиг 3) на информационных выходах 50 появляется чис- ювой код номера неисправного байта Единичное значение сигнала на выходе сумма- юра 39 по два сигнали зирует о неисправности байга с нулевым номером Состояние контрольных выходов 49 сигна лизир ет о наличии (отсутствии) исправимых (неисправимых) ошибок в считанных и блоков I, U информационных разрядах

С выходов блоков 18 и 19 коды номеров искаженных байтов на выходах 50 и информационных выходах контрольных сигналов 49 на входы формирователя 20 номера искаженного айта (фиг 4) Контрольные рафяды с выхода блока 19 обнаружения ошибок поступают на первые вхо 1,ы 59, контрольные разряды с выхода блока 18 обнаружения ошибок поступают на вторые входы 60 Коды номеров неисправных байтов с выхода блока 19 обнаружения ошибок поступают на третьи входы 61, а коды номеров неисправных байтов с выхода блока 18 обнаружения ошибок - на четвертые входы 62 На выходе формирователя 20 номера искаженного байта появляется код номера искаженного байта в том случае, если выполняется условие

/00,s Л 1U/V/ И,,, ЛОО|Ч/,

00,н

где г числовой код контрольного выхода llisj блока 18 обнаружения ошибок,

00,9 числовой код контрольного выхода jj

1 19J

блока 19 обнаружения ошибок

0

5

Если это условие не выполняется, то на выходе элемента ИЛИ- НЕ 58 появляется единичный сигнал на контрольном выходе 25, который сигнализирует о неисправимой ошибке

С выходов формирователя 20 код искаженного байта поступает на входы дешифратора 21, который преобразует его в унитарный

Единичный сигнал, поступивший с выхода дешифратора 21 на один из входов 70 (фиг 5), запрещает выдачу искаженного байта информационных разрядов через пер вую 63 группу элементов И в выходной 69 и через вторую 64 группу элементов И на вход группы элементов ИЛИ 66, выходы которой являются инфор мационными выходами 24 устройства Этот же единичный сигнал разрешает выдач исправленного байта информационных разрядов на вход группы элементов ИЛИ 66 и далее на информационные выходы 24 устройства Исправление байта ск ществля- ется в выходном сумматоре 69 поразрядного сложения байтов информационных разрядов, поступивших с выходов пер вой 63 группы элементов И, и поразряд ной байтов, полученной в форми рователе 17 и поступающей из блокое 1Ч IID памяти по первым 8 контрольных выходам На ныхот,е сумматора 69 сфор мируется скорректированный байт информационного слова Таким образом происходит коррекция пакетных ошибок

Пусть, например, на информационные входы 5 блоков 1| - 1Ч памяти коа числа

пицц оою; 101 оооооооо ииоыо

01000010 11111111 10101100 11001011

Тогда во входном формирователе 13 СУММ номеров единичных байтов (фиг 2) на выходах первой группы элементов И 28 и на выходах группы элементов И - НЕ -И формируются восьмиразрядные коды 10000100 и 01111011 соответственно На аналогичных выходах групп элементов во входном формирователе 15 сумм номеров нулевых байтов формируются коды 00100000 и 110111111 Поэтому в формирователе 13 на выходе первого шифратора 34 формируется код 000, на выходе второго шифратора 35 формируется код 101 (табл 1) Следовательно, на информационном выходе 38

0 формируется код 101, который представляет собой сумму номеров единичных байтов записываемого шестидесятичетырех разрядного информационного слова, а семафорный выход 37 находится в единичном состоянии, что сигнализирует о наличии в

5 байте с номером 000 кода 11111111

В формирователе 15 на выходе первого шифратора 34 формируется код 010, на выходе второго 35 шифратора формирует0

5

0

ся код 000, следовательно, на информационном выходе 38 формируется код 010. а семафорный 37 выход находится в нулевом состоянии.

В формировате е 17 производится поразрядное сложение байтов информационного слова

0-й байт (000) 1-й байт (001) 2-й байт (010) 3-й байт (011) 4-й байт (100) 5-й байт (101) 6-й байт (110) 7-й байт (111) Поразрядная байтов

сумма

Таким образом, в контрольные блоки lg- 1ю памяти будут записаны: код 11111100 поразрядной суммы байтов; код 1101, где первый разряд синнализирует о наличии в байте с номером 000 кода 11111111, а следующие три разряда - сумма номеров единичных байтов; код 0010, где первый разряд сигнализирует об отсутствии в байте с номером 000 кода 00000000, а следующие три разряда представляют сумму номеров нулевых байтов.

Пусть, например, в результате отказа второго блока памяти из блоков li-18 считывается следующее информационное слово:

00000000. 11110100. 10101100. 11001011.

Это информационное слово поступает на выходные блоки формирователя 14 суммы номеров единичных байтов и формирователя 16 сумм номеров нулевых байтов. С выхода формирователя 14 на один из входов первого блока 18 обнаружения ошибок поступит код 1100, где 2, 3, 4 разряды - поразрядная сумма номеров единичных байтов. С выхода формирователя 16 на один из входов второго блока 19 обнаружения ошибок поступит вновь сформированный код 0010.

На вторые входы блоков 18 и 19 по шинам 12 и 10, соответственно, поступят сформированные при записи информационного слова контрольные коды: на блок 18 - код 1101, на блок 19 - код 0010 (фиг. 1). В результате сложения по модулю два в блоке 18 сформируется номер искаженного байта 001:1101 + 1100

0001, который поступит на информационные выходы 50 блока 18 и контрольные разряды с кодом 11. Эти контрольные разряды разрешат выдачу номера искаженного байта на информационные выходы 50 (фиг. 3). В результате функционирования второго блока 19 обнаружения ошибок

вырабатываются коды: на выходе 50-000, на выходе 49-00,0010 +0010

оооо;

Коды с выходов первого 18 и второго 19

блоков обнаружения ошибок поступают на входы формирователя 20 номера ис кажен- ного байта. Код 00 с контрольного выхода 49 блока 19 поступает на первые 59 вхо0 ды формирователя 20 номера исках энного байта, код 11 с контрольного выхода 49 блока 18 поступает на вторые 60 входы формирователя 20, код 000 с информационного 50 выхода блока 19 на третьи входы 61 формирователя 20 и код 001 с вы хода 50 блока 18 на четвертые 62 входы формирователя 20. В результате этого на выходе первого 53 элемента И формируется сигнал единицы, который разрешает выдачу через группу элементов И 55 и далее через

0 группу элементов ИЛИ 56 на дешифратор 21 кода 001 искаженного байта. Одновременно на контрольном выходе 27 устройства формируется нулевой бит, сигнализирующий об отсутствии неисправной ошибки в считанном слове.

Код 001 после дешифрации преобразуется в унитарный код 01000000, который поступает на коммутирующие входы 70 блока 22 коррекции (фиг. 5). Единичный разряд унитарного кода запрещает выдачу через первую группу элементов И 63 на выходной сумматор 69 и череч группу элементов И 64, группу элементов ИЛИ 66 на выход 24 устройства искаженного байта с номером 001. В выходном 69 сумматоре формируется искаженный байт информационного слова, который по разрешающему единичному сигналу унитарного кода через третью группу элементов И 65. через группу элементов ИЛИ 66 поступит на выход 24 устройства на место заблокированного байта с номером 001.

Формирование исправленного байта информации в выходном сумматоре 69 осуществляется за счет поразрядного сложения байтов информационного слова, пропущенных через первую группу элементов И 63 и поразрядной суммы байтов записанного слова, считанной из контрольных блоков

1Ч-ho памяти на выход 8:

5

0

5

0

5

0

5

Ф

11111111-

0000000011110100-

01000010-

11111111- 10101100 11001011

11111100-

00101001-

0-й байт (000)

2-й байт (010)

3-й байт (01 1 )

4-й байт (100)

5-й байт (101)

6-й байт (ПО)

7-й байт (111)

Поразрядная сумма

байтов

Исправленный байт с

номером 001.

11

Принцип обнаружения одиночных, двухкратных и более кратных (до 8 кратных) ошибок в информационном слове и поразрядной сумме байтов заключается в следующем

В тех случаях, когда однонаправленных ошибок в считанном информационном слове нет, т е контрольные выходы 49 блоков 18 и 19 обнаружения выдают сигнал 00, в третьем блоке 23 обнаружения ошибок

к выходам дешифратора, а выходы первой группы являются информационными выходами устройства, отличающееся тем, что, с целью повышения надежности, в устройст во введены входной и выходной формирователи суммы номеров единичных байтов, входной и выходной формирователи сум мы номеров нулевых байтов, первый, вто рой и третий блоки обнаружения ошибок и формирователь номера неисправного байта,

в тпетьем блоке z,i оонаруженин ошииок ч- гi(фи 6) в группе 71 сумматоров по мо 10 причем входы входных формирователей сум (фиг о;, в ipymie Lyимы номеров нулевых и единичных баи

гов соединены с информационными входами устройства, а их выходы подключены

к входам контрольных разрядов соответст

Если не совпали все 8 разрядов, значит байтовая ошибка в контрольных разрядах (в поразрядной сумме байтов) или информационном слове 1-7 несовпадений на

дулю два производится поразрядное сравнение нулевых по номеру байтов считан ного из блока Ь памяти и сформирован

s.s, - ™ЈЕ

с входами первой группы соответственно первого и второго блоков обнаружения ошибок входы второй группы которых под

rxPoTTvrb; a;op;B 7rD;;r; ;ro 20 «люмены к выходам выходных формирова дваТказРывает „I налиме 1-7 кратных °Ш Та°кКим образом, в устройстве обнаружи-соединены с выходами информационных раз

ваются и исправляются все модульные ошибРЯДОВ накопителя выходы первой группы

„„„пеового и второго блоков обнар жения оши

ки, вызванные отказами, при которых про 25 соответственной входам первой и второй групп формирователя номера искаженного байта, выходы группы ко торого соединены с входами дешифрато ра один из выходов которого подключен Зо к вход третьего блока обнаружения ошибок, выходы которого являются первым и вторым контрольными выходами устройства, выходы второй группы первого блока обна р жения ошибок соединены с вхояами пер вой группы третьего блока обнаружения оши

,а:„ ;с™йства в™Ды и фор«аиионны 36 б т СтьеЙ Ф°Р 2азр,дУоВ Р„ак„„„те.„ ..,ЯЮТСФ, Р„„фоР„аи„ кГо Г Г о ьГм

выходом устройства, выходы второй группы второго блока обнаружения ошибок подключены к входам четвертой группы форми

накопителя, выходы информационных разря 40 рователя номера искаженного байта и к вхо дов и контрольных разрядов первой группылам второй группы третьего блока обнаугружения ошибок, входы третьей группы которого соединены с выходами информационных разрядов накопителя

исходят изменения любого кода в состоя ния 00000000 или 11111111 Кроме того, обнаруживаются одиночные и многократные (до 8 и кратности) ошибки

Форсила изобретения

Запоминающее устройство с коррекцией МОДУЛЬНЫХ ошибок, содержащее накопитель, адресные входы, входы записи и считыва ния которого являются одноименными вхо

онными входами устройства и соединены с входами формирователя поразрядной суммы байтов, выходы которого подключены к вхо дам контрольных разрядов первой группы

которого соединены с входами первой и вто рой группы блока коррекции ошибок, вхо- 1Ы третьей группы которого подключены

1633461

к выходам дешифратора, а выходы первой группы являются информационными выходами устройства, отличающееся тем, что, с целью повышения надежности, в устройст во введены входной и выходной формирователи суммы номеров единичных байтов, входной и выходной формирователи сум мы номеров нулевых байтов, первый, вто рой и третий блоки обнаружения ошибок и формирователь номера неисправного байта,

ч- гi0 причем входы входных формирователей сум мы номеров нулевых и единичных баи

гов соединены с информационными входами устройства, а их выходы подключены

к входам контрольных разрядов соответст

s.s, - ™ЈЕ

- 50

Фиг.З

60

52

з5Ь

56

К5л, 21

58

27

65л. 23

Фи$.5

W-1Q W-tB

73

75

25

%

L- 26

Фие.б

| Патент США № 3573728 кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Авторское свидетельство СССР ,Чо 1262576 | |||

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-03-07—Публикация

1989-03-23—Подача