(54) ЛОГИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логического управления | 1981 |

|

SU993260A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Логическое устройство | 1979 |

|

SU877539A2 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для программного управления | 1989 |

|

SU1698875A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения | 1980 |

|

SU877520A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Устройство для синхронизации | 1981 |

|

SU1012228A1 |

1

Изобретение относится к автоматическим устройствам дискретного типа, решающим задачи логического управления, описываемые системой уравнений временных булевых функций по заданному алгоритму последовательно во времени.

Известно логическое устройство по авт. св. № 189630, содержащее программный блок, состоящий из генератора импульсов и накопителя программ, дешифратор команд, входные элементы и выходные элементы И, элемент ИЛИ, элемент НЕ, сдвигающий регистр, элемент И, логический блок, реле времени, ячейку памяти 1.

Однако данное устройство не обеспечивает высокого быстродействия из-за необходимости повторения переменных, когда их число в произведении меньше разрядности сдвигающего регистра, и пересылки результата умножения в первый разряд сдвигающего регистра, когда число переменных в произведении больше разрядности сдвигающего регистра.

Цель изобретения - повышение быстродействия схемы при выполнении логических операций и сокращение программы вычислений.

Поставленная цель достигается тем, что в устройство введены два элемента И, элемент НЕ, формирователь синхроимпульса, формирователь импульса уставки сдвигающего регистра, триггер уставки сдвигающего регистра, выход которого через формирователь импульса уставки сдвигающего регистра подключен ко входу уставки сдвигающего регистра, управляющий вход которого соединен с первым входо.м первого элемента И и через элемент НЕ - с первым входом второго элемента И, второй вход первого элемента И соединен со вторым входом второго элемента И и

через с{)ормирователь синхроимпульса с тактовым выходом программного блока, выходы первого и второго эле.ментов И соединены соответственно с единичным и нулевым входами триггера уставки сдвигающего регистра.

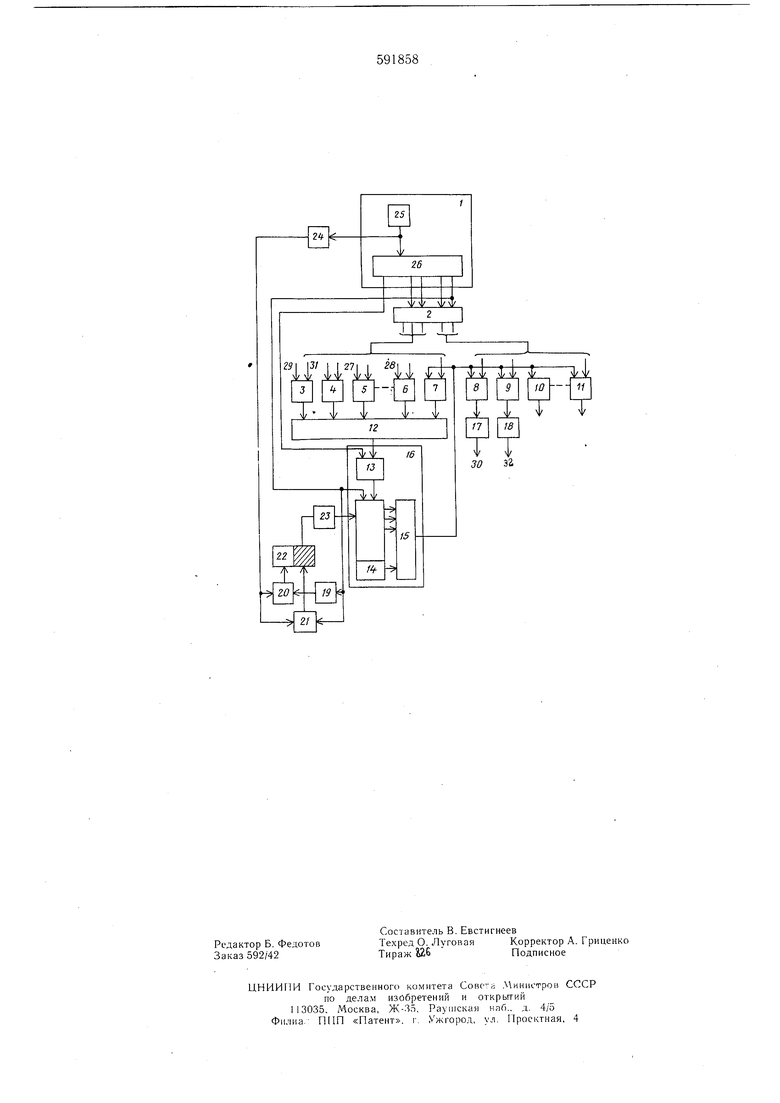

На чертеже представлена структурная электрическая схема устройства.

Устройство содержит программный блок 1, дешифратор команд 2, входные элементы И 3-7, выходные элементы И 8-11, элемент ИЛИ 12, элемент НЕ 13 входной переменной, сдвигающий регистр 14, элемент И 15, логический блок 16, реле времени 17, элемент памяти 18, элемент НЕ 19, элементы И 20, 21, триггер 22 уставки сдвигающего регистра, формирователь 23 импульса уставки сдвигающего регистра, формирователь синхрои.мпульса 24,

генератор импульсов 25, накопитель программ 26.

Программный блок 1 вырабатывает команду, СОСТОЯШ.УЮ из адреса входного и выходного элемента И и признака инвертирования входной переменной. Дешифратор команд 2 преобразует код выбранного адреса в управляющий сигнал, подаваемый на соответствующий элемент И 8-11. Одновременно сигнал инвертирования входной переменной подается в логический блок 16 на управляющий вход элемента НЕ 13, фор.мирователь 24 формирует синхроимпульс. Входные переменные, закодированные цифрами «О и «1, поступают на входы 27, 28 элементов И 5, системы обегающего контроля или непосредственно с датчиков.

Наряду с входными переменными на вход 29 элемента И 3 подается сигнал с выхода 30 реле времени 17, на вход 31 элемента И 4 - с выхода 32 элемента памяти 18, а на вход элемента И 7 - с выхода логического блока 16. По сигналу с дешифратора команд 2 открывается один из входных элементов И 3-1, и входная переменная через элемент ИЛИ 12 и элемент НЕ 13 записывается в первый разряд сдвигающего регистра 14. Сигнал с программного блока 1 (первый разряд кода адреса), разрешающий запись в сдвигающий регистр 14, поступает также на элемент И 21 и через элемент НЕ 19 - на элемент И 20. На вторые входы элементов И 20 и 21 подается синхроимпульс с формирователя 24. Выходы элементов И 20 и 21 подключены соответственно ко входам Уст. «О и Уст «1 триггера уставки сдвигающего регистра 22. Таким образом, по приходу синхроимпульса триггер 22 устанавливается в состояние, которое определяется значением первого разряда кода адреса.

Следовательно, при решении конъюнкции триггер уставки сдвигающего регистра 22 находится в единичном состоянии, а при выдаче результатов - в нулевом. Сигнал с единичного выхода триггера 20 поступает на формирователь импульса уставки сдвигающего регистра 23, который формирует импульс уставки регистра по переднему фронту входного сигнала. По началу вычисления новой конъюнкции сформированный импульс устанавливает все разряды сдвигающего регистра 14 в единичное состояние, поэтому нет необходимости при вычислении произведения заполнять все разряды последнего. По этой же причине можно увеличить число разрядов сдвигающего регистра, не опасаясь при этом увеличения програм.мы, что позволит сократить количество перезаписей результата вычислений в первый разряд сдвигающего регистра.

Таким образом, введение дополнительных блоков позволяет в значительной мере сократить объем программы, а также повысить быстродействие логического устройства.

Формула изобретения

Логическое устройство по авт. св. № 189630, отличающееся тем, что, с целью повышения быстродействия, в него введены два элемента И, элемент НЕ, формирователь синхроимпульса, формирователь импульса уставки сдвигающего регистра, триггер уставки сдвигающего регистра, выход которого через формирователь импульса уставки сдвигающего регистра подключен ко входу уставки сдвигающего регистра, управляющий вход которого соединен с первым входом первого элемента И и через элемент НЕ - с первым входом второго элемента И, второй вход первого элемента И соединен со вторым входом второго эле.мента И и через формирователь синхроимпульса - с тактовым выходом программного блока, выходы первого и второго элементов И соединены соответственно с единичным и нулевы.м входами триггера уставки сдвигающего регистра.

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1978-02-05—Публикация

1976-10-11—Подача