54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для коммутации сообщений | 1988 |

|

SU1529235A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для обмена информацией | 1984 |

|

SU1180905A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Адаптивное вычислительное устройство | 1984 |

|

SU1203506A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

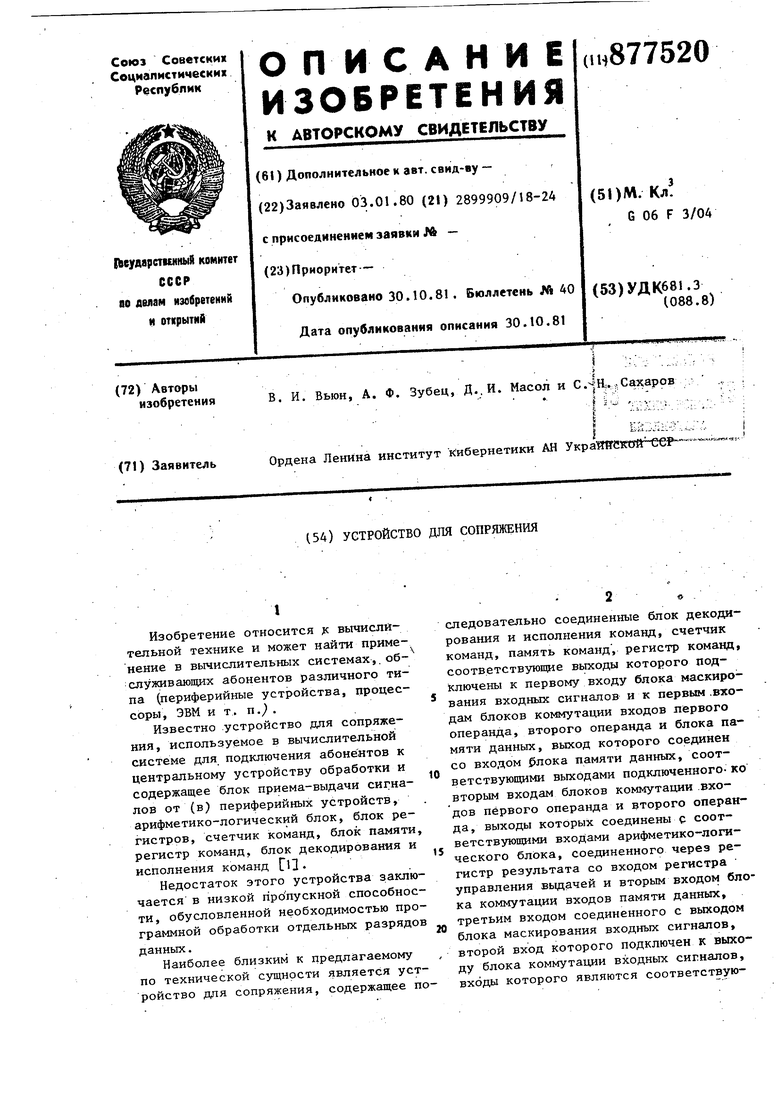

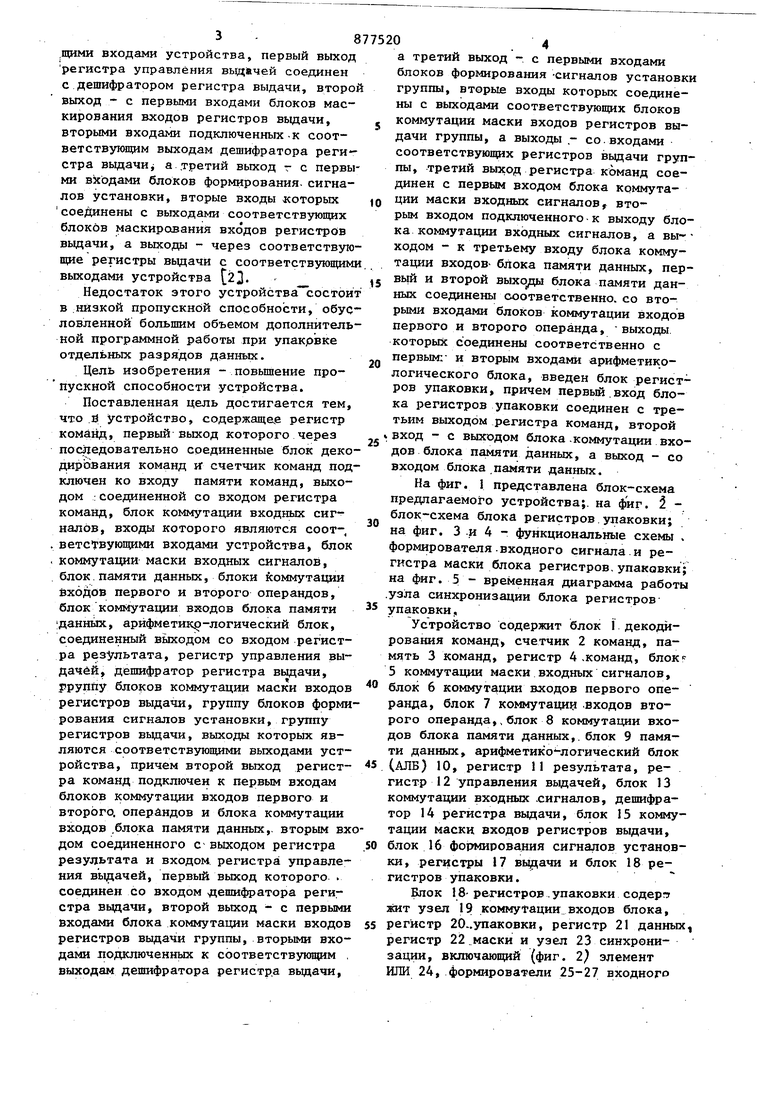

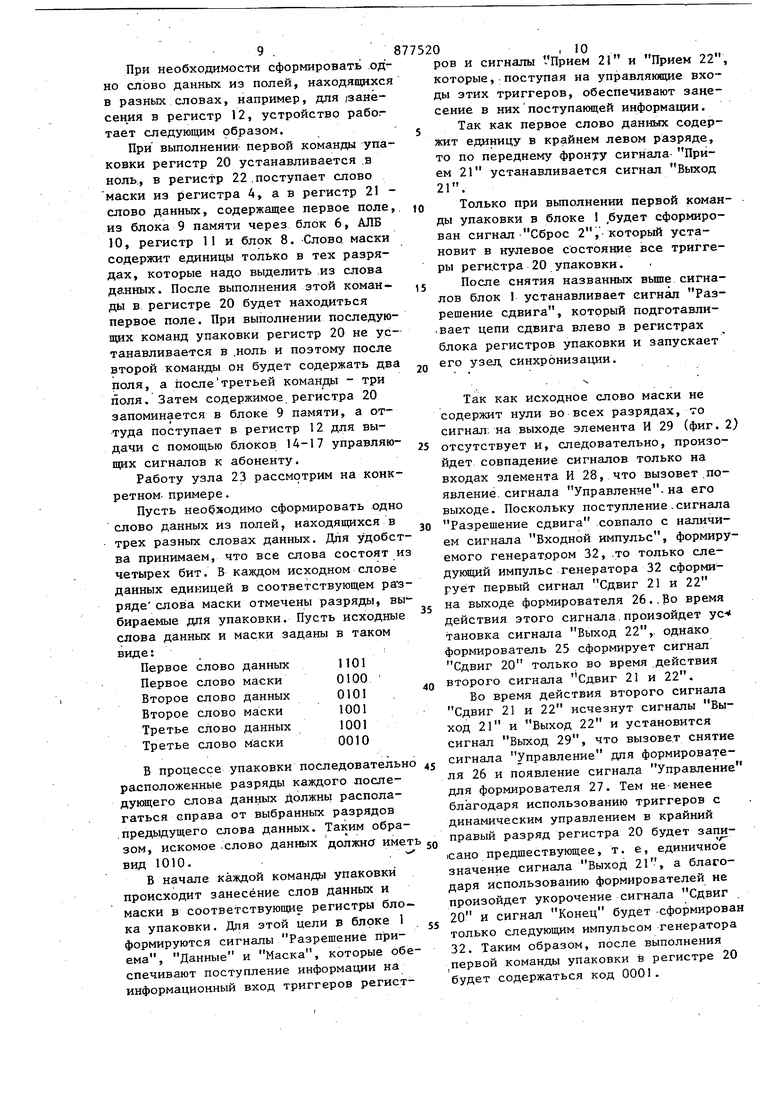

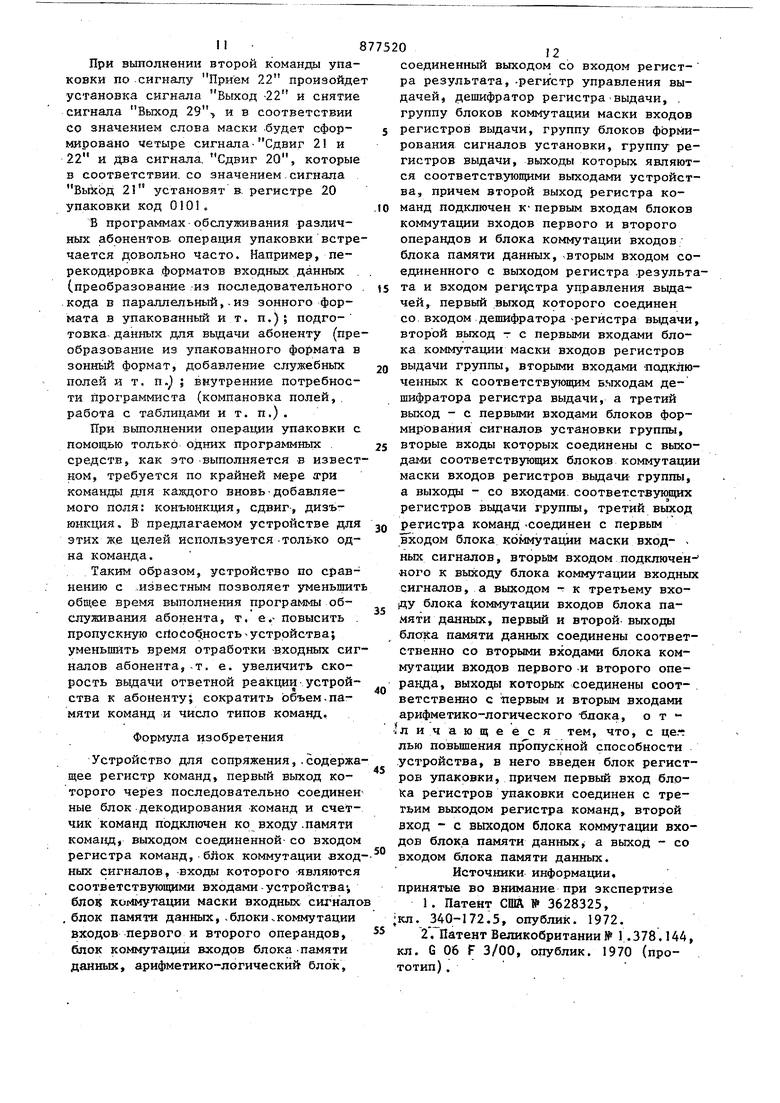

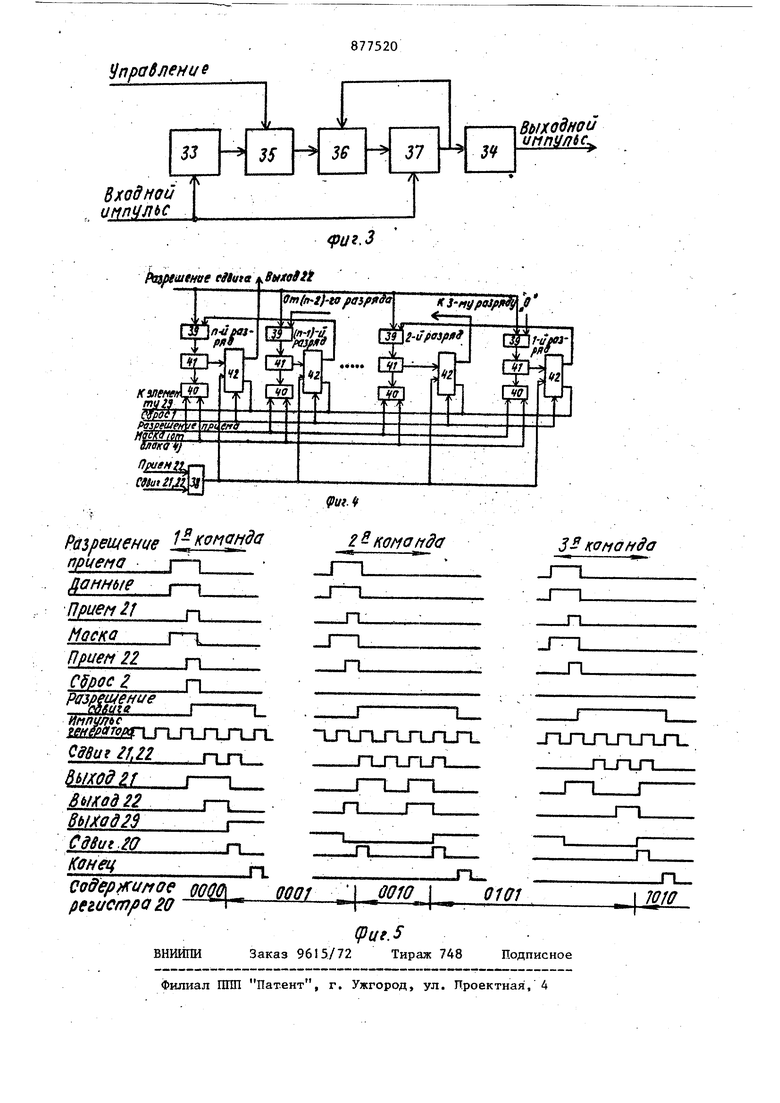

Изобретение относится у. вычислительной технике и может найти применение в вычислительных системах,. об слузшвающих абонентов различного типа (периферийные устройства, процессоры, ЭВМ и т. п. . Известно .устройство для сопряжения, используемое в вычислительной системе для подключения абонентов к центральному устройству обработки и содержащее блок приема-выдачи сигналов от (в) периферийных устройств, арифметико-логический блок, блок регистров, счетчик команд, блок памяти регистр команд, блок декодирования и исполнения команд ГО Недостаток этого устройства заклю чается в низкой пропускной способнос ти, обусловленной необходимостью про граммной обработки отдельных разрядо данных. Наиболее близким к предлагаемому по технической сущности является уст ройство для сопряжения, содержащее п следовательно соединенные блок декодирования и исполнения команд, счетчик команд, память команд , регистр команд, соответствующие вьрсоды которого подключены к первому входу блока маскирования входных сигналов и к первым .входам блоков коммутации входов первого операнда, второго операнда и блока памяти данных, выход которого соединен со входом &лока памяти данных, соответствующими выходами подключенного- ко вторым входам блоков коммутации .входов первого операнда и второго операн да, выходы которых соединены с соответствующими входами арифметико-логического блока, соединенного через регистр результата со входом регистра управления выдачей и вторым входом блока коммутации входов памяти данных, третьим входом соединенного с выходом блока маскирования входных сигналов, второй вход которого подключен к выходу блока коммутации входных сигналов, входы которого являются соответствую,щими входами устройства, первый выход регистра управления вьщйчей соединен с дешифратором регистра выдачи, второ выход - с первыми входами блоков маскирования входов регистров выдачи, вторыми входами подключенных-к соответствующим выходам дешифратора регистра вьщачи а третий выход г с первы ми входами блоков формирования, сигналов установки, вторые входы которых соединены с выходами соответствующих блоков маскирования входов регистров выдачи, а выходы - через соответствую щие регистры вьщачи с соответствующим выходами устройства зД. Недостаток этого устройства состои в низкой пропускнбй способности, обус ловленной большим объемом дополнитель ной программной работы при упакрвке отдельньпс разрядов данных. Цель изобретения - повьш1ение пропускной способности устройства. Поставленная цель достигается тем, что .а устройство, содержащее регистр команд, первый выход которого через последовательно соединенные блок деко дирования команд иг счетчик команд под ключен ко входу памяти команд, выходом :соединенной со входом регистра команд, блок коммутации входных сигналов, входы которого являются СООТ-, . ветствующими входами устройства, блок , коммутации маски входных сигналов, блок.памяти данных, блоки Коммутации входов первого и второго операндов, блок коммутации входов блока памяти :данных, арифметико-логический блок, соединенный выходом со входом регистра результата, регистр управления выдачей, дешифратор регистра выдачи, рруцпу блоков коммутации маски входов регистров выдачи, группу блоков форми рования сигналов установки, группу регистров выдачи, выходы которых являются соответствующими выходами устройства, причем второй выход регистра команд подключен к первым входам блоков коммутации входов первого и второго, операндов и блока коммутации входов .блока памяти данных,, вторым вх дом соединенного с- выходом регистра результата и входом, регистра управления выдачей, первый выход которого . соединен со входом дешифратора регистра выдачи, второй выход - с первыми входами блока коммутации маски входов регистров выдачи группы, вторыми входами лодключенных к соответствующим , выходам дешифратора регистра вьщачи. а третий выход - с первыми входами блоков формирования -сигналов установки группы, вторые входы которых соединены с выходами соответствующих блоков коммутации маски входов регистров выдачи группы, а выходы - со.входами соответствующих регистров вьщачи группы, третий выход регистра команд соединен с первым входом блока коммутации маски входных сигналов, вторым входом подключенного к выходу блока коммутации входных сигналов, а ходом - к третьему входу блока коммутации входов- блока памяти данных, первь1й и второй блока памяти данных соединены соответственно, со вторыми входами блоков коммутации входов первого и второго операнда, выходы, которых соединены соответственно с первым:- и вторым входами арифметикологического блока, введен блок регистров упаковки, причем первый.вход блока регистров упаковки соединен с третьим выходом регистра команд, второй вход - с выходом блока .коммутации входов блока па.мяти данных, а выход - со входом блока .памяти данных. На фиг. 1 представлена блок-схема предлагаемого устройства;, на фиг. 2 блок-схема блока регистров упаковки; на фиг. 3 ..и 4 - функциональные схемы . формирователя.входного сигнала.и регистра маски блока регистров, упаковки; на фиг. 5 - временная диаграмма работы узла синхронизации блока регистров упаковки.. Устройство содержит блок J декодирования команд, счетчик 2 команд, память 3 команд, регистр 4 .команд, блок 5 коммутации маски входных сигналов, блок 6 коммутации входов первого операнда, блок 7 коммутации .входов второго операнда,,блок 8 коммутации входов блока памяти данных,, блок 9 памяти данных, арифметико-логический блок (АЛБ) 10, регистр 11 результата, регистр 12 управления вьщачей, блок 13 коммутации входных .сигналов, дешифратор 14 регистра выдачи, блок 15 коммутации маски входов регистров выдачи, блок 16 формирования сигналов установки, регистры 17 вцЕ(ачи и блок 18 регистров упаковки. Блок 18- регистров . упаковки содерг жит узел 19 коммутации входов блока, регистр 20..упаковки, регистр 21 данных, регистр 22 маски и узел 23 синхронизации, включающий (фиг. 2) элемент ИЛИ 24, формирователи 25-27 входного

сигнала, элементы И 28-30, элемент НЕ 31 и генератор 32 импульсов.

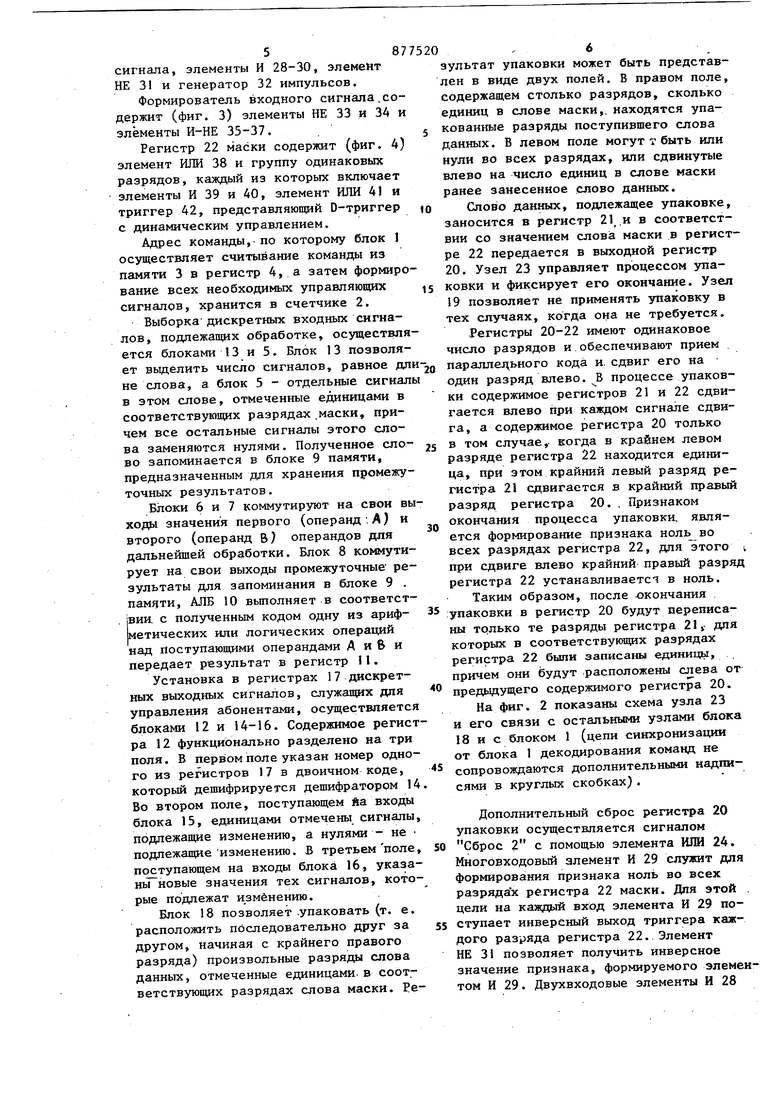

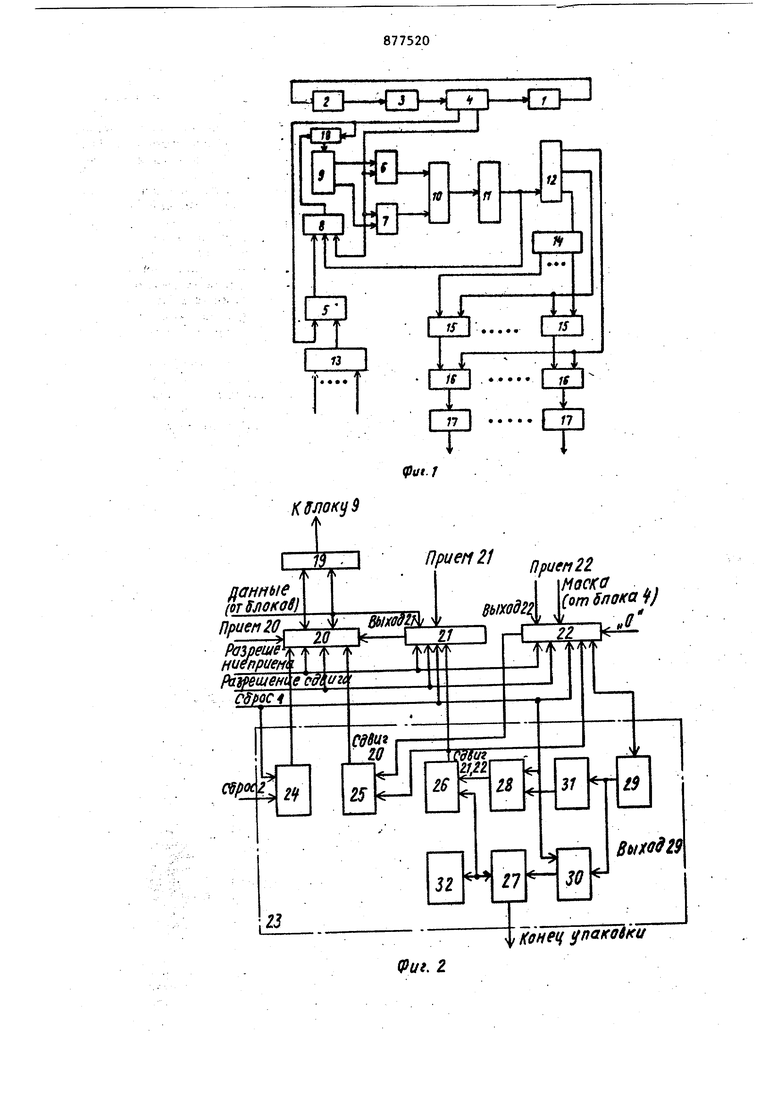

Формирователь входного сигнала,содержит (фиг. 3) элементы НЕ 33 и ЗА и элементы И-НЕ 35-37.

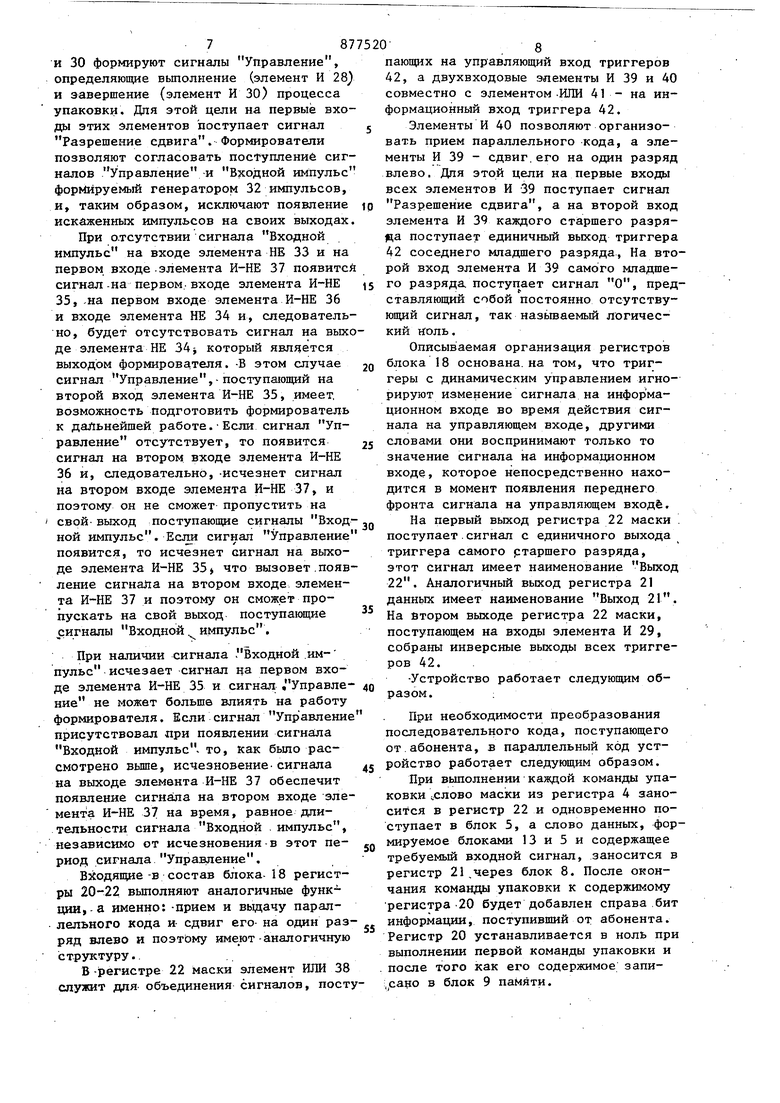

Регистр 22 маски содерткит (фиг. 4) элемент ИЛИ 38 и группу одинаковых разрядов, каждый из которых включает элементы И 39 и 40, элемент ИЛИ 41 и триггер 42, представляющий D-триггер с динамическим управлением.

Адрес команды, по которому блок 1 осуществляет считывание команды из памяти 3 в регистр 4, а затем формирование всех необходимых управляющих сигналов, хранится в счетчике 2.

Выборка дискретных входных сигналов, подлежавших обработке, осуществляется блоками 13 и 5. Блок 13 позволяет вьщелить число сигналов, равное дл не слова, а блок 5 - отдельные сигнал в этом слове, отмеченные единицами в соответствующих разрядах ,маски, причем все остальные сигналы этого слова заменяются нулями. Полученное слово запоминается в блоке 9 памяти, предназначенным для хранения промежуточных результатов. Блоки 6 и 7 коммутируют на свои вы хода значения первого (операнд . А) и второго (операнд В) операндов для дальнейшей обработки. Блок 8 коммутирует на свои выходы промежуточные результаты для запоминания в блоке 9 . памяти, АЛБ 10 вьтолняет в соответст. 1вии. с полученным кодом одну из арифметических или логических операций над поступающими операндами А и & и передает результат в регистр П. Установка в регистрах 17 дискретных выходных сигналов, служащих для управления абонентами, осуществляется блоками 12 и 14-16. Содержимое регист ра 12 функционально разделено на три поля. В первом поле указан номер одного из регистров 17 в двоичном коде, который дешифрируется дешифратором 14 Во втором поле, поступающем йа входы блока 15, единицами отмечены сигналы, подлежащие изменению, а нулями - не подлежащие изменению. В третьем поле, поступающем на входы блока 16, указаны новые значения тех сигналов, которые подлежат изменению. Блок 18 позволяет .упаковать (т. е. расположить последовательно друг за другом, начиная с крайнего правого разряда) произвольные разряды слова данных, отмеченные единицами, в соответствуюиц1х разрядах слова маски. Результат упаковки может быть представлен в виде двух полей. В правом поле, содержащем столько разрядов, сколько единиц в слове маски,, находятся упаковакнь е разряды поступившего слова данных. В левом поле могут т быть или нули во всех разрядах, или сдвинутые влево на число единиц в слове маски ранее занесенное слово данных.

Слово данных, подлежащее упаковке, заносится в регистр 21.и в соответствии со значением слова маски в регистре 22 передается в выходной регистр 20 Узел 23 управляет процессом упаковки и фиксирует его окончание. Узел 19 позволяет не применять упаковку в тех случаях, когда она не требуется.

Регистры 20-22 имеют одинаковое число разрядов и обеспечивают прием параллел ьного кода и. сдвиг его на один разряд влево.В процессе упаковки содержимое регистров 21 и 22 сдвигается влево при каждом сигнале сдвига, а содержимое регистра 20 только в том случае, когда в крайнем левом разряде регистра 22 находится единица, при этом крайний левый разряд регистра 21 сдвигается в крайний правый разряд регистра 20. . Признаком окончания процесса упаковки, является формирование признака ноль во всех разрядах регистра 22, для этого Ч при сдвиге влево крайний правый разряд регистра 22 устанавливаетст в ноль. Таким образом, после окончания упаковки в регистр 20 будут переписаны только те разряды регистра 21f для которых в соответствующих разрядах регистра 22 были записаны единицы, причем они будут расположены слева от предыдущего содержимого регистра 20. На фиг. 2 показаны схема узла 23 и его связи с остальными узлами блока 18 и с блоком 1 (цепи синхронизации от блока 1 декодирования команд не сопровождаются дополнительными надписями в круглых скобках). Дополнительный сброс регистра 20 упаковки осуществляется сигналом Сброс 2 с помощью элемента ИЛИ 24. Многбвходовый элемент И 29 служит для формирования признака ноль во всех разрядах регистра 22 маски. Для этой . цели на каждый вход элемента И 29 поступает инверсный выход триггера каждого разряда регистра 22. Элемент НЕ 31 позволяет получить инверсное значение признака, формируемого элементом И 29. Двухвходовые элементы И 28 8 И 30 формируют сигналы Управление, определяющие вьтолнение (элемент И 28) и завершение (элемент И 30) процесса упаковки. Для этой цели на первые вхо ды этих элементов поступает сигнал Разрешение сдвига. Формирователи позволяют согласовать поступление сиг налов Управление и Входной импульс формируемый генератором 32 импульсов, и, таким образом, исключают появление искаженных импульсов на своих выходах При отсутствии сигнала Входной импульс на входе элемента НЕ 33 и на первом входе-элемента И-НЕ 37 появитс сигнал -на первом., входе элемента И-НЕ 35, .на первом входе элемента И-НЕ 36 и входе элемента НЕ 34 и, следователь но, будет отсутствовать сигнал на вых де элемента НЕ 34 j который выходом формирователя. -В этом случае сигнал Управление,-поступающий на второй вход элемента И-НЕ 35, имеет, возможность подготовить формирователь к дальнейшей работе.-Если сигнал Управление отсутствует, то появится сигнал на втором входе элемента И-НЕ 36 и, следовательно, -исчезнет сигнал на втором входе элемента И-НЕ 37, и поэтому он не сможет пропустить на свой-выход поступающие сигналы Вход ной импульс. Если сигнал Управление появится, то исчезнет сигнал на выходе элемента И-НЕ 35) что вызовет.появ ление сигнала на втором входе, элемента И-НЕ 37 и поэтому он сможет пропускать на свой выход поступающие сигналы Входной импульс, При наличии сигнала Входной импульс исчезает сигнал на первом входе элемента И-НЕ 35 и сигнал « Управление не может больше влиять на работу формирователя. Если сигнал Управление присутствовал при появлении сигнала Входной импульс, то, как бьшо рассмотрено выше, исчезновение-сигнала на выходе элемента И-НЕ 37 обеспечит появление сигнала иа втором входе элемента И-НЕ 37 на время, равное длительности сигнала Входной импульс, независимо от исчезновения в этот период сигнала Управление. Входящие -в состав блока- 18 регистры 20-22 выполняют аналогичные функции, -а именно:-прием и вьщачу параллельного кода и сдвиг его- на один разряд влево и поэтому имеют -аналогичную структуру. Б -регистре 22 маски элемент ИЛИ 38 служит дпя объединения сигналов, посту пающих на управляющий вход триггеров 42, а двухвходовые элементы И 39 и 40 совместно с элементом-ИЛИ 41 - на информационный вход триггера 42. Элементы И 40 позволяют организовать прием параллельного кода, а элементы И 39 - сдвиг.его на один разряд влево. Дпя этой цели на первые входы всех элементов И 39 поступает сигнал Разрешение сдвига, а на второй вход элемента И 39 каждого старшего разряда поступает единичный выход триггера 42 соседнего младшего разряда, На второй вход элемента И 39 самого младшего разряда поступает сигнал О, представляющий собой постоянно отсутствующий сигнал, так назьгааемый логический ноль. Описыв аемая организация регистров блока 18 основана, на том, что триггеры с динамическим управлением игнорируют изменение сигнала на информационном входе во время действия сигнала на управляющем входе, другими словами они воспринимают только то значение сигнала на информационном входе, которое непосредственно находится в момент появления переднего фронта сигнала на управляющем входе. На первый выход регистра 22 маски . поступает.сигнал с единичного выхода триггера самого ртаршего разряда, этот сигнал имеет наименование Выход 22. Аналогичный выход регистра 21 данньк имеет наименование Выход 21. На втором выходе регистра 22 маски, поступающем на входы элемента И 29, собраны инверсные выходы всех триггеров 42. -Устройство работает следующим образом. : При необходимости преобразования последовательного кода, поступающего от.абонента, в параллельный код устройство работает следующим образом. При выполнении каждой команды упаковки слово маски из регистра 4 заносится в регистр 22 и одновременно поступает в блок 5, а слово данных, формируемое блоками 13 и 5 и содержащее требуемый входной сигнал, заносится в регистр 21,через блок 8. После окончания команды упаковки к содержимому регистра 20 будет добавлен справа бит информации, поступивший от абонента. Регистр 20 устанавливается в ноль при выполнении первой команды упаковки и после того как его содержимое запи сано в блок 9 памяти. При необходимости сформировать .одно слово данных из полей, находящихся в разных словах, например, для /занесения в регистр 12, устройство рабогтает следуюпщм образом. При выполнении первой команды упаковки регистр 20 устанавливается .в ноль., в регистр 22 .поступает слово маски из регистра 4, а в регистр 21 слово данных, содержащее первое поле из блока 9 памяти через блок 6, АЛБ 10, регистр 11 и блок 8. Слово маски содержит единицы только в тех разрядах, которые надо выделить .из слова данных. После выполнения этой команды в регистре 20 будет находиться первое поле. При выполнении последующих команд упаковки регистр 20 не устанавливается в .ноль и поэтому после второй команды он будет содержать два поля, а послетретьей команды - три поля. Затем содержимое регистра 20 запоминается в блоке 9 памяти, а оттуда поступает в регистр 12 для выдачи с помощью блоков 14-17 управляющих сигналов к абоненту. Работу узла 23 рассмотрим на конкретном, примере. Пусть необходимо сформировать одно слово данных из полей, находящихся в трех разных словах данных. Для удобст ва принимаем, что все слова состоят и четырех бит. В каждом исходном слове данных единицей в соответствующем раз ряде слова маски отмечены разряды, вы бираемые для упаковки. Пусть исходные слова данных и маски заданы в таком виде:; Первое слово данных 1101 Первое слово маски 0100 Второе слово данных 0101 Второе слово маски 1001 Третье слово данных 1001 Третье слово маски 0010 В процессе упаковки последовательн расположенные разряды каждого последующего слова данных должны располагаться справа от выбранных разрядов .предыдущего слова данных. Таким образом, искомое .слово данных должна имет вид 1010. . В начале каждой команды упаковки происходит занесение слов данных и маски в соответствующие регистры блока упаковки. Для этой цели в блоке 1 формируются сигналы Разрешение приема, Данные и Маска, которые обе спечивают поступление информации на информационный вход триггеров регист0ров и сигналы .прием 21 и Прием 22, которые, поступая на управлякицие входы этих триггеров, обеспечивают занесение в них поступающей информации. Так как первое слово данных содержит единицу в крайнем левом разряде, то по переднему фронту сигнала Прием 21 устанавливается сигнал Выход 21. Только при вьтолнении первой команды упаковки в блоке 1 .будет сформирован сигнал Сброс 2, который установит в нулевое состояние все триггеры регистра 20 упаковки. После снятия названных выше сигналов блок 1 устанавливает сигнал Разрешение сдвига, который подготавливает цепи сдвига влево в регистрах блока регистров упаковки и запускает его узед синхронизации. Так как исходное слово маски не содержит нули во всех разрядах, то сигнал, на выходе элемента И 29 (фиг. 2) отсутствует и, следовательно, произойдет совпадение сигналов только на входах элемента И 28, что вызовет .появление, сигнала Управление, на его выходе. Поскольку поступление.сигнала Разрешение сдвига совпало с наличием сигнала Входной импульс, формируемого генератрром 32, .то только следующий импульс генератора 32 сформирует первый сигнал Сдвиг 21 и 22 на выходе формирователя 26.,Во время действия этого сигнала, произойдет ус- тановка сигнала Выход 22,. однако формирователь 25 сформирует сигнал Сдвиг 20 только во время действия второго сигнала Сдвиг 21 и 22. Во время действия второго сигнала Сдвиг 21 и 22 исчезнут сигналы Выход 21 и Выход 22 и установится сигнал Выход 29, что вызовет снятие сигнала Управление для формироватеЛЯ 26 и появление сигнала Управление для формирователя 27. Тем не менее благодаря использованию триггеров с динамическим управлением в крайний правый разряд регистра 20 будет записано предшествующее, т. е, единичное значение сигнала Выход 21, а благодаря использованию формирователей не произойдет укорочение сигнала Сдвиг , 20 и сигнал Конец будет -сформирован только следующим импульсом генератора 32. Таким образом, после выполнения первой команды упаковки в регистре 20 будет содержаться код 0001. При выполнении второй команды упаковки по сигналу Прием 22 произойде установка сигнала Выкод -22 и снятие сигнала Выход 29, и в соответствии со значением слова маски -будат сформировано четыре сигнала- Сдвиг 2 и 22 и два сигнала. Сдвиг 20, которые Б соответствии, со значением.сигнала Вьйсод 21 установят в. регистре 20 упаковки код 0101. В nporpa iMax-обслуживания различных абонентов, операция упаковки встре чается довольно часто. Например, перекодировка форматов входных данных . (преобразование из последовательного кода в параллельный,-из зонного формата в упакованный и т. п.); подготовка- данных для вьздачи абоненту (пре образование из упакованного формата в зонный формат, добавление служебных полей и т. п. I вкутренние потребности программиста (компановка полей, . работа с таблицами и т. п.). При вьшолнении операции упаковки с помощью только одних программньгх , средств, как это выполняется в извест ном, требуется по крайней мере а-ри для каждого вновь - добавляемого поля: конъюнкция, сдвиг-, дизъюнкция, Б предлагаемом устройстве для этих же целей используется-только одна команда. Таким образом, устройство по сравнению с .известным позволяет уменьшит общее время выполнения программы обслуживания абонента, т/ е.; повысить . пропускную crtoco HocTb-устройства; уменьшить время отработки -входных сиг налов абонента,-т. е. увеличить скорость вьщачи ответной реакции - устройства к абоненту; сократить объем.памяти команд и число типов команд, Формула изобретения Устройство для сопряжения,.содержа щее регистр команд, первый выход которого через последовательно соединен ные блок декодирования -команд и счетчик команд подключен ко входу .памяти команд, выходом соединенной- со входом регистра команд, блок коммутации вход ных сигналов, входы которого являются соответствующими входами устройства-, блок коммутации маски входных сигнал . блок памяти данных, .блоки.коммутации входов первого и второго операндов, блок коммутации входов блока памяти данных, арифметико-логический блок. 0 соединенный выходом со входом регистра результата, -реги стр управления выдачей, дешифратор регистра-выдачи, . группу блоков коммутации маски входов регистров выдачи, группу блоков формирования сигналов установки, группу регистров выдачи, выходы которых являются соответств.у1ощими выходами устройства, причем второй выход регистра команд подключен к- первым входам блоков коммутации входов первого и второго операндов и блока коммутации входов блока памяти данных, вторым входом соединенного с выходом регистра .результата и входом регистра управления вьщачей, первый выход которого соединен со.входом дешифратора регистра выдачи, второй выход г с первыми входами блока коммутации маски входов регистров выдачи группы, вторыми входами подключенных к соответствующим выходам дешифратора регистра выдачи, а третий выход - с первыми входами блоков формирования сигналов установки группы, вторые входы которых соединены с выходаг4и соответствующих блоков коммутации маски входов регистров выдачи группы, а выходы - со входами, соответствующих регистров выдачи группы, третий выход регистра команд -соединен с первым входом блока коммутации маски вход- иых сигналов, вторым входом подключен-ного к выходу блока коммутации входных сигналов, а выходом т к третьему входу блока коммутации входов блока памяти данных первый и второй выходы блока памяти данных соединены соответственно со вторыми входами блока коммутации входов первого и второго операнда, выходы которых соединены соответственно с Первым и вторым входами арифметико-логического -блока, о т и ч а ю щ е ее я тем, что, с це.г лью повышения пропускной способности устройства, в него введен блок регистров упаковки, причем первый вход бло Ка регистров упаковки соединен с третьим выходом регистра команд, второй вход - с выходом блока коммутации входов блока памяти данных, а выход - со входом блока памяти данных. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3628325, кл. 340-172.5, опублик. 1972. 2. Патент Великобритании № 1.378.144, кл. G 06 F 3/00, опублик. 1970 (прототип) .

Кулаку 9

BMxoffmjL

-L

CSpocl

2f

Z3

I моска ..

.//.4

1

Ж-

I

/ K

/w

ffSui

w I

iO I

гш

g «J

flT

19

IB

31

Вы1ко919

KOi

Конец tfnoKo6Kt/

(Put, 2

Авторы

Даты

1981-10-30—Публикация

1980-01-03—Подача