1

: Изобретение относится к вычислительной технике и может быть использовано для вычисления значений логарифмической функции от двоичного аргумента.

По основному авт.св. № 593212 известно цифровое устройство содержащее регистры старших и младших разрядоз, блоки памяти, коммутатор, сумматор, выходной регистр, блок управления сдвигателем, причем первый выход регистра старших и выход регистра младагах разрядов соединены соответственно со входами первого и второго блоков памяти, выходы которых подключены соответственно к первому входу сумматора и первому входу коммутатора, выход которого подключен ко второму входу сумматора, первый выход ;которого соединен со входами выходного регистра и третьего блока Пс1мяти, выход третьего блока памяти подключен к первому входу сдвигателя, управляющий вход которого через знаковый триггер подключен к знаковому выходу сумматора, а второй - к выходу регистра младших разрядов, выход сдвигателя подключен ко второму входу .кока утатора, управляющие входы кото.рого подключены к выходам блока управления pTj .

Однако данное устройство имеет низкую точность вычисления функции.

Цель изобретения - повьвиение точности .

Поставленная цель достигается тем что устройство, по авт.св. 593212, дополнительно содержит два блока сравнения,причем первый и второй входы первого блока сравнения соединены соответственно со вторыми входами регистра старших разрядов и первого блока памяти, а выход - с третьим, входом сумматора, первый и второй входы второго блока сравнения подключены ко вторым выходам соответственно сумматора и, третьего блока памяти а выход - ко второму входу сдвигателя.

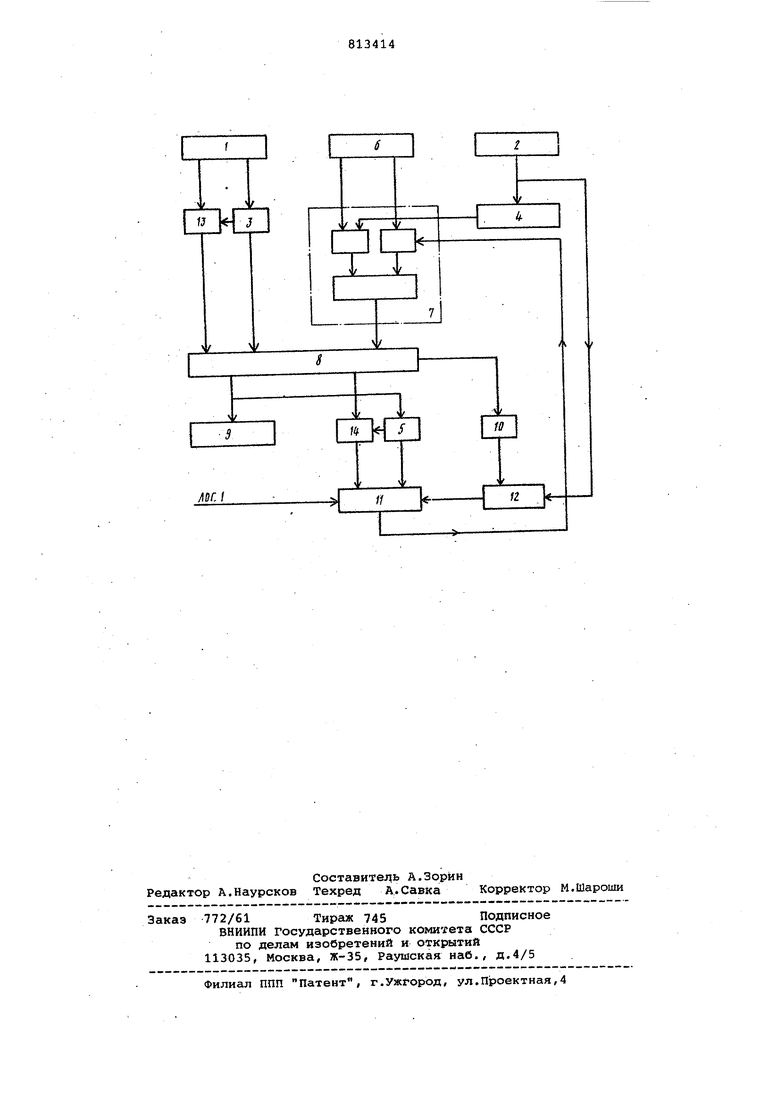

На чертеже представлена блок-схема устройства.

Устройство содержит регистры старших 1 и .младших 2 разрядов аргумента блоки 3-5 памяти, блок 6 управления, коммутатор 7, сумматор 8 выходноЛ регистр 9, триггер 10 числа, сдвига тель 11, блок 12 управления сдвигателем, блоки 13 и 14 сравнения. Вычисление двоичного логарифма от нормализованного аргумента V ( -я- V 1 ) производится в предлаг емом устройстве на основе соотноше ний i 092 09,2 (х+У 2) где X - число,образованное старшим разрядами аргументаУ; у - число, образованное младши разрядами аргумента V; К - чн1сло двоичных разрядов дл записи числа х ; ес(х у ОГ )--tog,x e«g( 2;; 2-при к.,, Jo Ji42 j-e;;2 где N - число двоичных разрядов дл записи аргумента) .2(( X ел 2 причем ix4i-2 а () + л(х),г где л(х) - фунедия абсолютной погреш ности аппроксимации логар ма прямой. Заметим, что л(х} 2 , а .log.x 2 (х- ) с точностью до 2 . Пусть oi 1092. ( )- log,jx;2° 2 где Р - целая часть числа А - дробная часть числа f - значение разности логарифмов . Обозначим Ь при 0 о Р IA , при о о . А р+ 2 2 ,при , /о р 2 2 ,при Qi О Пусть Z 2, , г ijb+ 1 - (р), где п - число двоичных разрядов, н обходимое для записи числа функция абсолютной погрешности апроксимации функции прямой. Заметим, что А (|2)) 2 ,а точностью до 2 , Устройство работает следующим о разом. На первом этапе работы устройс хранящиеся на регистрах старших 1 младших 2 разрядов аргумента знач ния X и у передаются соответствен на входда блоков 3 и 4 постоянной мяти, где хранятся таблицы мантис огарифмов старших и младших разрядов ргумента. В таблице, хранящейся в локе 3 постоянной памяти отсутствут два старших разряда значений-мантисс логарифмов. Значения второго, третьего и четвертого разрядов регистра 1 старших разрядов аргумента поступают на вход блока 13 сравнения, состоящего из элемента ИЛИ и сумматора, осуществляющего сложение числа, бразованного вторым, третьим и четвертым разрядами аргумента с кодом 001, если значение четвертого разряда регистра 1 старших разрядов аргумента не совпадает со значением, поступающим с выхода старшего разряда блока 3 постоянной памяти. В противном случае происходит сложение с нулем, не изменяющее входного числа. Блок 13 сравнения работает следующим образом. При несовпадении инверсивного значения четвертого разряда регистра 1 старших разрядов аргумента с значением старшего разряда числа, выбранного из первого блока 3 постоянной памяти, происходит увеличение на единицу числа, представленного инверсивным значением второго,третьего и четвертого разрядов аргумента.На выходе блока 13 сравнения получаем два старших разряда логарифма, образ званные двумя старшими разрядами суммы, вычисленной блоком 13 сравнения. С выхода блока 3 постоянной памяти снимаются значения мантиссы с отсутствую1дими двумя старшими разрядами. С выхода блока 4 постоянной памяти снимается значение мантиссы I - log ( Мантиссы логарифмов поступают на входы сугютатора 8, причем содержимое на выходе 4 блока постоянной памяти, равное мантиссе I log (-g)| / проходит через управляемый коммутатор 7, подключающий в этом такте ко входу сумматора 8 выход блока 4. На выходе сумматора 8 формируется согласно формулам значение J5 , которое передается на вход блока 5 постоянной памяти, где хранится таблица функции 2 с отсутствующими тремя старшими разрядами значений функции. Три старших разряда суммы с выхода сумматора 8 поступают на вход блока 14 сравнения, состоящего из элемента ИЛИ и сумматора. Значение на.выходе старшего разряда блока 5 постоянной памяти также поступает на вход блока 14 сравнения, котбрый осуществляет сложение кода 111 с числом, образованным инверсией трех старших разрядов суммы, поступающих с выхода сумматора 8, в случае, если значение .старшего разряда числа, выбранного из блока 5 постоянной памяти, не совпадает со значением инверсии третьего разряда суммы, поступающей из сумматора 8. В противном случае происходит сложение числа, образованного и версией трех старших разрядов суммы поступающей с выхода сумматора 8, с нулем/ не изменяющее значение этой инверсии. На выходе блока 14 сравнения получаем значение второго и третьего разряда функции 2 , образован ные двумя старшими разрядами суммы, полученной блоком 14 сравнения, С выхода блока 5 постоянной памяти снимаются значения функции 2f с отсутствующими тремя старшими разрядами. Таким образом, на выходе блоков 14 и 5 образуется значение функции 2 с отсутствующим старшим разря дом. Значение старшего разряда функции 2, принимается равным логической единице в силу выполнения неравенства для Z. Значение функции z 2 поступает на вход сдвигателя 11. Зна чение знакового разряда сумматора 8 запоминается на триггер 10. Блок 12 управления сдвигателем представляет собой комбинационную схему, подсчитывающую число нулевых разрядов слева до первого единичного разряда в регистре 2 младших разрядов аргумента и суммирующую это число со значением триггера 10, что дает значение требуемого числа сдвигов Р или Р + 1 в сдвигателе 11 для получения на его выходе значения 2 из поступающего на вход сдвигателя значения 2Р . Образованное на выходе сдвигателя число 2 через управляелвлй коммутатор 7 подключающий на втором этапе работы устройства ко входу сумматора 8 выходы сдвигателя 11, подается на сумматор, где происходит сложение значений 2° и поступающего на другие входы сумматора значения с выхода блока 3 и блока 13 сравнения. В результате сложения на сумматоре происходит формирование по исходной формуле значения мантиссы log,2.V, которое передается на вход выходного регистра 9. Таким образом,предлагаемое устройство преобразует нормешизованное значение аргумента V в значение мантиссы . При сохранении точности вычисления функции достигается экономия оборудования. Экономия информационной емкости блоков постоянной памяти естественно приводит к экономии оборудования. Так, при N 24 необходимая емкость первого блока постоянной памяти составит 8192 слов по 25 разрядов.Наиболее емкие биполярные блоки памяти в интегральном исполнении в настоящее время имеют емкость 256 слов по 4 бита. Количество корпусов интегральных ПЗУ, необходимых для реализации первого блока постоянной памяти в схеме основного изобретения составт ляет корпуса. Для предлагаемого устройству объем интегральных ПЗУ для первого блока постоянной памяти составляет корпуса. Выигрьаи на первом блоке постоянной памяти равен 32 корпуса и при затратах в 2 корпуса, чистый выиг--: рьни - 30 корпусов. Емкость интегральных схем третьего блока постоянной памяти составляет 4096. слов по 13 разрядов. При реализации по схеме основного изобретения количество интегральных ПЗУ составляет 64 корпуса. Для предлагаемой схемы для тех же требуется 48 корпусов, т.е. получаем выигрыш 16 корпусов при затратах максимум двух корпусов интегральных схем. Дополнительный вьаигрьш получается за счет исключаемЁ1Х, впредлагаемом устройстве, элементов или для объединения 32 выходов старшего разряда в первом блоке постоянной памяти. Это составляет порядка 4 корпусов для первого блока постоянной памяти и 2 корпусов для второго блока постоянной памяти.Общий чистый выигрыш составляет около 30+14+2 50 корпусов интегральных схем. Соответственно снижается потребляемая мсвцность и увеличивается надежность устройства.о Форнчула изобретения Цифровое устройство для логарифмирования двоичных чисел, по авт. св. № 593212, отличающеес я тем, что, с целью повышения точности, оно содержит два блока сравнения, причем первый и второй входы первого блока сравнения соединены соответственно со вторыми входами регистра старяяих разрядов и первого блока памяти, а выход - с третьим входом сумматора, первый и второй входы второго блока сравнения подключены ко вторым выходам соответственно сумматора и третьего блока памяти, а выход - ко второму входу сдвигателя. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 593212, кл.С 06 F 7/38, 1977 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования двоичных чисел | 2015 |

|

RU2614932C1 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Устройство для логарифмирования массивов двоичных чисел | 1979 |

|

SU926654A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1976 |

|

SU593212A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для вычисления показательной функции | 1988 |

|

SU1536376A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

Авторы

Даты

1981-03-15—Публикация

1979-02-16—Подача