1

Изобретение относится к вычислительной технике и цифровой автоматике и может быть исподьзовано для построения регистров в цифровых вычислительных машинах и приборах дискретного действия.

Известны схемы регистров сдвига, выполненные на логических элементах И.-НЕ, каждый разряд которых состоит из основного и вспомогательного триггера и элементов, с помощью которых осуществляется стробирование продвижения, информации (вентили, управляющие триггеры и т. д.). В Зависимости от варианта построения подобные разряды- регистра содержат от 8 до 5 элементов И-НЕ 1.

Недостатком известных регистров сдвига является наличие большого количества элементов в одном разряде.

Известен реверсивный регистр сдвига, разряд которого содержит два коммутационных триггера, триггер памяти и логический элемент И-НЕ 2.

Недостаток данного регистра - большое количество элементов И-НЕ (в одном разряде 7), а также невозможность установа регистра в «1 при 4-х управляющих цепях: «Сдвиг вправо. «Сдвиг влево, «Такт, «Сброс.

Наиболее близким по технической сущности и схемному решению к данному изобретению является сдвиговый регистр, содержащий в каждом разряде регистра элементы памяти, каждый из которых состоит из четырех элементов И-НЕ, входы которых подключены к соответствующим тактовым шинам, а первый и третий элементы И-НЕ соединены соответственно со вторым и чет10вертым элементами И-НЕ триггерной связью, и первый входной элемент И-НЕ, соединенный триггерной связью, с первым элементом И-НЕ первого элемента памяти 3.

Недостаток указанного регистра - большое количество элементов в каждом разря15де регистра (в одном разряде 5 элементов И-НЕ).

Цель изобретения - упрощение схемы регистра.

Поставленная цель достигается тем, что регистр содержит второй входной элемент

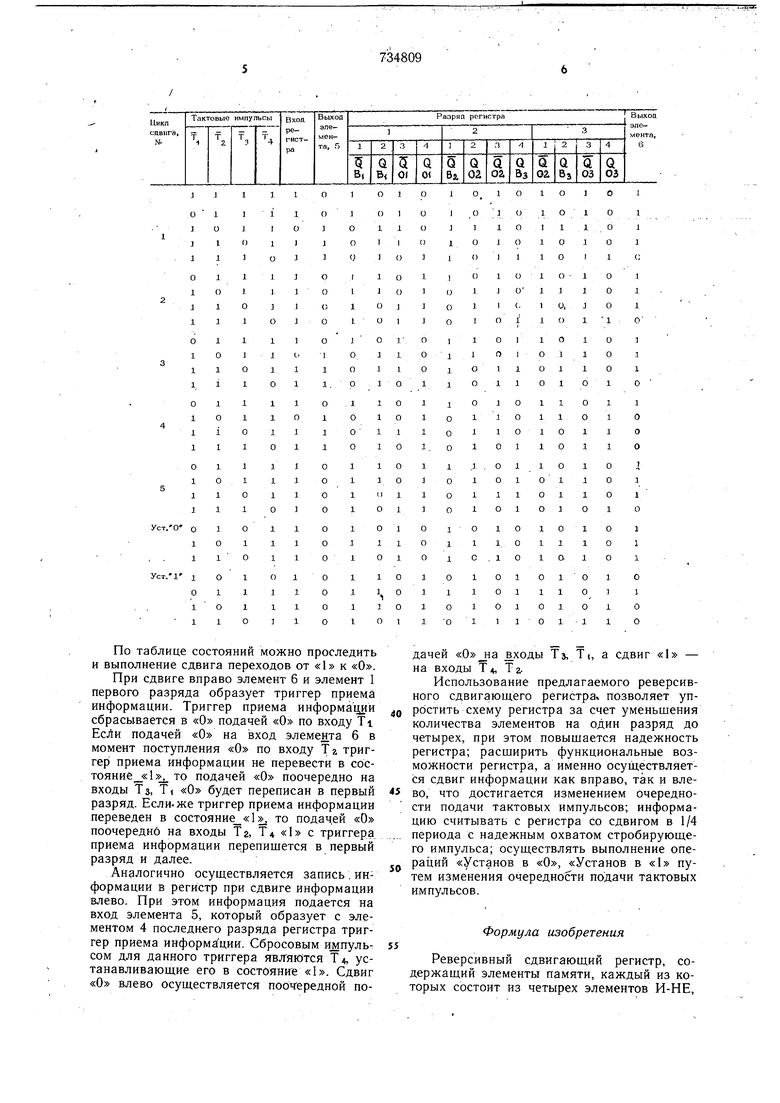

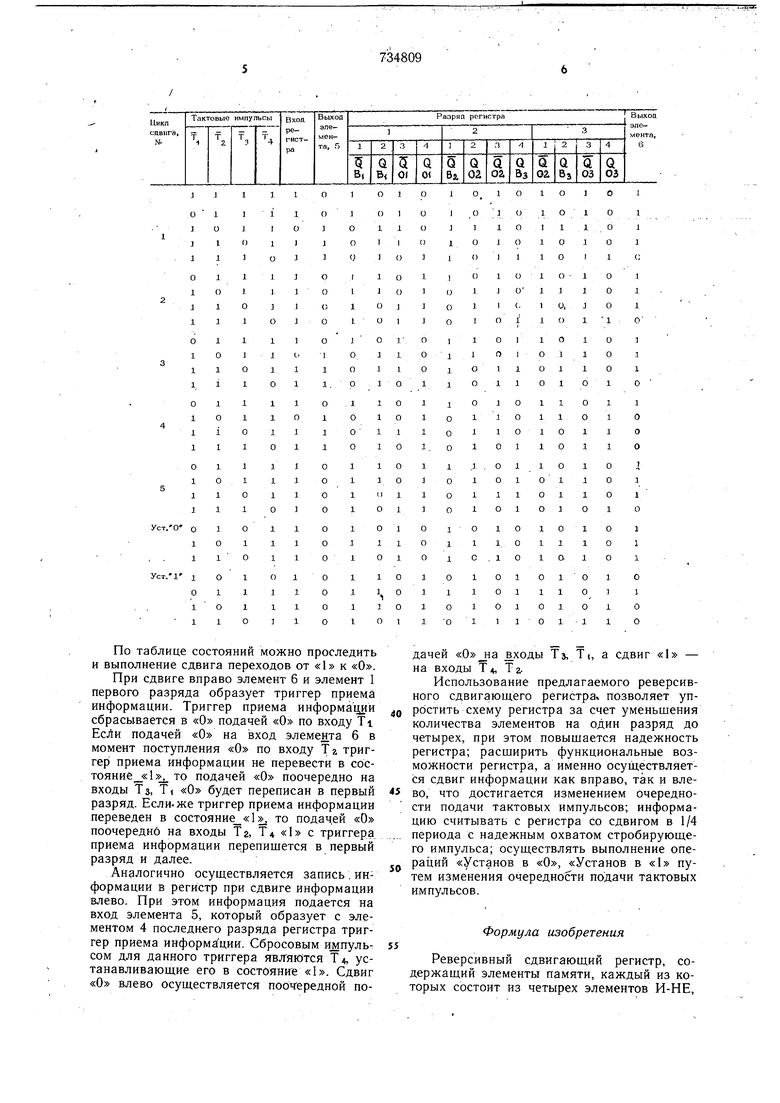

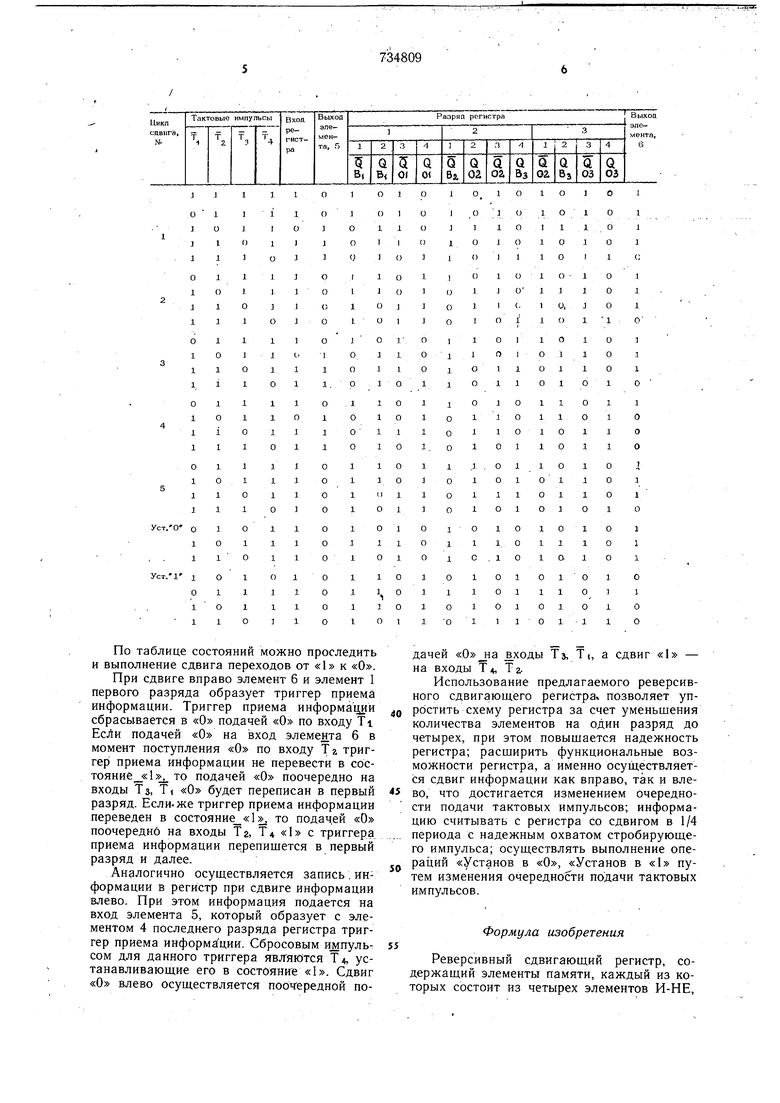

20 И-НЕ, соединенный триггерной связью с четвертым элементом И-НЕ последнего элемента памяти, второй и третий элементы И-НЕ каждого элемента памяти соединены триггерной связью, а четвертый элемент И-НЕ Каждого элемента памяти, кроме последнего, соединен триггерной связью с первым элет ментом И-НЕ последующего Элемента памяти. . ; .-,.На чертеже представлена схема п-разрядного рев ерсивного сдвигающего регистра. Реверсивный сдвигающий регистр содержит п разрядов, каждый из которых состоит из четырех логических элементов И-НЕ 1, 2, 3, 4,образующих основной (элементы 1, 2) и дополнительный (элементы 3, 4) триггеры, и входной элемент приема информации на выходе регистра 5, и элемент приема информации на входе регистра 6. Элементы 1 и 2, 3 и 4, 2 и 3, 4-й предыдущего и 1-й последующего разряда, а также 6-й и 1-й первого разряда, 5-й и 4-й п-го разряда соединены между собой попарно триггерными связями. На входы элементов 1, 2, 3, 4 подается одна из последовательн остей так-товых импульсов соответственно Ti, Тг, Тз, Т4,последовательность подачи которых определяет направление сдвига информации в регистре. Для сдвига вправо «0 подается поочередно на входы Т1,,Т4г Д-1Я сдвига влево - на входы Т4, Тз, Т г, Ti. Установ регистра в «О осуществляется путем одновременной подачи сигнала «О по вхрда Тг, Тз, установ в «1 - по входам Тг, Т4. В результате выполнения команды «Установ в «О на выходе нечетных элементов регистра устанавливается «1, а на выходе четных - «О. В результате выполнения команды «Установ в «1 на выходе нечетных элементов устанавливается «О, а на выходе четных - «1. При сдвиге информации вправо для записи в первый разряд «1 на вход элемента б подается «О во время воздействия «О по входу Та. Для записи в первый разряд «О на вход элемента 6 в течение всего цикла сдвиFa подается «1. На вход элемента 5 при сдвиге вправо подаются тактовые импульсы Т,. При сдвиге влево для записи «О в последний разряд регистра на вход элемента 5 подается «О во время воздействия «О по входу Тз, для записи «1 на вход элемента 5 в течение всего цикла сдвига подается «1. На вход элемента 6 при сдаиге влево подаются тактовые импульсы Т 4. Подача на входы Jлeмeнтoв 5, 6 входного сигнала или Ть Т4 в режиме реверсирования может осуществляться, например, с помощью электронного коммутатора. При записи в разряды регистра одинаковой информации (одних «О или «1) «О и «1 на выходах элементов чередуются и каждая «1 на выходе элемента поддерживается двумя «О на его входе с выходов двух соседних элементов г1одача «О поочередно на входы Ti, Тг, Тз, Т4 приводит к изменению информации на выходе только на время воздействия тактового импульса, так как «О по входу тактовых импульсов переводится в «1 только один из «О, удерживающих «1 на выходе; По окончанию воздействия fcO по входу тактовых импульсов на входах элемента установятся «1, а на выходе этого элемента восстановится «О. На границе перехода ОТ «о к «1 в (нечетном и четдвух смежных элементах ном) устанавливается 1 . Например, на выходе элементов 3 и 4 первого разряда (см. таблицу состояний цикл 2, Тз 0). При этом «1 поддерживается сигналом «О лищь от одного смежного элемента: «1 на выходе элемента 3 сигналом «О с выхода .элемента 2, «1 на выходе элемента 4 - «О с выхода первого элемента следующего разряда. В этом случае в зависимости от того, какой придет очередной тактовый импульс, зависит что осуществится - сдвиг перехода от «О к «1 вправо или влево. Действительно, если поступит «О на вход TI элемента 1 второго разряда, то на его выходе сигнал изменится с «О на «1, что вызовет появление «О на выходе элемента 4 первого разряда, который обеспечит сох- , ранение «1 на выходе элемента 1 второго разряда и после окончания «О на входе Ti. Тем самым переход от «О к «1 сместится вправо на два элемента. Аналогично, в случае прихода «О по входу Т г сигнал на выходе элемента 2 первого разряда изменится с «.О на «1, появится «О на выходе элемента 3 и зафиксирует «1 на выходе элемента 2. Переход от «О к «1 сместится влево.

По таблице состояний можно проследить и выполнение сдвига переходов от «1 к «О.

При сдвиге вправо элемент 6 и элемент 1 первого разряда образует триггер приема информации. Триггер приема информации сбрасывается в «О подачей «О по входу TI ЕсЛи подачей «О на вход элемента 6 в момент поступления «О по входу Т г триггер приема информации не перевести в состояние «1 то подачей «О поочередно на входы Тз, TI «О будет переписан в первый разряд. Если, же триггер приема информации переведен в состояние «1 то подачей «О поочереднб на входы Т г, Т 4 «1 с триггера приема информации перепишется в первый разряд и далее.

Аналогично осуществляется запись . ин формации в регистр при сдвиге информации влево. При этом информация подается на вход элемента 5, который образует с элементом 4 последнего разряда регистра триггер приема информации. Сбросовым и пульсом для данного триггера явл яются Т, устанавливающие его в состояние «1. Сдвиг «О влево осуществляется поочередной подачей моды Тз, Т(, а сдвиг «1 - на входы Т+, ТаИспользование предлагаемого реверсивного сдвигающего регистра, позволяет упростить схему регистра за счет уменьшения количества элементов на один разряд до четырех, при этом повышается надежность регистра; расширить функциональные возможности регистра, а именно осу1дествляется сдвиг информации как вправо, так и влево, что достигается изменением очередности подачи тактовых импульсов; информацию считывать с регистра со сдвигом в 1/4 периода с надежным охватом стробируюш,его импульса; осуществлять выполнение операций «УСТЭНОВ в «О, «Установ в «1 путем изменения очередности подачи тактовых импульсов.

Формула изобретения

Реверсивный сдвигающий регистр, содержащий элементы памяти, каждый из которых состоит ИЗ четырех элементов И-НЕ,

входы которых подключены к соответствующим тактовым шинам, а первый и третий элементы И-НЕ соединены соответственно со вторым и четвертым элементами И-НЕ триггерной связью, и первый входной элемент И-НЕ, соединенный триггерной связью с первым элементом И-НЕ первого элемента памяти, отличающийся тем, что, с целью упрощения регистра, он содержит второй входной элемент И-НЕ, соединенный триггерной связью с четвертым элементом И-НЕ последнего элемента памяти, второй и третий элементы И-НЕ каждого элемента памяти соединены триггерной связью, а четвертый элемент И-НЕ каждого элемента памяти, кроме последнего, соединен триггерной связью с первым элементом И-НЕ последующего элемента памяти.

JИсточники информации,

принятые во внимание при экспертизе

1.Букреев И. Н. и др. Микроэлектронные схемы цифровых устройств. М., 1975,

с. 136-148.

2.Авторское свидетельство СССР « № 285054, кл. G 11 С 19/00, 1970.

3.Авторское свидетельство СССР

№ 343307, кл. G 11 С 19/00, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Реверсивный регистр сдвига | 1974 |

|

SU593317A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| Ячейка памяти для регистра сдвига | 1979 |

|

SU851495A1 |

| Система для передачи и приема цифровой информации с согласованием скорости | 1989 |

|

SU1755385A1 |

| Устройство цикловой синхронизации | 1988 |

|

SU1730733A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2016 |

|

RU2626338C1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1642527A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| Устройство для подключения абонента к общей магистрали | 1988 |

|

SU1583936A1 |

.i-ij рог ряЭj2-й p.

, Вма-..I йых.А ,0 Stac.i uux,o 6u,x.i e«a,fl ых J бых,0 SuxJ 6ых,0. .

Авторы

Даты

1980-05-15—Публикация

1977-05-10—Подача