1

Изобретение относится к радиоэлектронной и вычислительной технике, в частности, к технике проверки электрического монтажа различных радиоэлектронных узлов и блоков, содержащих большое количество монтажных точек.

Известны устройства для автоматической проверки монтажа, работающие по принципу выявления и распознавания всех монтажных соедииений, имеющихся фактически в проверяемом изделии, и сравнения найденных связей с эталоном, записанным на перфоленте.

Одно из известных устройств для автоматической проверки монтажа содержит блок управления, связанный с коммутатором, блоки анализа, дешифрации адреса, печати и перфорации, ввода информации и предварительной обработки 1.

Основным недостатком данного устройства является медленность поиска точек, обладающих заданным признаком, т. е. в этом устройстве отсутствует узел группового поиска. Поэтому такое устройство неприменимо для контроля узлов, содержащих большое количество (десятки тысяч) монтажных точек.

Другое известное устройство для автоматической проверки монтажа содержит последовательно соединенные коммутатор подключения контрольных точек, регистр, дешифратор, блок анализа, схему сравнения, блок смены

2

адресов, блок ввода, блок вывода и п. ступеней последовательно соединенных распределителя импульсов, регистра, дешифратора и коммутатора опроса 2.

Даиное устройство содержит схему ступенчатого группового поиска, благодаря чему операция поиска точек значительно ускоряется. В устройстве имеется также блок преобразования кодов адресов, который позволяет выводить информацию в заданной этим преобразователем адресной системе (соответствующей адресной системе конкретного проверяемого изделия). Иедостатками этого устройства являются

невозможность смены выходной адресной системы без переделки блока преобразования кодов адресов, а также пробивка на иерфоленте и ввод информации не в адресах проверяемого изделия, а в условных машинных адресах устройства, что затрудняет подготовку исходных иерфолент для первых образцов изделий.

Иаиболее близким техническим решением к данному изобретению является устройство для

автоматической проверки моитажа, содержащее блок управления, блок группового поиска, коммутатор, блок преобразования кодов адресов, блок анализа, блок ввода-вывода, блок памяти программы, блок иамяти иараметров

модификации адресной системы счисления и

счетчик адресов признака, причем выход п вход блока памяти программы соедииеиы соотвсгствеипо с псрвгзтми входом и выходом блока управлеиия, вторые выход и вход которого соедипены соответственно с первыми входом и выходом блока группового поиска, третий выход блока управления соединен со входом счетчика адресов признака, четвертый, пятый, шестой и седьмой выходы блока управлеиия соединены с управляющими входами блока иреобразования кодов адресов, блока анализа, блока ввода-вывода п блока памяти параметров модификации адресной системы счисления, второй выход блока груииового иопска соедииен с третьим входом блока управления и с иервым входом коммутатора, выход которого является первым выходом устройства, исрвые выход и вход блока преобразования кодов адресов соединены соответственно со входом и выходом блока памяти нараметров модификации адресной системы счисления, второй выход блока преобразования кодов адресов соединен с первыми входами блока анализа н блока ввода-вывода, выход блока а ализа соедииен со вторым входом блока ввода-вывода, первый выход которого является вторым выходом устройства, а третий вход - входом устройства 3.

В этом устройстве можно более оперативно менять программу кодоиреобразования адресов при переходе от контроля одного вида изделия к другому, а выход информации для одного проверяемого изделия производится в одиой фиксированной адресной системе, что неудобно в случаях, когда в одном изделии имеются несколько адресных систем.

Другим недостатком этого устройства является ввод ииформацип не в реальных, а в условных адресах, что обусловлено конструкцией и работой блока преобразования кодов адресов лишь в одном (обратном) нанравлении.

Общим недостатком указанных устройств является отсутствие четкого критерия, позволяющего разграничивать наличие или отсутствие монтажной (проводной) связи между точками. В результате этого если, ианример, в проверяемом изделии между двумя цепями с чисто проводной связью имеется связь через резистор, то в некоторых случаях, при малой величине сопротивления резистора, эти две цепи могут быть нриияты устройством за одну. Для проверки монтажа таких изделий имеющиеся в них резисторы нужно или выпаивать, или закорачивать, что значительио снижает эффективность автоматической проверки.

Целью изобретения является расширение функциональных возможиостей устройства за счет организации контроля как проводных ценей, так и резистивных связей между проводными цепями, а также за счет организации ввода и вывода информации в реальных адресах.

Поставленная цель изобретения достигается тем, что в устройство введены блок памяти приоритетных адресов, регистр адреса признака, блок выдачи адреса признака, дискриминатор сопротивления связей, регистр входного адреса и регистр машинного адреса, причем восьмой, девятый и десятый и одиннадцатый выходы блока управления соединены с управляющими входами блока памяти приоритетных адресов, регистра адреса признака, блока выдачи адреса признака и регистра ма10 илиииого адреса, выход блока памяти соединен с первым входом регистра адреса признака, второй вход которого соединен с выходом блока группового поиска, а выход - с первыми входами блока выдачи адреса иризнака и

15 регистра машиниого адреса и со вторым входом блока 1-руниового поиска, выход счетчика адресов признака соеднпен со вторым входом блока выдачи адреса признака, выход котороio соедипеи со вторым входом коммутатора и

0 с четвертым входом блока управления, второй выход коммутатора соединен со входом дискриминатора сопротивления связей, первый выход которого соединен с пятым входом блока управления, а второй выход - со вторым

5 входом блока анализа и с четвертым входом блока ввода-вывода, выход блока группового поиска соединен со вторым входом регистра машинного адреса, выход которого соединен со вторым входом блока преобразования кодов адресов, третий выход блока преобразования кодов адресов соединен со входом блока памяти приоритетных адресов, второй выход блока ввода-вывода соединен со входом регистра входного адреса, выход которого сое5 динеи с третьими входами блока анализа и блока преобразования кодов адресов, третий выход блока ввода -вывода соединен со вторым входом блока памяти иараметров модификации адресной системы счисления.

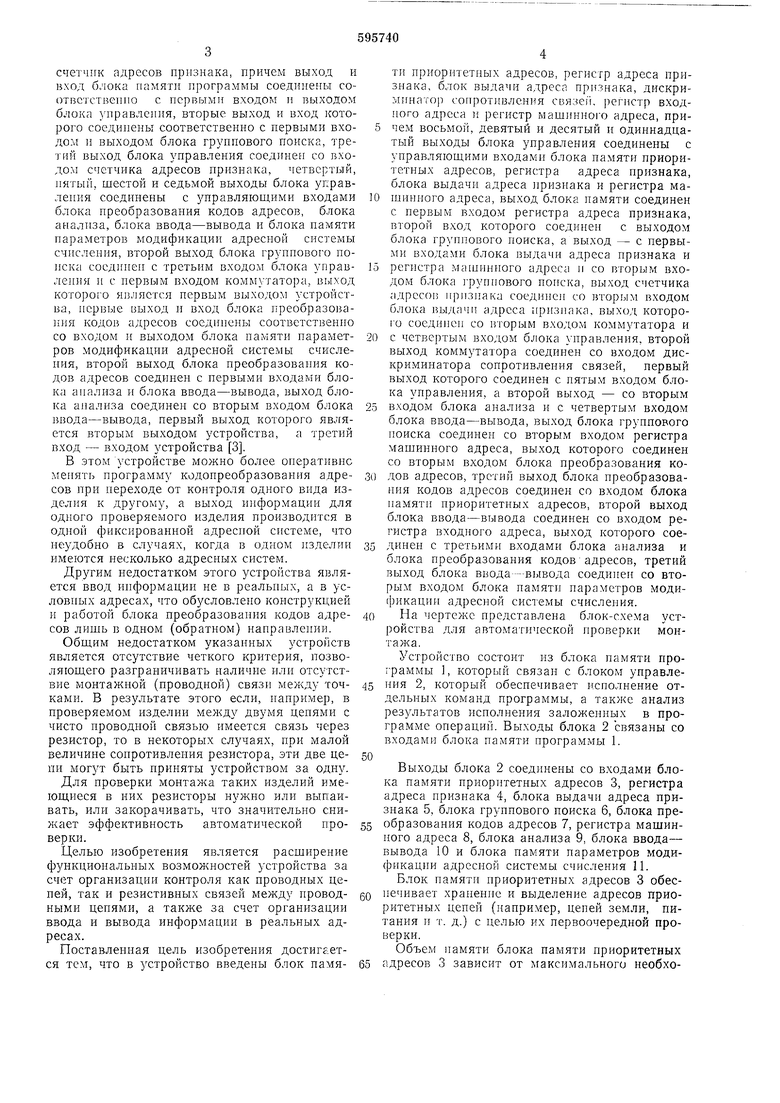

0 На чертеже нредставлена блок-схема устройства для автоматической ироверки монтажа.

Устройство состоит из блока памяти программы 1, которЕлй связан с блоком унравле5 ПИЯ 2, который обеспечивает исполнение отдельных команд программы, а также анализ результатов исполнения заложеииых в программе операций. Выходы блока 2 связаны со входами блока памяти программы 1.

Выходы блока 2 соединены со входами блока памяти приоритетных адресов 3, регистра адреса иризнака 4, блока выдачи адреса признака 5, блока грунпового поиска 6, блока пре5 образования кодов адресов 7, регистра машинного адреса 8, блока анализа 9, блока ввода- вывода 10 и блока памяти параметров модификации адресной системы счисления И. Блок памяти приоритетных адресов 3 обес0 печивает хранение и выделение адресов приоритетных цепей (например, цепей земли, питания и т. д.) с целью их первоочередной проверки. Объем памяти блока памяти приоритетных

адресов 3 зависит от максимального необходнмого количества приоритетных nerieii проверяемого изделия.

Регистр адреса признака 4 и блок выдачи адреса признака 5 служат для выполнения программы выявления резистивных связей между цепями проводных связей и первоочередной проверки приоритетных цепей.

Блок группового поиска 6 предназначен для нахождения адресов точек проверяемого монтажа изделия, в которых присутствует заданный признак (положительный потенциал).

Для обратного преобразования кодов машинных адресов в табличные (реальные) адреса точек проверяемого монтажа и прямого преобразования кодов табличных адресов в машинные - предназначен блок преобразования кодов адресов 7.

Регистр машинного адреса 8 является буферным регистром для хранения кодов адресов, подлежаш.их прямому преобразованию.

Блок анализа 9 предназначен для анализа правильности проверяемых связей и номиналов сопротивлений резисторов путем сравнения адресов найденных точек с адресами, вводимыми с контрольной перфоленты. Выдача данных из блока ввода-вывода и ввод адресов в него производится в реальных адресах проверяемого изделия.

Блок памяти параметров модификации адресной системы счисления И служит для хранения кодов адресов точек, в которых происходит изменение адресной системы счисления и соответствуюш,их этой системе модулей счета.

Выходы блока памяти приоритетных адресов 3 соединены со входами регистра адреса признака 4, другие входы которого соединены с выходами блока группового поиска 6. Выходы регистра 4 соединены с выходами блока выдачи адреса признака, блока группового поиска б и регистра машинного адреса 8. Вторые входы блока 5 связаны с выходами счетчика адресов нризнака 12, счетный вход которого связан с уцравляюш,им выходом узла центрального управления.

Выходы блока 5 соединены с выходами коммутатора 13 и блока управления 2. Коммутатор 13 предназначен для подключения опрашиваемых цепей объекта проверки 14 к дискриминатору сопротивлений связей 15.

Выходы блока группового поиска 6 соединены с входами коммутатора 13 регистра машинного адреса 8, блока 2 и регистра 4 и со входами блока центрального управления 2.

Входы блока преобразования кодов адресов 7 соединены с регистром входного адреса 16, с регистром машинного адреса 8 и с блоком памяти параметров модификации адресной системы 1 .

Регистр 16 является буферным регистром для кодов адресов, подлежащих обратному преобразованию. Выходы блока преобразования кодов адресов 7 соединены со входами блоков анализа 9 и ввода-вывода 10, с блоком памяти приоритетных адресов 3 и с блоКОЛ1 памяти параметров модификацип адресной системы 11.

Входы блока анализа 9 соединены с выходом регистра 16 - с выходом блока управлеНИН 2, а выход блока 9 соединен со входом блока ввода-вывода 10.

Однн выход блока ввода-вывода 10 является выходом устройства, второй соединен с регистром 16, третий - с блоком 11. Управляюший вход блока ввода-вывода 10 подключен к выходу блока 2. Вход блока 10 является входом устройства. Выходы коммутатора 13 подключены к объекту проверки 14, ко входу дискриминатора сопротивления связей 15.

Дискриминатор 15, предназначенный для регистрации наличия приводной пли резистивной связи, имеет два выхода, которые связаны со входами блока управления 2 и. со входами блока анализа 9- и блока ввода-вывода 10.

Программа работы устройства, заиисаттная в блоке памяти программы, обеспечивает поиск п обнаружение как проводных, так и резистивных связей. Таблица резистивных связей каждой цепи представляется на бланке после ее проводных связей в внде перечисления цепей, связанных с данной цепью через сопротивление, причем каждая такая цепь

представляется только одной - начальной точкой. Порядок следования этих точек такой же, как и проводных связей - монотонное возрастание адресов. В специальном разряде адресной строки указывается значение номинала сопротивления, зашифрованное десятичной цифрой. Этот номинал определяется с помощью дискриминатора сопротивления связей 15.

Предусмотренное в устройстве выделение

приоритетных цепей (например, цепей земли, питания и т. п.) путем занесепня их адресов в блок 3 обеспечивает их первоочередную проверку, безусловную идентификацию по записанному адресу п приоритет при выявлении

резистивных связей рядовых и старших приоритетных цепей. В таблице проводных связей приоритетной цепи первым всегда является выделенный адрес независимо от его старшинства. Запись остальных точек проводной свя.п. следующих после начальной, подчиняется установленному порядку монотонного возрастания адресов, очередность следования приоритетных цепей друг за другом в начале остального массива цепей также подчиняется

этому порядку.

Для рядовых цепей, имеющих резнстивную связь с приоритетной цепью, другие резистивные связи не указываются. То же относится к

приоритетным цепям, имеющим резистивную связь с младшей приоритетной цепью. Устройство может работать в 2-х режимах: режиме подготовки программы по эталонному изделию п режиме проверки изделия по эталонной

программе.

7

В режиме подготовки ирограммы устройство работает следующим образом.

После подачи питающих напряжений устройство аптоАгатичееки устапавливаетс5 в исходное состояние. В блок памяти приоритетных адресов 3 и блок памяти параметров моднфпкапии адресной системы счисления П заиосят коды адресов начальных точек приоритетных непей к точек, в которых происходит изменение адресной системы счисления и коды модулей пересчета.

Согласно заданной программе блок управления 2 передает командные имнульсы в блоки 1, 6, блок 3, регистр 4 и б.лок 5, по которым начггнается обследование цепей, адреса начальных точек которых записаны в блоке 3. Каждый адрес ноочередно, начиная с младшего, выбирается из блока 3 в регистр 4.

Блок 5 переключается на выдачу адреса из регистра 4, и начинается поиск связи точки с этим адресом.

Вначале находят все проводные связи с выводом на печать, потом - резистивные связи.

При поиске резистнвпых связей дискриминатор 15 регистрнрует нахождение только тех точек, связь которых с исходной точкой носит резнстивный характер, то есть сопротнвление связей которого больнге пороговой величины, определяюн ей границу проводной связи, но меньше порога, соответствующего нолной изоляггин.

Каждая, найденная таким образом точка, подвергается анализу на начальность нени, (то есть является ли она младнтей в своей ценн). Для этого ее адрес из блока грзтпового поиска 6 передается в регистр 4, и производится поиск первой проводной связн этой точки, а затем сравнение заданного и найденного адресов в блоке управления 2. Если точка окажется начальной (что бздет прн равенстве адресов в регистре 4 и в блоке 6), то ее адрес из блока груипового поиска б выводится через регистр 8, блок нреобразоват-гя кодов адресов 7 и блок ввода-вывода 10 на перфорацию или печать. Если же найденная резнстивная точка окажется не начальной, то ее адрес из регистра 4 передается обратно в блок группового поиска б - для продолження нонска. а в резнсторе 4 нАтем передачи из блока намя-пг нрноритетных адресов 3 восста1гавливается исходная точка и попек рсзистивпьтх связей продолжается.

Таким образоАт, на печать выводится только одня, начальная точка цепи, имеющая с проверяемой пенью резпстивную связь.

После проверки всех приоритетных нсней начг-нается проверка рядовых (непрноритетных) цепей. Для проверки каждой очередной точки в счетчик 12 тгз блока управления 2 прибавляется «1, а блок 5 нереключается на выдачу в коммутатор 13 кода из счетчнка 12. Далее нроизводится поиск нроводных связей проверяемой точки, причем, если эта точка оказывается не начальной, что устанавливается путем сравнения в блоке 2 адреса нервой найденной точки с адресом исходной точкг), то поиск связей прекращается и в счетчике 12 танавливается очередной адрес признака. Для начальной точки пронзводится проверка та связь ее с нриоритстпымп точками. Для этого адрес этой точки остается в блоке б, а в porncTD 4 поочередно вызываются адреса из блока 3. блок 5 нереключается на регистр 4 и пронзводится опрос дискриминатора 15 на налгнпте проводной связи. Если такая связь обнаруживается, то дальнейщий поиск связей этой точкп также прекращается (поскольку она уже вошла в нрноритетную цепь). Еслн же начальная точка не относптся к приоритетной

цени, то производится поиск и вывод в блок 10 для печати всех точек, нмеющих с ней проводную связь. После нахождения проводных связей нроизво.а.ится поиск резистивных связей даггной цепи, выполняемый так же, как и

для приоритетных цепей, е использованием регнстра 4 для анализа найденных точек на «начальность, с той лишь разницей, что код исходной точки тенерь сохраняется в счетчике 12. Найденные начальные точки цепей,

имеющих с опрашиваемой цепью резистивную связь, проверяются на принадлежность, к приоритетным пеням по методу, описанному выHie. Если оказывается, что опрашиваемая цець связана резистивно с нриоритетной цепью, то

только эта связь и фиксируется (другие резистивные связн этой цени не обследуются). Благодаря исключается многократное повторение проверки одних и тех же резистивных связей в случае, когда, например, множество цепей связаны через сопротивление с одной и той же цепью (например, с землей), которую в этом случае целесообразно выделить, как приоритетиую.

Вывод требуемых адресов на печать из регистра адреса нризнака 4 или блока груннового поиска б производится через блоки 8, 7, 10. При этом происходит обратное преобразование адреса из машинного в табличный (реальный). Это преобразование адреса нроисходит путем параллельного счета ИМПУЛЬСОВ в двух счетчиках, имеющихся в блоке 7, один тЗ которых считает по модулю, СтановленноMV для машинного адреса, а считает но ,тодулю, задаваемому из блока намяти нараметров модификации адресной cиcтc fы счпслення 11.

После каждого счетного имнульса в схеме срявнення, входящей в блок преобразования кодов адресов 7. происходит срявгггипе полученного таблнчного адреса с адресом очередггой точкп модификации адрссггой системы счисления, также выдаваемым из блока П.

При совпадении адресов, счета, выдаваемый из бдока намяти нараметров модифнкании адресной системы счнсления П. меняется на очередной: общий счет нмнульсог ппоисходит до совпадения кодов в счетчике ианигнного адреса блока нреобразования кодов адресов 7 и регистра мангннного адреса 8,

после чего в счетчике табличного адреса блока преобразования.кодов адресов 7 оказывается преобразованный адрес, который передается пз блока 7 в блок ввода-вывода 10 на печать или перфорацию.

Прямое преобразование адресов, которое требуется при вводе чисел в устройство или для контрольных операций, производится аналогичным образом с той лишь разницей, что счет ндет до совпадения кодов в счетчике табличного адреса блока преобразования кодов адресов 7 и регистра 16.

В режиме нроверки изделий по эталонной программе (режим контроля) устройство осуществляет поиск связей аналогично описанному выше поиску связей в режиме подготовки программы, по найденные адреса из блока 7 ие сразу выводятся в блок 10, а нередаются через блок анализа 9. В блоке 9 найденные адреса сравниваются с адресами, вводимыми с контрольной перфоленты через блок 10, 16 и на печать через блок 10 выводятся только те адреса, которые являются ошибочными - лишними, недостаюшими или отличающими но сопротивлению связей.

Преимуществами описанного устройства перед предшествующими аналогичными устройствами являются:

исключение необходимости выпаивания или закорачивания, имеющихся в монтаже проверяемого изделия резисторов, и возможность проверки требуемых резистивных связей между цепями, что существенно сокращает время и трудоемкость проверки таких изделий;

выдача данных в реальных адресах проверяемого объекта даже нри наличии в нем нескольких адресных систем, что исключает необходимость пользоваться в таких случаях переводными таблицами для расщифровки адресов;

возможность выделения приоритетных цепей, которые проверяются в нервую очередь, и резистивная связь с которыми других цепей исключает их взаимную проверку, благодаря чему упрощается и значительно сокращается запись таблицы монтажа и соответственно объем эталонной перфоленты;

запись данных на эталонной нерфоленте в реальных адресах проверяемого изделия, благодаря чему упрощается подготовка исходных перфолент с помощью ЭВМ, т. к. исключается необходимость перевода реальных адресов в условные, а также появляется возможность ручной корректировки и подготовки перфолент.

В результате этих преимуществ значительно повышается оперативность и общая производительность работ при проверке монтажа электронных вычислительных машин, узлов и блоков радиоэлектронной аппаратуры.

Формула изобретения

Устройство для автоматической проверки люнтажа, содержащее блок управлепия, блок группового поиска, коммутатор, блок преобразования кодов адресов, блок анализа, блок

ввода-вывода, блок памяти программы, блок памяти параметров модификации адресной системы счисления и счетчик адресов признака, причем выход и вход блока памяти программы соединены соответственно с первыми входом п выходом блока управления, вторые выход и вход которого соединены соответственно с первыми входом и выходом блока группового поиска, третий выход блока

управления соединен со входом счетчика адресов признака, четвертый, пятый, шестой и седьмой выходы блока управления соединены с управляющими входами блока преобразования кодов адресов, блока аналпза, блока ввода-вывода и блока памяти параметров модификации адресной системы счисления, второй выход блока группового поиска соединен с третьим входом блока управлення и с первым входом коммутатора, выход

которого является первым выходом устройства, первые выход и вход блока преобразования кодов адресов соединены соответственно со входом и выходом блока памяти параметров модификации адресной системы счисления, второй выход блока преобразования кодов адресов соединен с первыми входами блока анализа и блока ввода-вывода, выход блока анализа соединен со вторым входом блока ввода-вывода, первый выход которого

является вторым выходом устройства, а третий вход - входом устройства, отличающееся тем, что, с целью расщирения функциональных возможностей за счет организации контроля резистивных связей между проводными цепями, в устройство введены блок памяти приоритетных адресов, регистр адреса признака, блок выдачи адреса признака, дискриминатор сопротпвления связей, регистр

входного адреса и регистр мащинного адреса,

причем восьмой, девятый, десятый и одиннадцатый выходы блока управления соединены с управляющими входами блока памяти приоритетных адресов, регистра адреса признака, блока выдачи адреса признака и регистра машинного адреса, выход блока памяти соединен с первым входом регистра адреса признака, второй вход которого соединен с выходом блока группового поиска, а выход - с первыми входами блока выдачи адреса признака и регистра машннного адреса и со вторым входом блока группового поиска, выход счетчика адресов прпзнака соединен со вторым входом блока выдачи адреса признака, выход которого соединен со вторым входом коммутатора и

с четвертым входом блока управления, второй выход коммутатора соединен со входом дискриминатора сопротивлепия связей, первый выход которого соединен с пятым входом блока управления, а второй выход - со вторым

входом блока анализа и с четвертым входом б,-|ока ввода-вывода, выход блока группового поиска соединен со вторым входом peri гетра машинного адреса, выход которого соединен со вторым входом блока преобразования кодов адресов, третий выход блока преобразо11

вания кодов адресов соединен со входом блока памяти приоритетных адресов, второй выход блока ввода-вывода соединен со входом регистра входного адреса, выход которого соединен с третьими входами блока анализа и блока преобразования кодов адресов, третий ;ыход блока свода-выхода соединен со вторым входом блока памяти параметров модификации адресной системы счисления.

12

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №404056, кл. G 05В 23/02, 1970.

2.Авторское свидетельство СССР №342189, кл. G 06F 11/00, 1970.

3.Обмен опытом в радиопромышленпости. М., НИИЭИР, 1974, № 6, с. 54-56 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для контроля ферритовых сердечников запоминающих матриц | 1984 |

|

SU1280460A1 |

| Запоминающее устройство | 1976 |

|

SU613401A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для контроля электрических цепей | 1980 |

|

SU1018054A1 |

| Устройство для ввода информации | 1981 |

|

SU962892A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для проверки электрического монтажа | 1978 |

|

SU741277A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для задания тестов | 1981 |

|

SU1010632A1 |

Авторы

Даты

1978-02-28—Публикация

1975-05-19—Подача