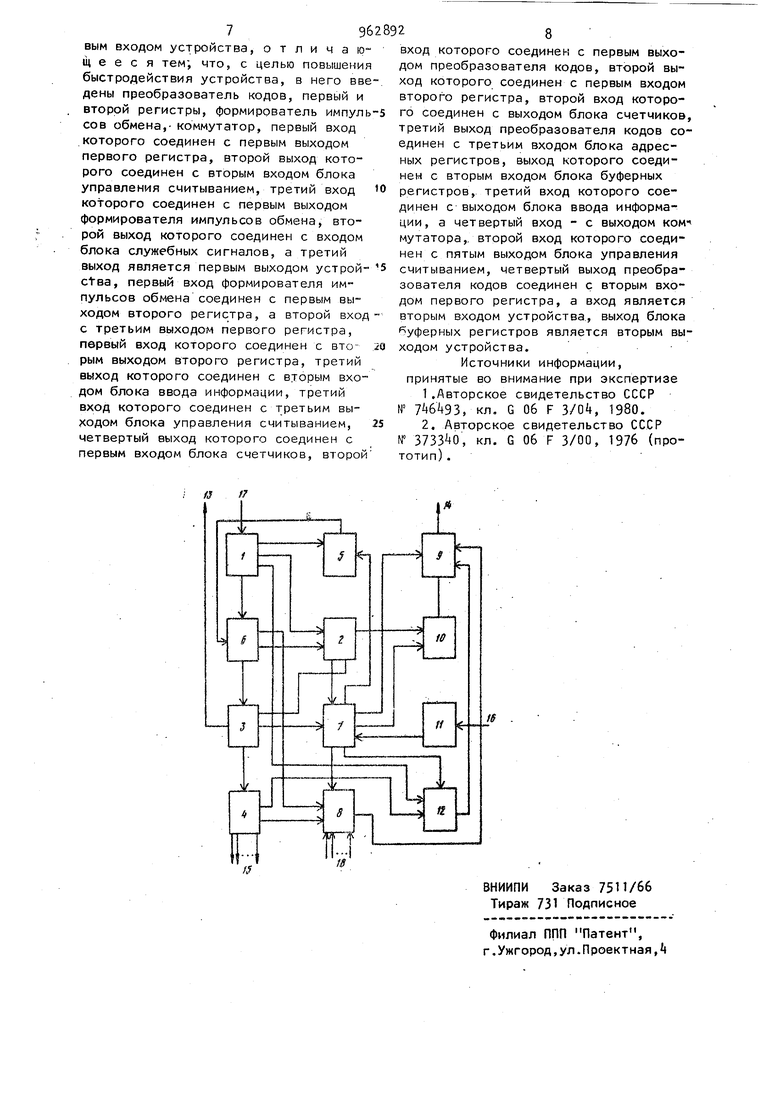

Устройство относится к вычислитель ной технике и может быть использовано при автоматическом вводе информации от множества датчиков. Известно устройство для ввода ийформации, содержащее последовательно соединенные блок коммутации, блок управления, подключенный к блоку выделения кода времени и блоку выбора каналов, преобразователь кодов, блок формирования машинных слов, блок сопг ряжения, блок формирования команд обмена, блок преобразования временного масштаба и осуществляющее периодический ввод массивов информации от датчи ков во внешнюю память ЭВМ в заданные интервалы времени 1. , . Однако в указанном устройстве не предусмотрен непосредственный ввод информации в оперативную память ЭВМ, а также одновременный прием информации в устройство ввода от множества датчиков, что вызывает дополнительные потери времени в процессоре на ввод информации в оперативную память. Наиболее близким к предлагаемому является устройство для ввода информации, содержащее регистр сдвига,, буферный регистр, счетчик, блок ввода, блок служебных сигналов, блок управ-i ления счетчиком, блок управления считыванием, блок формирования признаков зон и блок синхронизации 2. Достоинством известного устройства является формирование информации с признаком зоны памяти ОЗУ, позволяющее сократить время в процессоре на, формирование адреса для записи информации в память ОЗУ, увеличив быстродействие системы, однако в нем не предусмотрено задание режима обмена с определением необходимой длины массива от каждого датчика информации и, кроме того, совмещение во времени одновременного приема информации от датчиков в устройство ввода с выдачей ид устройства ввода в процессор в режиму непосредственного доступа к ОЗУ процессора, что уменьшает быстродействие и гибкость при работе процессора с множеством датчиков информации. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для ввода информации содержащее блок счетчиков, блок формирования служебных сигналов, первый выход которого соединен с первым- входом блока адресных регистров, а второй выход соединен с первым входом блока ввода информации, входы группы входов которого являются входами rpyn пы устройства, выходы группы блока служебных сигналов являются входами группы устройства, второй вход блока адресных регистров соединен с первым выходом блока управления считыванием, второй ВЫХОД которого соединен с nepвым входом блока буферных регистров, первый вход блока управления считыванием соединен с выходом блока синхро.низации, вход которого является первым входом устройства, введены преобразователь кодов, первый и второй регистры, формирователь импульсов обмена, коммутатор, первый вход которого . соединен с первым выходом первого регистра, второй выход которого соединен с вторым входом блока управления считыванием, третий вход которого соединен с первым выходом формирователя импульсов обмена, второй выход которого соединен с входом блока служебных сигналов, а третий выход является первым выходом устройства, первый вход формирователя импульсов обмена соединен с первым выходом второго регистра, а второй вход - с третьим вы ходом первого регистра, первый вход которого соединен с вторым выходом второго регистра, третий выход которого соединен с вторым входом блока ввода информации, третий вход которого соединен с третьим выходом блока управления считыванием, четвертый выход которого соединен с первым входом блока счетчиков, второй вход которого соединен с первым выходом преобразова теля кодов, второй вход которого со.единен с первым входом второго регист ра, второй вход которого соединен с выходом блока счетчиков, третий выход преобразователя кодов соединен с третьи, им входом блока адресных регистров, выход которого соединен с вторым входом блока буферных регистров, третий 962 вход которого соединен с выходом блока ввода информации, а четвертый входс выходом коммутатора, второй вход которого соединен с пятым выходом блока управления считыван11ем, четвертый выход преобразователя кодов соединен с вторым входом первого регистра, а вход является вторым входом устройства, выход блока буферных регистров является вторым выходом устройства. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит преобразователь 1 кодов, первый регистр 2, формирователь 3 импульсов обмена, блок служебных сигналов, блок 5 счетчиков, второй регистр 6, блок 7 управления считыванием, блок 8 ввода информации , блок 9 буферных регистров, коммутатор 10, блок 11 синхронизации, блок 12 адресных регистров, первый выход 13, второй выход Н, группу 15 выходов, первый вход 16, второй вход 17, группу 18 входов. Преобразователь 1 кодов имеет дешифраторы кодов операции, адресов датчиков информации, поступающих от процессора. Регистр 6 связи с датчиками информации имеет число разрядов, равное числу подключаемых датчиков информации. В единичное состояние каждый разряд регистра 6 устанавливается с помощью преобразователя 1.кодов одновременно с выдачей информации из процессора о длине массива, который необходимо снять с соответствующего датчика. В нулевое состояние каждый разряд регистра 6 устанавливается при считывании всей длины массива данного датчика, определяемое с помощью.соответствующего счетчика 5. Регистр 2 предназначен для организации цикла связи с процессором. Число разрядов этого регистра также равно числу датчиков информации, каждый разряд регистра 2 устанавливается в единичное состояние во время приема с процессора информации о начальном адресе ячейки ОЗУ процессора для массива информации соответствующего датчика информации. Информация на регистре обновляется после выдачи i-ro слова со всех датчиков путем переписи с регистра 6. Установка в нулевое состояние каждого разряда регистра 2 происходит после окончания цикла выдачи в процессор 1-го слова массива соответствующего датчика. Формирователь 3 импульсов обмена . имеет схемы сравнения регистров 2 и 6 Совпадение кодов регистров инициирует формирование команды начала группово го обмена с абонентами,, а совпадение; кодов этих регистров после выдачи мас сивов информации от всех датчиков вызывает формирование команды окончания группового оимена. Блок k служебных сигналов формирует синхроимпульсы для обмена информации последовательным кодом одновременно с тех датчиков информации, которым соответствует единичное состояние регистра 6 Кроме то го, блок t вырабатывает сигналы, управляющие преобразованием последовательного кода в параллельный в блоке 8 ввода информации от датчиков и пере дачей кода адреса из блока 12 адресных регистров и кода информации из блока 8 ввода в блок 9 буферных регистров. Блок 7 управления считыванием содержит управляющие триггеры, другие логические элементы, осуществляющие согласование скорости приема информации от датчиков и выдачи ее в процес-. сор. Коммутатор 10 связи с процессором представляет собой регистр, в котором В единичное состояние поочередно уста навливается один из разрядов на время передачи очередного слова из устройст ва для ввода информации в процессор. При этом коммутатор не подключает те датчики, с которыми обмен не был инициирован или же у которых массив информации уже закончился. Блок 11 синхронизац 1и осуществляет привязку тактовой сетки устройства для ввода к тактовой сетке процессора Устройство работает следующим образом. Преобразователь 1 кодов осуществляет дешифрацию кодов входной информации от процессора, записывая в начале в соответствующие счетчики блока 12 коды начальных адресов для соответствую1чих датчиков информации и формируя при этом код регистра 2, а затем коды количества слов в массиве каждого датчика, формируя код регистра 6 в связи с датчиками информации. При совпадении кодов регистров 2 и 6 формируется импульс начала группового обмена с помощью блока 3, кото рый в свою очередь запускает блоки k и 7. С помощью команд блоков k и 7 на чинается прием информации одновременно с тех датчиков информации, которым соответствуют единичные состояния соответствующих разрядов регистра 6. Пбсле приема первого слова массива ин.формации одновременно со всех запра-; шиваемых датчиков на регистры блока 8 ввода информации с помощью команд блока 7 управления считыванием переписывается информация с блока 8 ввода в : блок 9 буферных регистров параллельным кодом и запускается временная диг аграмма считывания информации в про-, цессор в.режиме непосредственного доступа в память ОЗУ. При этом одновременно с выдачей информации и сформированных адресов ячеек ОЗУ в процессор параллельным кодом наФ1нается прием следующего слова массивов информации от датчиков.. Таким образом, в.устройстве осуществляется непрерывный прием информации одновременно со всех датчиков с выдачей в процессор в режиме непосредственного доступа в ОЗУ. При этом происходит значительная экономия времени процессора, что очень важно при решении оперативных задач управления. Кроме этого, устройство для ввода формирует команды начала и окончания группового обмена, тем самым освобЬждая процессор от формирования этих операций в своей операционной системе. Непосредственная запись массивов информации в оперативную память сокращает общее время на решение задач в процессоре, так как не требуется o ipaщение во внешнюю память. Формула изобретения Устройство для.ввода информации, содержащее блок счетчиков, блок формирования служебных сигналов, первый выход которого соединен с первым входом блока адресных регистров, а второй выход соединен с первым входом блока ввода информации, входы группы входов которого являются входами группы устройства, выходы группы блока служебных сигналов являются выходами группы устройства, второй вход блока адресных регистров соединен с первым выходом блока управления считыванием, второй выход которого соединен с первым входом блока буферных регистров, первый вход блока управления считыванием соединен с выходом блока синхронизации вход которого является перв

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации в память микроЭВМ с общей шиной | 1982 |

|

SU1290336A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

Авторы

Даты

1982-09-30—Публикация

1981-01-04—Подача