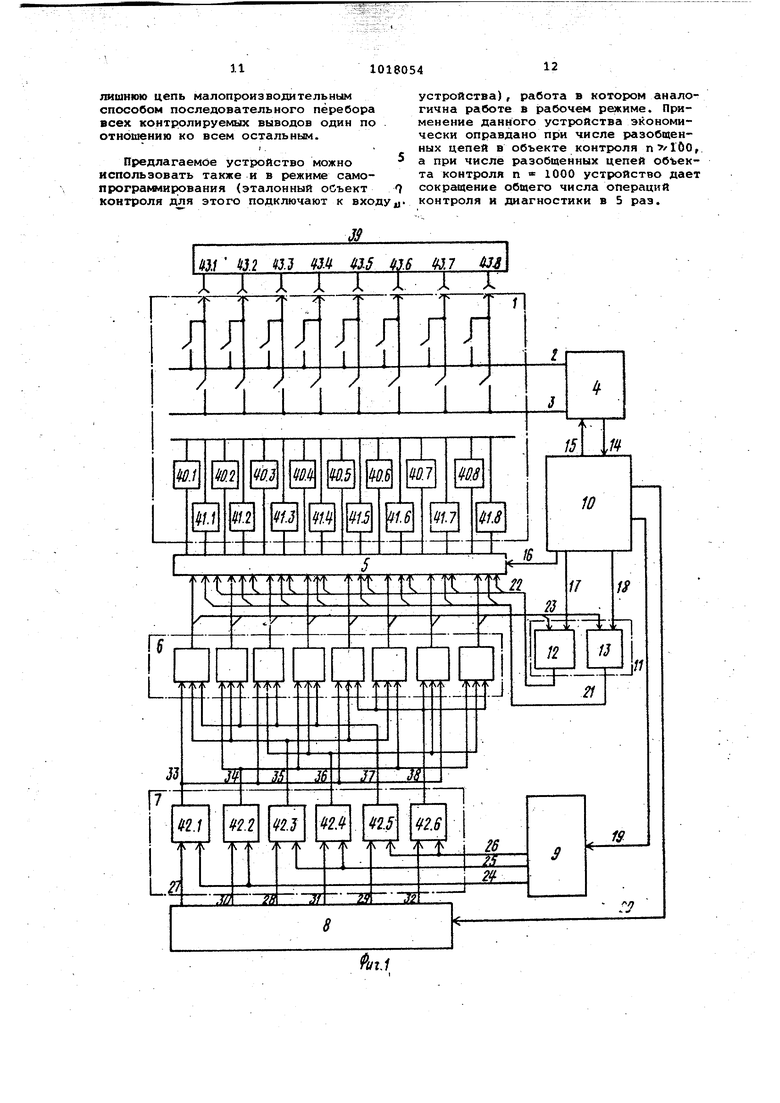

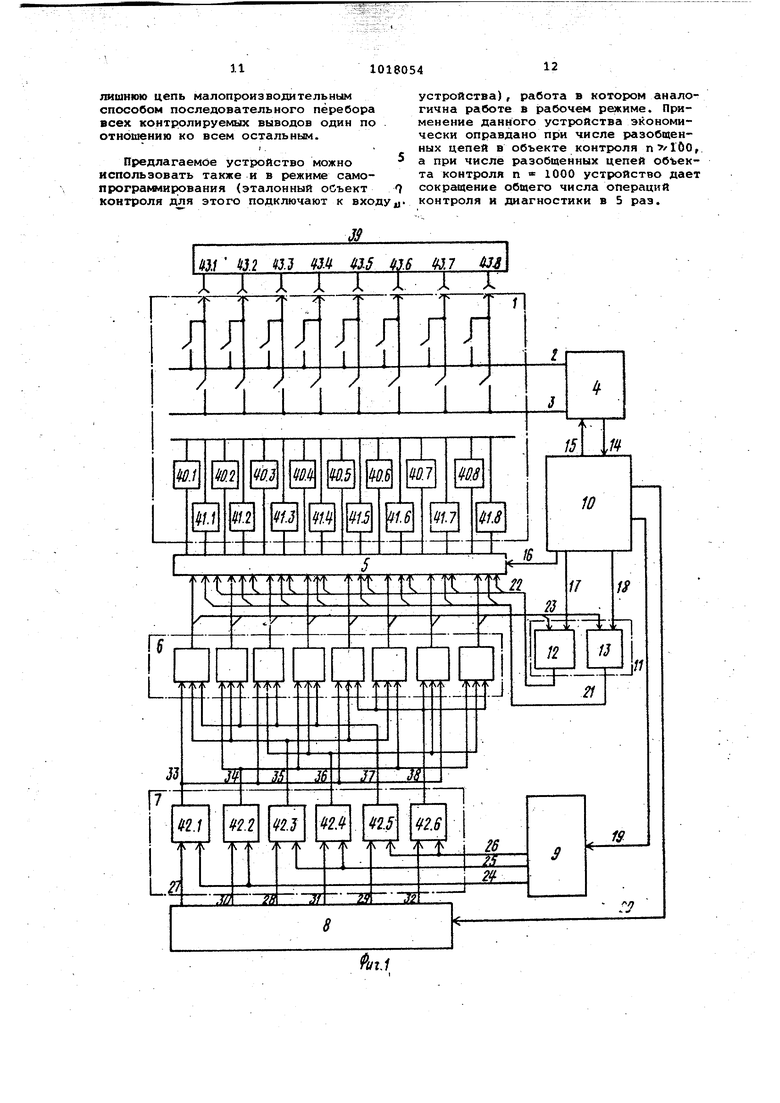

Изобретение относится к иэмери-тельной технике и может быть испол зовано для контроля сопротивления испытания электрической прочности изоляции электрических цепей, а та же для поиска лишних связей между разобщенными цепями кабельных изде лий, печатных плат и т.п. Известно устройство, содержащее коммутатор, блок управления, блок памяти, регистр адресов и блок измерения 1 . Недостатком этого устройства яв ляется необходимость в большом объ ме блока памяти для реализации диа ностики, а также низкое быстродейс вне при диагностике, обусловленное последовательным перебором всего массива адресов при выборе подмножества адресов выводов, которые необходимо в процессе диагностики подключить к измерительным шинам. Наиболее близким по технической сущности к предлагаемому является устройство для контроля электрических цепей, содержащее коммутатор, блок переключений, запоминающий бло распределитель (дешифратор) , венти ли, регистр адреса, блок ввода и управления, элементы запрета, комби натор и генератор, контакты коммута тора соединены с его входами и двум выходными шинами, соединенными с блоком измерения, выход которого соединен блоком анализа и управления, первый выход которого соединен с входом регистра адреса, а второй выход блока анализа и управления соединен с управлякхдим входом блока управления коммутатором, выходы кот рого соединены с обмотками реле ком мутатора, а остальные входы блока управления коммутатором соединены с выходами дешифратора и блока памя .ти, входы которого соединены с выходами дешифратора L2, Недостаток известного устройства также заключается в низком быстродействии при локализации цепей с по ниженныгл сопротивлением изоляции. Цель изобретения - повышение быстродействия при локализации цепей с пониженным сопротивлением изЬляции. Эта цель достигается тем, что в устройство для контроля электрических цепей, содержащее коммутатор, контакты которого соединены с его входами и двумя выходными шинами, соединенными с блоком измерения, выход которого соединен с блоком анализа и управления, первый выход которого соединен с входом регистра адреса, а второй выход блока анализа и управления соединен с управляю щим входом блока управления коммутатором, выходы которого соединены с обмотками реле коммутатора, а остальные входы блока управления коммутатором соединены с выходами дешифратора и блока памяти, входы которого соединены с выходами дешифратора, введены блок логического суммирования, регистр группового выбора адТреса, а блок памяти выполнен из двух узлов - узла адресного сброса и узла адресного отключения, при этом третий выход блока анализа и управления соединен с входом регистра группового выбора адреса, выходы разрядов которого соединены с соответствующими входами блока логического суммирования, другие входы которого соединены с выходами регистра адреса, а выходы блока логического суммирования соединены с соответстВующими входами дешифратора, выхо- ды которого соединены с входами узлов адресного сброса и адресного отключения блока памяти, подключенных к соответствующим выходам блока анализа и управления, причем блок логического суммирования выполнен на элементах ИЛИ, число которых равно числу прямых и инверсных выходов регистра адреса, при этом первые входы элементов ИЛИ соединены с инверсными и йрямыми выходами регистра адреса,-а вторые входы элементов ИЛИ попарно и поразрядно соединены с соответствующими выхода1«ш регистра группового выбора гшреса, а четвертый выход блока анализа и управления соединен с блоком измерения. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема .алгоритма работы устройства; на фиг. 3 - пример выполнения цепей объекта контроля с линиями связи. Устройство (фиг. 1) содержит коммутатор 1 с выходными шинами 2 и 3, блок 4 измерения, блок 5 управления коммутатором, дешифратор б, блок 7 логического Суммирования, регистр 8 адреса, регистр 9 группового выбора адреса, блок 10 анализа и управления, блок 11 памяти, состоящий из узла 12 адресного сброса и узла 13 адресного отключения, а также соединительных шин 14 и 15, соединяющих блок 10 анализа и управления с блоком 4 измерения, 16 - с блоком 5 управления коммутатором,. 17 - с уз-, лом 12 адресного сброса, 18.- с уз-, лом 13 адресного отключения блока 11 памяти, 19 - с регистром 9 группового выбора и 20 - с регистром 8 выбора адреса, шин 21-23,соединяющих соответственно узлы 13 адресного отключения и 12 адресного сброса блока памяти с соответствующими входами блока 5 управления коммутатором и с дешифратором 6, шин 24-26, соединяющих выходы разрядов, начина с младшего регистра 9 группового вы бора адреса с входами сортветствующих разрядов блока 7 логического суммирования, шии 27-29, соединяющих инверсные выходы и шин 30-32, соединяюашх прямые выходы разрядов регистра 9 выбора адреса с соответствующими входами блока 7 логического суммирования, разрядные выходы которого через шины 33-38 соединены с соответствующими входами дешифратора, и объект 39 контроля, цепи которого обозначены в двоичном коде от 000 до 111. Коммутатор 1 содержит по два реле 40.1-40.8 и 41.141.8 для каждой из цепей объекта контроля, которые через контакты Каждого реле соединены соответствен но с выходными шинами 2 и 3. В блок 5управления коммутатором каждый канал управления выполнен в виде элемента памяти и усилителя, соединенного с обмоткой соответствующего реле коммутатора 1. Дешифратор 6 выполнен на элементах И. Блок 7 .лог ческого суммирования содержит по дв элемента 42.1-42.6 ИЛИ для выходов каждого разряда регистра 8 адреса. Узлы 12 и 13 адресного сброса и адресного отключения состоят из эле ментов памяти по числу входов устройства. Блок 10 анализа и управления может быть выполнен в виде специального логического устройства или .ЭВМ. Устройст1ао работает в двух режимах: режиме индивидуального выбора сщресов и режиме группового выбора адресов и подключения выводов 43.143.8 (000...111) объекта контроля 39 к шине 2 и 3 блока 4 измерения. I-... При контроле соединенных между собой выводов используется режим ин дивидуального выбора адресов. Для . этого по команде блока 10 анализа и управления после включения устрсЗй ства по шинам 15-20 блоки 4,5,8,9, 11,12 и 13 приводятся в начальное состояние. Затем по шине 20 из блока 10 в регистр 8 адреса заносится адрес начальной точки, например 010 проверяемой цепи объекта контроля 39, регистр 9 остается обнуленным, и на его выходах (шины 24-26) во всех разрядах остаются логические О. Из регистра 8 адреса через элементы 42.1-42,6 ИЛИ блока 7 логи ческого суммирования и дешифратор 6указанный адрес поступает в блок 5 управления коммутатором в тот эле мент его, памяти, который соответствует адресу 010. Одновременно из блока 10 по шине 16 подается команда Подключение к шине 2Vi Включается соответствующее реле 40.3 ко мутатора 1 и своим контактом подклю ает выход объекта 39 контрол с адесом 010 к шине 2, реле 4143 при этом остается выключенным. Затем . - ргистр 8 обнуляется и в него заносится адрес второй точки проверяемой цепи, например 101, а по шине 16 в блок 5 управления коммутатором подается команда Подключение к цшне 3, включается реле 41.6 и подключает указанную точку в шине 3. Далее по команде из блока 10 блок 4 измеряет сопротивление цепи между выводами 43.3 (010) и 43.6 (101), а результат по имне 14 поступает в блок 10, где запоминается и анализируется. После этого по команде из блока 10 регистр 8 снова обнуляется, а вывод 43.3 (010) остается подключенным. В следующем такте вызывается адрес очередной точки,электрически соединенной с выводом 43.3 (010) и подключается к шине 3, вновь измеряется сопротивл:ение, результат запоминается. Процесс продолжается до тех пор, пока не будут проверены все выводы цепи, nocjge чего реле 40.3.также отключается; выбирается и подключается к тине 2 начальная точка следующей цепи и т.д. до тех пор, пока не будут проверены все соединенные цепи. После проверки электрических соединений переходят к режиму проверки электрически разобщённых цепей. Для этого отключают с помощью узла 13 адресного отключения те выводы объекта контроля 39, которые/не являются начальными для цепей. Для этого в регистр 8 последовательно записывают адреса отключаемых выводов, которые затем по шине 23 поступают в узел 13, по шине 18 с блока 10 поступает команда Отключение, в узле 13 по выбранному каналу срабатывает элемент памяти и по шине 21 выдается сигнал, исключающий подключение реле по этим адресам. В результате этой подготовки все выводы электрических цепей, кроме начальных, не будут подключаться к шинам 2 и 3 и участвовать в последукмдих проверках. При описании алгоритма работы устройства М режиме контроля разобщенных цепей и поиска адресов выводов, образующих лишние связи, на 2 -обозначено: -номер цикла контроля; -количество циклов контроля (количество двоичных разрядов . адресов точек); -номер текущего разряда иско-мого адреса; -Номер Лишней цепи; -номер вывода лишней цепи; адрес k-ro вывода т-й лишней цепи) .,)- i-й разряд регистра 8 (9) ; ( массив разрядов регист 8(9) за исключением разрядаQV( i массив разрядов регист , ра 8(9); lVoi- 4ej : массив разрядов регист ра 9 с разряда а по раз ряд € включительно,,. - массив разрядов адреса |%cij{Am,K)- запись 1 в J-й разря текущего гщреса „ - сопротивление между контролируемыми вывода ми; R - минимсшьио допускаемое значение сопротивления между выводами) С, - команда Сброс шины 2 t1 - команда Подключение к шине П, - команда Подключение к шине Ар - команда Адресный сбро по шине Ло - команда Адресное отключение ;/А HBV вывод массива адре сов выводов лишних цепей (если они обнаружены) на внешнее устройство, В первом цикле контроля к шине 2 подключаются выводы, номера которых в двоичном обозначении имеют i первом (младшем) разряде, а к шине 3 - номера с О в первом разряде во втором цикле к шине 2 подключают ся выводы с , а к шине 3 с О во втором разряде и т.д. При этом для подключения на выбранную шину выводов, адреса которых имеют 1 (0) в -м разряде, необходимо по шиНе 16 подать команду Подключение к выбранной шине , в регистр 9 занес ти код, который имеет О в -м разряде и в остальных, а в ре гистр 8 ванести код, котррый имеет 1 (С) вj-м разряде, О в осталь ных. Таким образом, число циклов конт роля равно числу двоичных разрядов в обозначении количества выводов объекта контроля. Если имеем п выводов, то число циклов определяется N lCog- hl, где itoff h / наименьшее целое число не менее Вод иЕсли в объекте контроля имеются избыточные связи между номинально разойденными цепями, то по групповому логарифмическому методу производится поиск адресов этих связей с помощью предлагаемого устройства, в промежуток времени между циклами кон троля. Работа предлагаемого устройства (Фиг 1) и алгоритмы контроля и диагностики неисправностей рассмат:риваются (фиг. 2) на примере объекта контроля, схема которого приведена на фиг. 3. Все выводы объекта контт рОля с 43.1 (000) по 43.3 (111) являются номинально разобщенными, при этом имеют место неисправности (лишг ние цепи) между выводами 43.2 (001), 43.3 (010), 43.4 (011), а также 43.6 (101) и 43.7 (110). Процесс контроля разобщенных цепей начинается с того, что в ЭВМ (блок 10) в счетЧик циклов контроля заносится 1 (i: 1), номеру цепи присваивается значение 1 (га 1) - оператор 0 на фиг. 2, из ЭВМ по пине 16 в блок 5 управления коммутатором подается команда С - коммутатор 1 устанавливается при .этом в исходное состоя-, ние, когда все реле включены. Затем - оператор 0 - из ЭВМ в i-й (вначале ) разряд регистра 9 группового выбора заносится О, в i-й разряд а в остальные регистра 8 адреса заносится Ч , а в остальные разряды этого регистпо шине 16 выдается команда П2. При этом в первом цикле контроля (1 1) на выходе элементов 42.1-42.6 ИЛИ появляются сигна1, R 1, R| I, лы R « j - 1, в результате возбужR- - 1, R даются второй, четвертый, шестой, восьмой элементы И дешифратора 6, сигналы с которых поступают в блок 5 управления коммутатором, срабатывают реле 40.2, 40.4, 40.6, 40.8 и. подключают выводы 43.2, 43.4, 43.6, 43.3 к шине 2 блока 4. Так как управляняцие реле обладают памятью, то эти выводы остаются подключенными к шине 2 до поступления команды С2 по шине 16. Далее содержимое регистра 9 не изменяется, а в регистр 8 во все разряды заносятся 0 - оператор Оз, по шине 13 выдается команда ПЗ. В результате возбуждаются первый, третий, пятый, седьмой элекйнты И дешифратора 6. Выводы 43.1, 43.3, 43.5, 43.7 подключаются к шине 3. Проверяется с помощью блока 4 измерения ycлoвия R Rg - оператор Оф. Если условие соблюдается, в ЭВМ анализируется еще одно условие: i N . Если i N, что означает, что последний цикл контроля закончен, контроль заканчивается. Результаты контроля из памяти ЭВМ выдаются на внешнее устройство оператор О . Ecjra i « N, в счетчик циклов в ЭВМ добавляется i оператор О-, - и происходит возврат к оператору О. Если при исполнении Од получен результат Нет, что означает, что имеется, по KpaRtieft мере, одна лишняя цепь, происходит переход к ветви поиска адреса перво го (начального) вывода лишнея цепи к оператору Oj. При этом в ЭВМ счетчик циклов диагностики обнуляется (j 0), искомой цепи присваивается порядковый номер,начиная с ,выводу т-ой цепи (вначале ) также рприсваивается номер,начиная с (k 1, а в i-й разряд адреса первого вывода т-й цепи заносится О. Далее в счетчик j блока 10 добавля« ется - оператор 0, и проверя ется условие j i - оператор б переход к оператору O(j, если Нет - переход к операто ру О . При этом .J -му разряду адреса А дается пробное значение О, в регистр 8 из блока 10 зано сится значение уже найденных разрядо J3 первого по ( j - 1)-й адреса А,я,- И пробное значение j-го разряда ot (А,, ) 0. В остальные разряды . регистра 8 заносится О, также заносидся О в разряды с первого по j-й регистра 9, в остальные регистра 9 заносится . Из блока 10 в блок 5 по шине 16 посылается команда ПЗ. К шине 3 при этом подключаются выводы, адреса которых имеют в разрядах с первого по ( J- 1)-е значения, соответствую щие найденным значениям разрядов искомого вывода, в у-ом разряде значение О, значение остальных разрядов безразлично. По команде из блока 10 блок 4 проверяет условие R у. Rg - оператор О ..Если условие соблюдается, в i-ый разряд адреса (, ) заносится i - опе ратор О , и переходят к оператору О, , если Нет - для j -го разряда (А уп,4 ) сохраняется значение О и переходят к оператору 0 Оператор : проверка условия j N т.е. определен уже старший разряд адреса или нет. Если Нет - пере ход к оператору.О9. Процесс продолж ется до тех пор, пока не будут найдены все разряды адреса (А ). После этого переходят к поиску адре сов. всех выводов т-ой цепи, кроме первого. Для этого - оператор О . к номеру искомого вывода добавляется 1 (k k + 1), в счетчике ци лов остается число J N, а по шине 16 в блок 5 из блока 10 проходит ко манда С2. Коммутатор 1 приходит в исходное состояние, когда всё реле выключены. Далее - оператор О, на нается поиск адреса очередного k-ro (k J 1) вывода m-ой цепи, для которОй адрес первого вывода найден. Дл этого в J-й разряд искомого адреса заносится . В регистр 8 адреса в разряды с Q,j по QU заносятся значения адресов, записанные в регнстр адреса в ЭВМ с -j -го по п-й разряды соответственно, а в разряды Q . .. регистра 8 заносится О . В регистр 9 группового выбора в разряды q, ...Qjj заносится , а в разряды q ... - 1. По шине 16 в блок 5 выдается команда 112. При этом к ишне 2 подключаются выводы, адреса которых имеют в старших разрядах уже найденные значения, в -м ра.зряде ..меют , а значения остальных разрядов не анализируются. Затем в регистр 8 ь разряды с первого по N-й заносится адрес первого вывода анализируемой цепио..., (A.l а в регистр 9 - О оператор 0, , а на шине 23 образуется сигнал, соответствующий отключаемому гщресу, по шине 17 проходит команда автоматический сброс (АС), а затем по шине 16 ПЗ. При этом в результате воздействия по шине 22 сигнала с выхода узла 12 на вход блока 5 от шины 2 отключается вывод с адресом А щ , если он попал туда в операторе О , и в любом случае подключается к шине 3. Проверяется с помощью блока 4 условие RX RO оператор . Если , в ЭВМ в j-и разряд гщреса . заносится О оператор , блок 10 переходит к оператору Dgo , проверя.ется при этом условие j 1 . Если Да это означает, что закончено формирование последнего (младшего) разряда искомого адреса А т,к . Затем блок 10 переходит к оператору О. При этом в разряды с первого по N-й регистра 8 из блока 10 заносится код адреса А„,, во все разряды регистра 9 заносится О. На шине 23 образуется сигнал, соответствукидий ещресу отключаемого вывода, по имне 18 в узел 13 из блока Ю подается команда АО, сигналом по шине 21. в блок 5 - адрес А , при этом указанный вывод от шины отключается и из дальнейших проверок исключается. Далее блок 10 переходит к оператору О г проверяется условие ..N А„,к ) О .... О , т.е. содержит ли найденный адрес во всех разрядах 0. Если Да - то найденный вывод с адресом . является последним в га-й цепи. После этого переходят . к оператору s в счетчик номеров цепей добавляется и продолжается (Oj.) операция контроля с 1-го цикла, прерванного по оператору 0+. Если в операторе 0,2.1 получен результат Нет , то в т-й цепи вывод с ,л-1 апресом не является последним, и блок 10 возвращается к выполнению оператора Ojc в счетчик номера вывода добавляется , в счетчик j заносится N и начинается поиск следующего (k + 1)-го вывода т-й цепи. Если в операторе получен результат Нет, блок 10 переходит к оператору проверяется услови j 1, если Да - переход к опе-« paTQpy О и далее, как описано выш Если в операторе О/2д получен реблок 10 переходит зультат к выполнению оператора О, : в разряды с У-го по N-й регистра 8 зано сятся найденные значения .,,N (AM,к в остальные разряды регистра 8 заносится . Из счетчика вычита ется , в разряды с j -го по N-й регистра 9 заносится О, в остальные i по шине 17 в узел 1 из блока 10 подается команда Авто матический сброс (АС), а по шине 23 Образуются сигналы, соответствую щие адресам отключаемых в данном цикле При этом в результате воздействия на входы блока 5 сигналов по шине 22 от шины 2 отключается примерно половина выводов, причем та, адреса которых имеют О в следующем младшем (идущем за найденным) разря де. В найденный же разряд адреса за писывается - оператор Oz6 блок 10 возвращается к оператору О Если в операторе 02-0 получен резуль тат Нет, ЭВМ переходит к исполнению оператора счетчика j вычитается г по шине 16 из бло ка 10 в блок 5 проходит команда С2, а блок 10 переходит к оператору О и далее, как описано выше. Для объекта контроля, показанног на фиг. 3, процесс контроля разобщенных цепей с помощью предлагаемого устройства осуществляется следующим образом. О : i 1, m 1,, сброс шины 2 (С I 03,,,,,q,,,.Q, ,Qv подключение выводов 43.2, 43.4, 43, 43.3 к шине 2; Ь i О - Q , Q., 9 подключе ниё к шине 3 (ПЗ) и выводов 43.1, 43.3, 43.5, 43.7; нет .. R э О, k 1, . . (А + 1 i - П Э возврат к ,j - 1 да , . , j .1 2 .0 М i, JHeT ; 0,/.(a(A,,Jio(,,i(A,,.Oay $q,, q, j 14 в ; u - Чг . -: q подключение к шине 3 (ПЗ) выводов 43.1, 43.3 (на шине 2 выводы, подключенные в Оо); - R 7х Rg Oi5 : (А 1,1 ) Oi4 : з N Нет,возврат к О 0л : :) j + 1 3 : 3 i нет 0,,(A,,,),c(.4,,(A,,)}Oi,Oa,Q,L 0 q j , подключение вывода 43.3 к шине 3; : Ry 7/ R 3 . : j N Да , А 010 0,g : k k +1 2; j N 3 сбрюс шины 2; (,,4)-Оз o.-5o,Qaro -Q6; -J«V., подключение выводов 43.5,43.6, 43.7, 43.3 к шине 2; , Or,...г.) --ОъУ, o-Hi-.i сброс вывода А, с шины 2 и подключение его к шине 3; : R X / R-a переход. к ; .,, : (А .,,2 ) .0, Oio : j 1 Нет ; О, : J -j- 1 2 сброс шины 2 выводов, подключенных к О. и переход к ; О, о(а(А,,а),г ()- 02лЬ - ч О- jq. 5, 1 - 41 подключение к шипе 2 выводов 43.3, 43.4 , О,. :,... (А,,,. iO,,.,,3 О - 5 З,... } адресный сброс вывода 43.3 с шины 2 и подключение его к шине 3; RIL Кэ Нет ; Ог.4 : j 1 Нет ; , Оа С(.2,Ъ (А ) -, JQ,j , J ; О UQ, J j- 1 .1. О -в q J сброс с шины 2 вывоia с адресом 010 Оав: .(Ai.,y;A.j 011 возврат к Qfg : Ry 7/ R э Нет (A,2).-.bb0 5V....i, адресное отключение вывода А. 2 проверяется условие во всех ли разрядах адреса нули, Нет снова переход к оператору О. ,.. Как и в предыдущем цикле находится адрес А . После этого в О 2 получают для адреса А 000, что означает адрес А,, был последним в первой цепи, происходит переход к Oj,,. :т т+1 2и далее к О . Так же как и для второй цепи находятся адреса А, 110, К А 101, полученнре затем значение 000 означает, что адрес А, был последним во второй цепи, при этом в операторе по результату Да происходит переход к 0, далее к 0..., Og-, 0, снова O,...,Of с переходом по результату --Да в Or к Of,. На этом контроль разобщенных цепей заканчивается. В результате обнаруживаются адреса лишних связей по цепям: цепь 1 - А 010, 001, А,, 011; цепь 2 101. 110, А Известное устройство производит поиск адресов выводов, образующих

лишнюю цепь малопроизводительным способом последовательного перебора всех контролируемых выводов один по . отношению ко всем остальным.

} .,

Предлагаемое устройство можно

использовать также и в режиме самопрограммирования (эталонный оСъект 9 контроля этого подключают к входу .

устройства), работа в котором аналогична работе в рабочем режиме. Применение данного устройства экономически оправдано при числе разобщенных цепей в объекте контроля , а при числе разобщенных цепей объекта контроля п « 1000 устройство дает сокращение общего числа операций контроля и диагностики в 5 раз.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство группового программного управления технологическими процессами | 1989 |

|

SU1663603A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для сопряжения процессора с устройствами вывода | 1984 |

|

SU1206788A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКИХ -ЦЕПЕЙ, содержащее коммутатор, контакты которого соединены с его входами и двумя выходными шинами, соединенными с блоком измерения, выход которого соединён с блоком анализа и управления, первый выход которого соединен с входом регистра адреса, а второй выход блока анализа и управления соединен с управляющим входом блока управления коммутатором, выходы которого соединены с обмотками реле коммутатора, а остальные входы блока управления коммутатором соединены с выходами дешифратора и блока памяти, входы которого соединены с выходами дешифратора, о т л и ч а -ю щ е е с я тем, что, с целью повышениябыстродействия при локализации цепей с пониженным сопротивлением изоляции. в него введены блок логического суммирования, регистр группового выбора адреса, а блок памяти выполнен в виде двух узлов - узла адресного сброса и узла адресного отключения, при этом третий выход блока анализа и управления соединен с входом регистра группового выбора адреса, выходы разрядов которого соединены с соответствующими входами блока логического суммирования, другие входы которого соединены с выходами регистра адреса, а выходы блока логического суммирования соединены с соответствующими входами дешифратора, выходы которого соединены с входами узлов адресного сброса и адресного от- i ключения блока, памяти, подключенных (Я к соответствующим выходам блока анализа и управления, причем блок логис ческого суммирования выполнен на элементах ИЛИ, число которых равно числу прямых и инверсных выходов регистра адреса, при этом первые еходы элементов ИЛИ соединены с инверсными и прямыми выходами регистра адреса, а вторые входы элементов ИЛИ попарно и поразрядно соединены с соответствующими выходами регистра 00 О СП группового выбора адреса, а четвертый выход блока анализа и управления соединен с блоком измерения. 4;

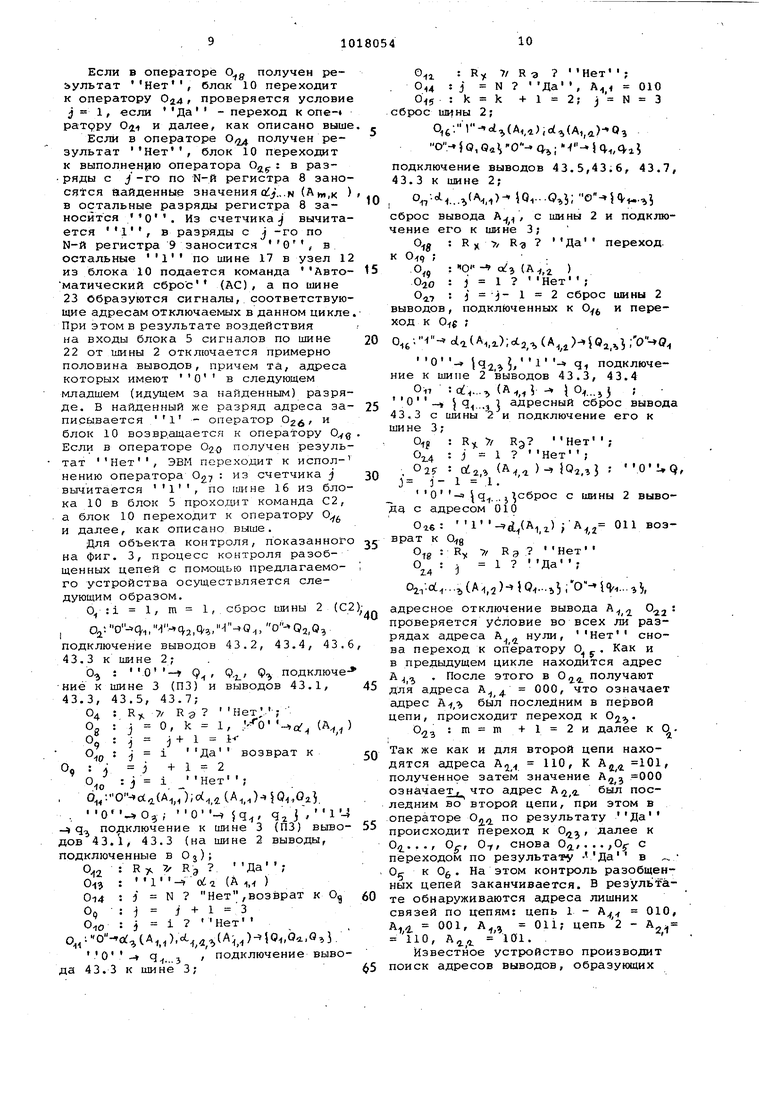

( Начало j V.Ct , , Л () I I 4i . ,j-aj . j Hem On . (Atn.t) ,.- ,...,,,.,j} „D-iQ/G.-jJ .0-П1-4Л ,-4j). Г KoHei j (j{Amk) «j... (flj.. ,.(Q/Qj- } ...N} Л ...N} 1 o(/... .-{Q о(;...мГ/4т;с;- {Л;...«}| //Me/Cj...o . ..ffJ |.(;MmJk) ., I АО oi.i...n(Amk)-(S,...Hj ..

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР 754331, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля электрических цепей | 1975 |

|

SU529432A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-05-15—Публикация

1980-03-13—Подача