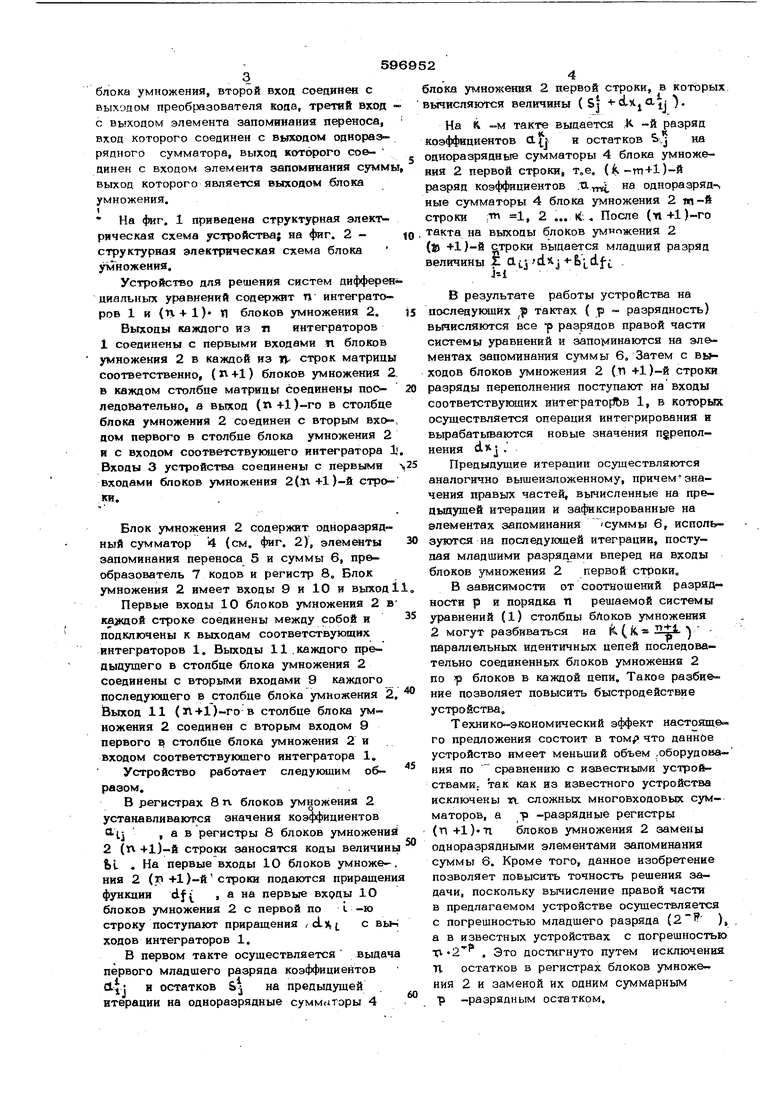

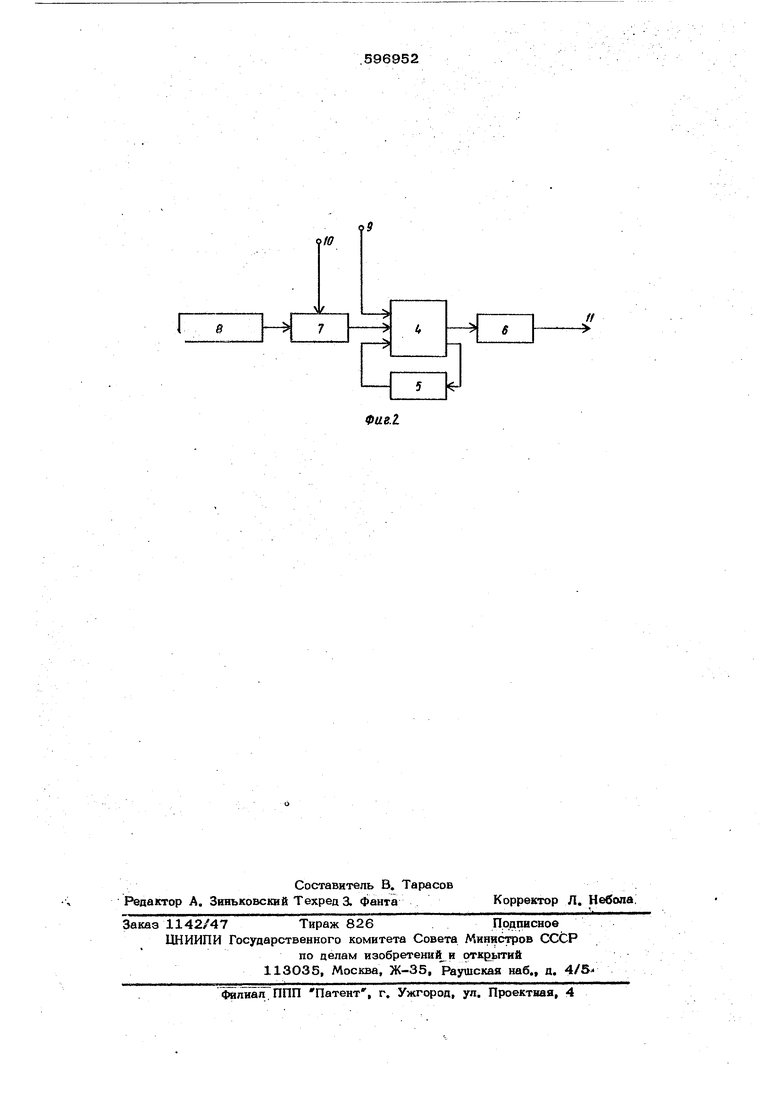

блока умножения, второй вход соецинея с выходом преобразователя коаа, третий вход с выходом элемента запоминания переноса, вход которого соедннен с выходом одноразрядного сумматора, выход которого со&динен с входом элемента запоминания сумм выход Которого является выходом блока умножения. На (Цшг. 1 приведена структурная электрическая схема устройства; на фиг. 2 - структурная электрическая схема блока умножения. Устройство для решения систем диффере циальных уравнений содержит П интеграторов 1 и (п 4- 1 ) я блоков умножения 2, Выходы каждого из п интеграторов 1 соединены с первыми входами п блоков умножения 2 в каждой из п- строк матрицы соответственно, (л +1) блоков умножения 2 в каждом столбце матрицы соединены последовательно, а выход {п+1)-го в столбце блока умножения 2 соединен с вторым входом первого в столбце блока умножения 2 и с входом соответствующего интегратора Входы 3 устройства соединены с первыми Входами блоков умножения 2(.1х+1)-и стро- ки. Блок умножения 2 содержит одноразрядный сумматор 4 (см, фиг, 2), элементы запоминания переноса 5 и суммы 6, преобразователь 7 кодов и регистр 8. Блок умножения 2 имеет входы 9 и 10 и выход Первые входы 10 блоков умножения 2 в Kaytfuou строке соединены между собой и подключены к выходам соответствующих интеграторов 1, Выходы 11 .каждого предыдущего в столбце блока умножения 2 соединены с вторыми входами 9 каждого последукщего в столбце блока умножения 2 Выход 11 (Т1+1)-гоВ столбце блока умножения 2 соединен с вторым входом 9 первого в столбце блока умножения 2 и входом соответствукнпего интегратора 1. Устройство работает следующим образом. В регистрах 8 п блоков умножения 2 устанавливаются значения коэффициентов Q-tj , а в регистры 8 блоков умножений 2 (tx -f 1)-й строки заносятся коды величины Ы , На первые входы 10 блоков умножения 2 (Т1+1)-й строки подаются приращени функции df ( , а на первые вхрды 1О блоков умножения 2 с первой по L -ю строку поступают приращения с1)(, с вьы ходов интеграторов 1, В первом такте осуществляется выдач первого младшего разряда коэффициентов Л и остатков Ь.: на предыдущей итерации на одноразрядные суммг4торы 4 5 2 лока умножения 2 первой строки, в которых вычисляются величины ( Sj -«-Ач а ). На К -м такте выдается .К -и разряд коэффициентов CLy и остатков S, на одноразрядные сумматоры 4 блока умножения 2 первой строки, т„е. ()-й разряд коэффициентов .U на одноразряд-, ные сумматоры 4 блока умножения 2 щ-й строки ;« 1, 2 .,, К; ч После (п+1)-го такта на выходы блоков умножения 2 (й +1)-й строки выдается младший разряд величины i а ц В результате работы устройства на посяедукицих р тактах { р - разрядность) вычисляются все -р разрядов правой части системы уравнений и запоминаются на элементах запоминания суммы 6. Затем с выходов блоков умножения 2 (Т) +1)-й строки разряды переполнения поступают на входы соответствукших интеграто(Л)В 1, в которых осуществляется операция интегрирования и вырабатьгоаются новые значения п§репол- нения d%j . Предыдущие итерации осуществляются аналогично вышеизложенному, причемзначения правых частей, вьгчисленные на предыдущей итерации и зафиксированные на элементах запоминания -суммы 6, используются на последу1с«цей итеграции, поступая младшими разрядами вперед на входы блоков умножения 2 первой строки, В зависимости от соотношений разрядности р и порядка п решаемой системы уравнений (1) столбцы блоков умножения 2 могут разбиваться на Й({. параллельных идентичных цепей последовательно соединенных блоков умножения 2 по р блоков в каждой цепи. Такое разбиение позволяет повысить быстродействие устройства, Технико-экономический эффект настояще. го предложения состоит в том; что данное устройство имеет меньший объем .оборудова- ния по сравнению с известными устройствамИр так как из известного устройства исключены п сложных многовходовьвс сумматоров, а -р -разрядные регистры (n +1)-тг блоков умножения 2 замены одноразрядными элементами запоминания суммы 6, Кроме того, данное изобретение позволяет повысить точность решения задачи, поскольку вычисление правой части в предлагаемом устройстве осуществляется с погрешностью младшего разряда ( ), . а в известных устройствах с погрешностью T;V «2 , Это достигнуто путем исключения П остатков в регистрах блоков умножения 2 и заменой их одним суммарным р -разрядным остатком.

5

,р е т е н и и

Формулаи

3 о

1. Устройство для решения систем диференциальных уравнений, содержащее ий-, теграторы, матрицу блоков умножения,2

причем, выход каждого интегратора соединен с первыми входами блоков умножения соответствующей строки матрицы, первые Ьходы блоков умножения последней строки матрицы соединены с входами устройства, .отличающееся тем, что, с целью упрощения и повьппения точности, блоки умножения каткдого столбца соединены последовательно, выход каткдого из блоков умножения последней строки соединен с дом соответствующего интегратора и вторыми входами соответствующих блоков умножения первой строки матрицы.

2. Устройство по п. 1, отличаю - щ е -е с я тем, что блок умножения со- 20

держит регистр, преобразователь кода, первый вход которого соединен с выходом регистра, второй вход является первым входом блока умножения, одноразрядньтй сумматор, первый вход которого соединен с вторым входом блока умножения; второй вход Соединен с выходом преобразователя Кода, третий , вход с выходом элемента запоминания переноса, вход которого соединен с выходом одноразрядного сумматора, выход которого соединен с входом элемента запоминания суммы, вьпсод которого является ВЫХС11ДОМ блока умножения.

Источники информации, принятые во внн- мание при экспертизе:

1.Майоров Ф, М. Электронные цифровые интегрируклцие машины, М., Машгиз, 1962.

2.Воронов А. А. и др. Цифровые ана- . логи для систем автоматического уиравле- ния, М,. АН СССР, I960.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ и диф-фЕРЕНциАльНыХ уРАВНЕНий | 1978 |

|

SU798860A1 |

| Устройство для вычисления сумм произведений | 1973 |

|

SU480077A1 |

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811275A1 |

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

Авторы

Даты

1978-03-05—Публикация

1975-04-28—Подача