(54) ОДНОФАЗНЫЙ ИНВЕРСНЫЙ Д-ТРИГГЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОФАЗНЫЙ ИНВЕРСНЫЙ Д-ТРИГГЕР | 1973 |

|

SU405167A1 |

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064471A1 |

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| @ -Триггер с предпочтительной установкой в @ -состояние | 1982 |

|

SU1075380A1 |

| Генератор импульсов | 1975 |

|

SU570185A1 |

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064470A1 |

| Динамический триггер на моптранзисторах | 1976 |

|

SU657594A1 |

| Логический элемент Исключающее ИЛИ | 1982 |

|

SU1072264A1 |

1

Изобретение относится к цифровой вычислительной технике, предназначено для построения вычислительных устройств в интегральном исполнении.

Известен Д-триггер на МОП-транзисtopax со взаимодополняющей симметрией содержащий три инвертора, входную, тактирующую,, выходную и общие шины и два последовательных ключа, каждый из которых состоит из двух параллельно включенных транзисторов разных типов проводимости, на затворы которых подается в противофазе тактирующий сигнал l.

Этот триггер имеет сложную схему.

Известен однофазный инверсный Дтриггер на МОП-транзисторах со взаимодополняющей симметрией, содержащий двухвходовый элемент ИЛИ-НЕ, два блокрующих транзистора п-типа и два вентильных транзистора р-типа, входную, тактирующую, выходную и общую шины; . истоки блокирующих транзисторов соединены с o6ui,eA шиной, стоки первых вентильного и блокирующего транзисторов подключены к первому входу элемента ИЛИ-НЕ, стоки вторых вентильного и блокирующего транзисторов подключены ко второму входу элемента ИЛИ-НЕ, затворы первых вентильного и блокирующего транзисторов.соединены с истоком второго вентильного транзистора и с тактирующей шиной, затворы вторых вентильного и блокирующего транзисторов соединены с выxoдJpм элемента ИЛИНЕ и с выходной шиной; исток первого вентильного транзистора соединен со входной шиной 2.

Этот Д-триггер недостаточно устойчив против помех в процессе записи информации.

Цель изобретения - повышение помехоустойчивости д-триггера.

Для достижения этой цели в Д-триггер на МОП-транзисторах со взаимодополняющей симметрией, содержащий двухвходовый элемент ИЛИ-НЕ, два блокирующих транзистора п-типа и два в нтильных транзистора р-типа, входную, тактируквдую, выходную и общую шины; причем истоки блокирующих транзисторов соединены с общейшиной, стоки первых вентильного и блокирующего транзисторов подключены к первому входу элемента ИЛИ-НЕ, стоки вторых вентильного и блокирующего транзисторов подключены ко второму входу элемента ИЛИ-НЕ, затворы первых вентильного и блокирующего транзисторов соединены и истоком второго вентильного транзистоpa И С тактирующей шиной, затворы вторых вентильного и блокирующего транзисторов соединены с выходом эле/иента ИЛИ-НЕ.и с ёыходной шиной, исток первого вентильного транзистора соединен со входной шиной, параллельно вентильным транзисторам введены форсирующие транзисторы п-типа, затворы которых соединены со своими истоками

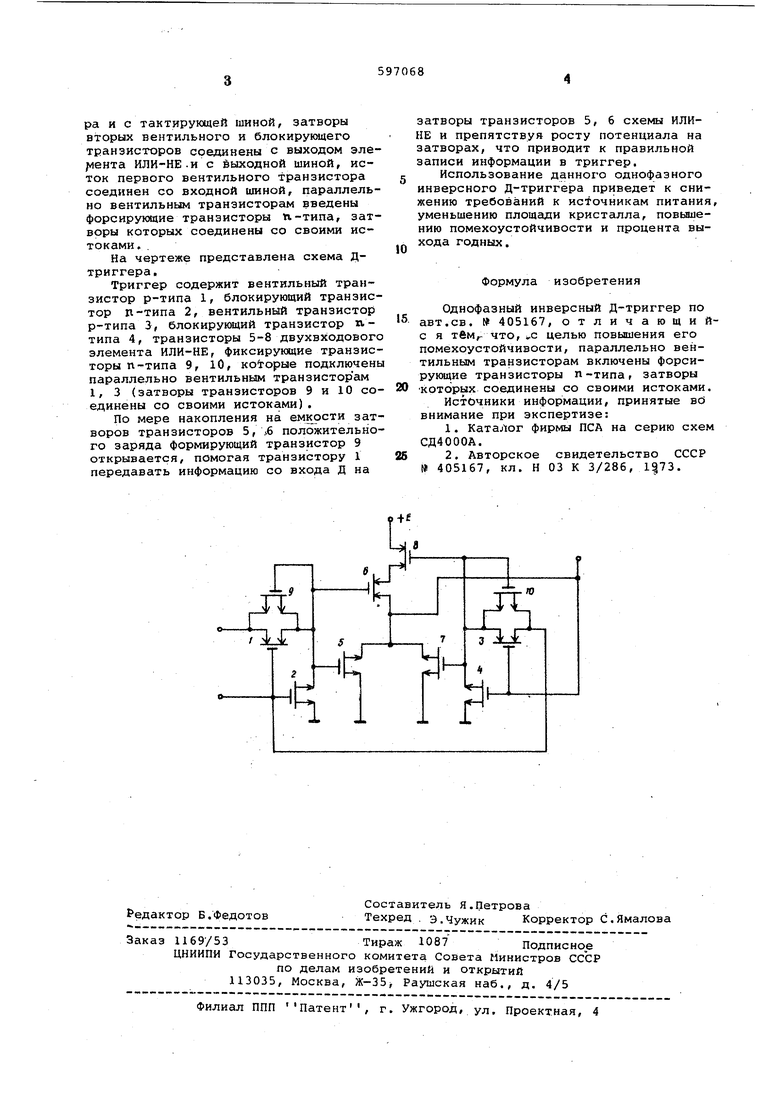

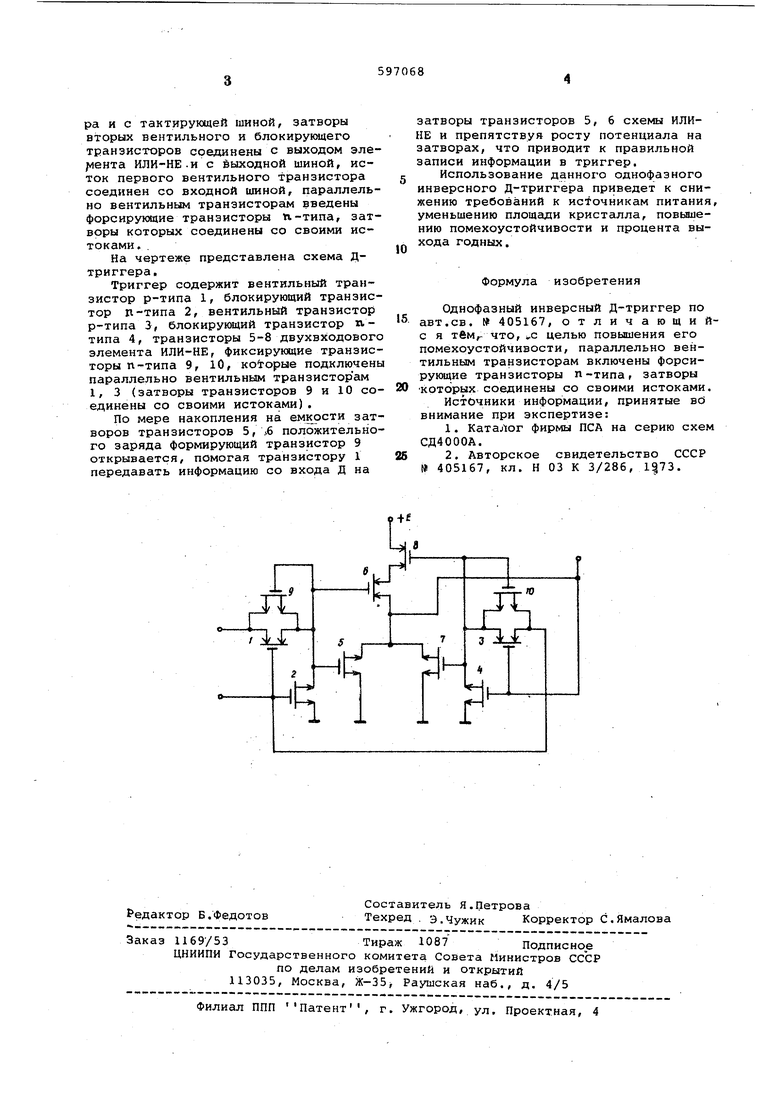

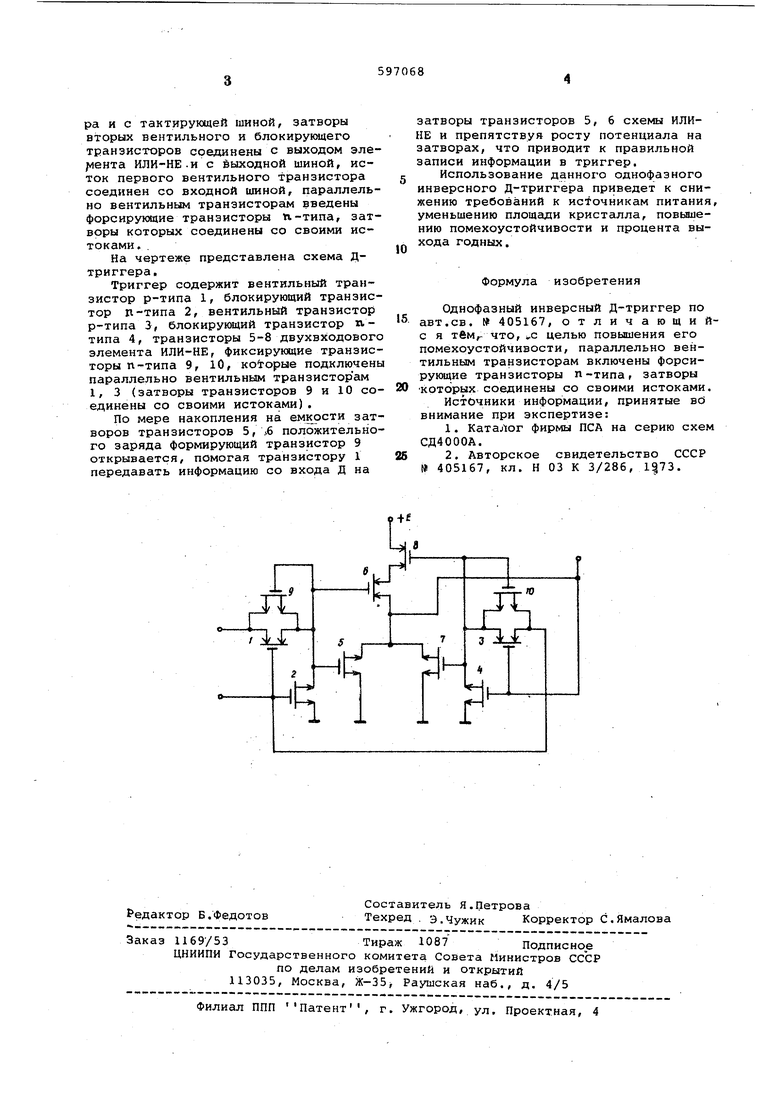

На чертеже представлена схема Дтриггера.

Триггер содержит вентильный транзистор р-типа 1, блокирующий транзистор п-типа 2, вентильный транзистор р-типа 3, блокирующий транзистор п,типа 4, транзисторы 5-8 двухвходового элемента ИЛИ-НЕ, фиксирующие транзисторы п-типа 9, 10, ко орые подключены параллельно вентильным транзисторам 1, 3 (затворы транзисторов 9 и 10 соединены со своими истоками).

По мере накопления на емкости затворов транзисторов 5, j6 положительного заряда формирующий транзистор 9 открывается, помогая транзистору 1 передавать информацию со входа Д на

затворы транзисторов 5, б схемы ИЛИНЕ и препятствуя росту потенциала на затворах, что приводит к правильной записи информации в триггер.

Использование данного однофазного инверсного Д-триггера приведет к снижению требований к источникам питания, уменьшению площади кристалла, повьниению помехоустойчивости и процента выхода годных.

Формула изобретения

Однофазный инверсный Д-триггер по авт.св. № 405167, отличающийс я твм,- что, 1,с целью повышения его помехоустойчивости, параллельно вентильным транзисторам включены форсирующие транзисторы п-типа, затворы которых соединены со своими истоками.

Источники информации, принятые вО внимание при экспертизе:

Авторы

Даты

1978-03-05—Публикация

1976-11-19—Подача