Изобретение Относится к области вычислительной техники и предназначено для построения управляющих вычислительных систем.

Известно устройство, содержащее двухвходовую схему «ИЛИ-НЕ, два блокирующих транзистора «,-типа и два вентильных транзистора /7-типа, входную, тактирующую, выходную и общую щины.

Тажой триггер имеет относительно больщое количество транзисторов и квазистатический режим работы, не обеспечивающий длительного хранения информации, вследствие чего ограничивается построение на этих триггерах управляющих вычислительных систем.

Для обеснечения длительного хранения информации и упрощения триггера, в пеаМ истоки блокирующих транзисторов соединены с общей щиной, стоки первых вентильного и блокирующего транзисторов подключены к первому входу двухвходовой схемы «ИЛИ -- НЕ, стоки вторых вентильного и блокирующего транзисторов - к второму входу двухвходовой схемы «или-НЕ. Затворы первых вентильного и блокирующего транзисторов соединены с истоком второго вентильного транзистора и с та ктирующей шиной, затводы вторых вентильного и блокирующего транзисторов - с выходом двухвходовой схемы «ИЛИ-НЕ и с выходной щиной, а исток

первого ве ггильного транзистора связан с входной щиной.

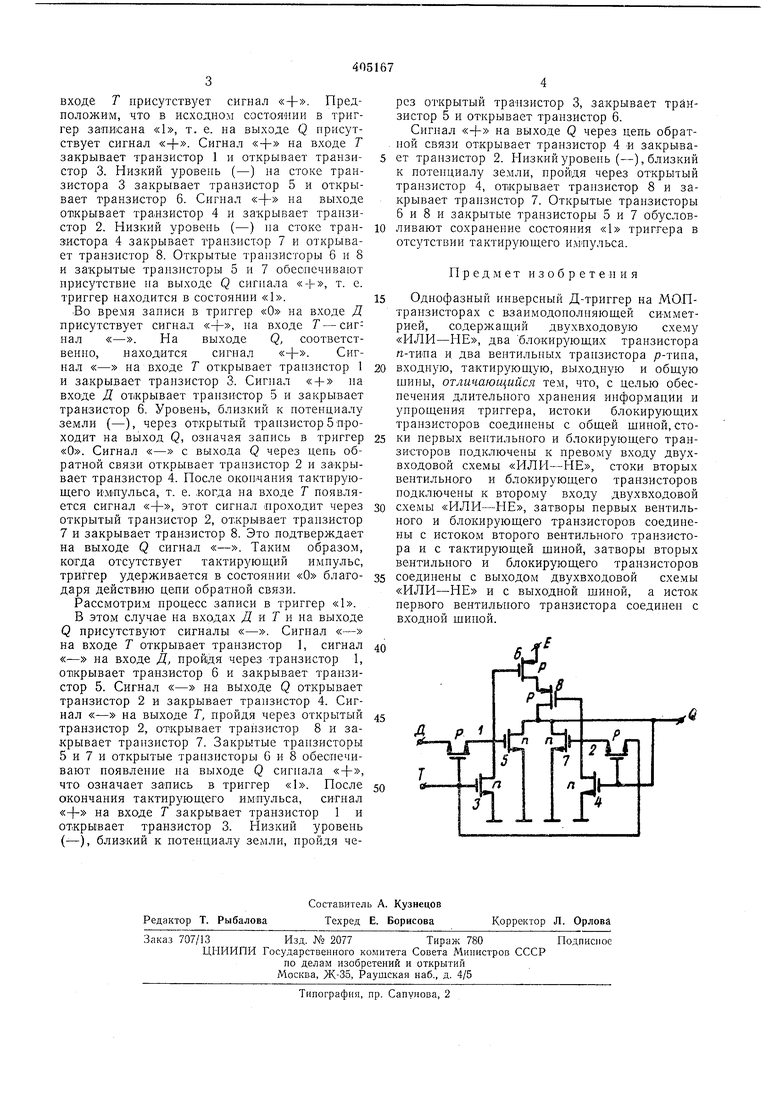

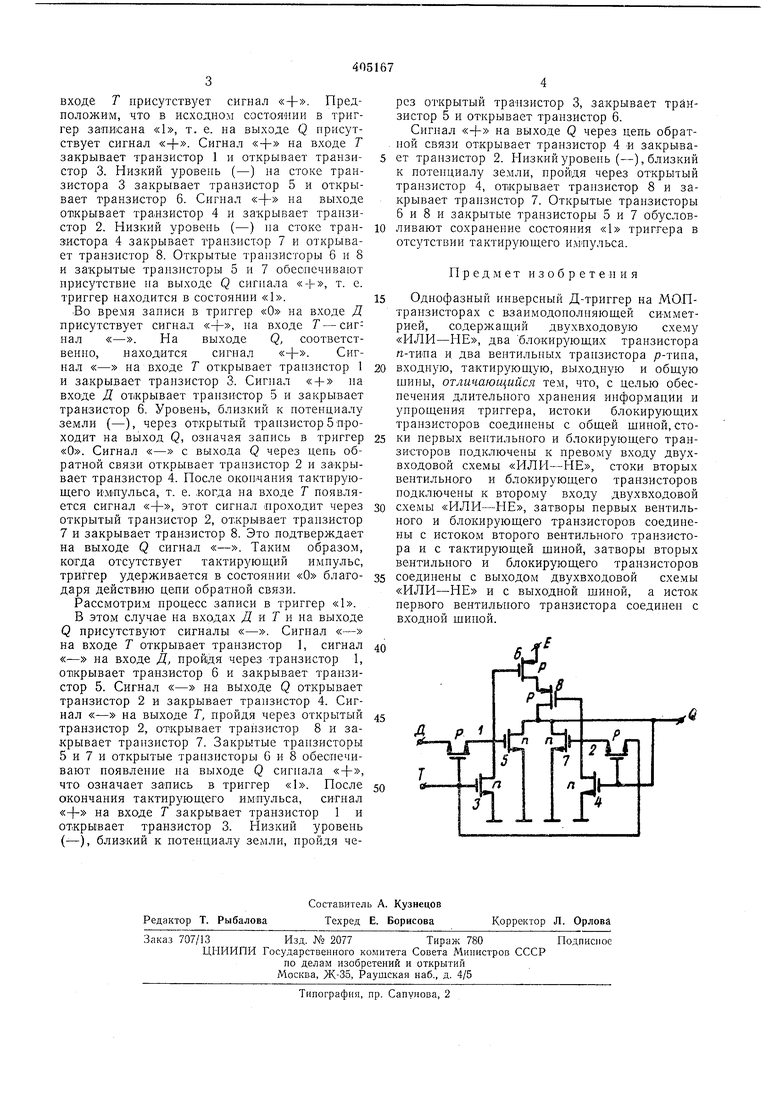

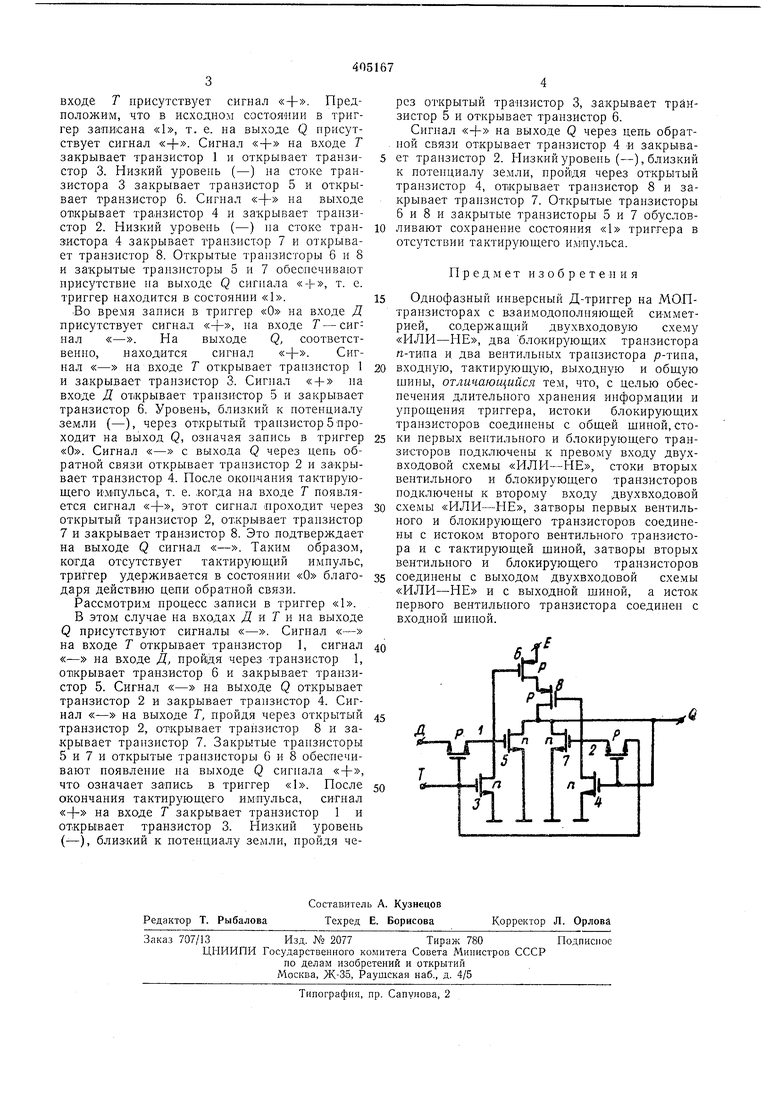

На чертеже ноказана принципиальная схема однофазного инверсного Д-триггера, собранного на вентильных трапзистрах р-типа 1 и 2, блокирующих трандисторах п-типа 3 и 4, транзисторах 5-8 схемы «ИЛИ-НЕ.

Выходом а триггера является выход двухвходовой схемы «или-НЕ, к входам которой подключены вентильные транзисторы ртина 1 и 2 и блокирующие транзисторы п-типа 3 и 4. Истоки блокирующих транзисторов заземлены, стоки первых вентильного 1 и блокирующего 3.транзисторов объединены н нодключены к первому входу схемы «ИЛИ-НЕ. Стоки вторых вентильного 2 и блокнруюн1ег() 4 транзисторов объединены и подключетнл к второму входу схемы «ИЛИ-НЕ.

Затворы первых вентильного и блокирующего транзисторов объединены с истоком второго вентильного транзистора, образуя тактирующий вход Т триггера. Затворы вторых вентильного и блокирующего транзисторов соединены с выходом Q схемы «ИЛИ- НЕ, а исток первого вентильного транзнстора является информационным входом Д триггера.

Триггер тактируется импульсами отрицательной полярности (-). Рассмотрим исходное состояние триггера, когда на его

| название | год | авторы | номер документа |

|---|---|---|---|

| Однофазный инверсный д-триггер | 1976 |

|

SU597068A2 |

| ПАРАФАЗНЫЙ Д-ТРИГГЕР | 1973 |

|

SU395971A1 |

| СЧЕТНЫЙ ТРИГГЕР НА МДН-ТРАНЗИСТОРАХ | 1973 |

|

SU369717A1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| Ключевой элемент на моп-транзисторах | 1972 |

|

SU455488A1 |

| Динамический триггер на моптранзисторах | 1976 |

|

SU657594A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Формирователь суммы на мдп-транзисторах | 1972 |

|

SU516038A1 |

| Триггер на МПД-транзисторах | 1984 |

|

SU1223349A2 |

| Д-триггер на полевых транзисторах | 1984 |

|

SU1347153A1 |

Даты

1973-01-01—Публикация