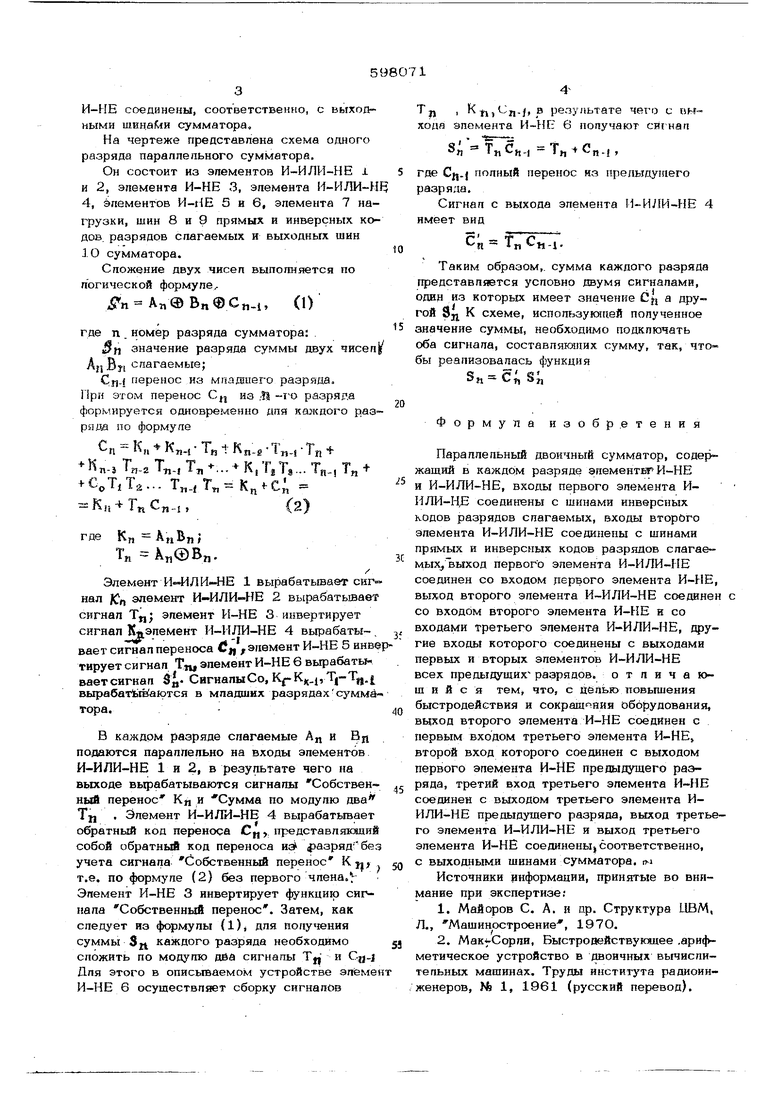

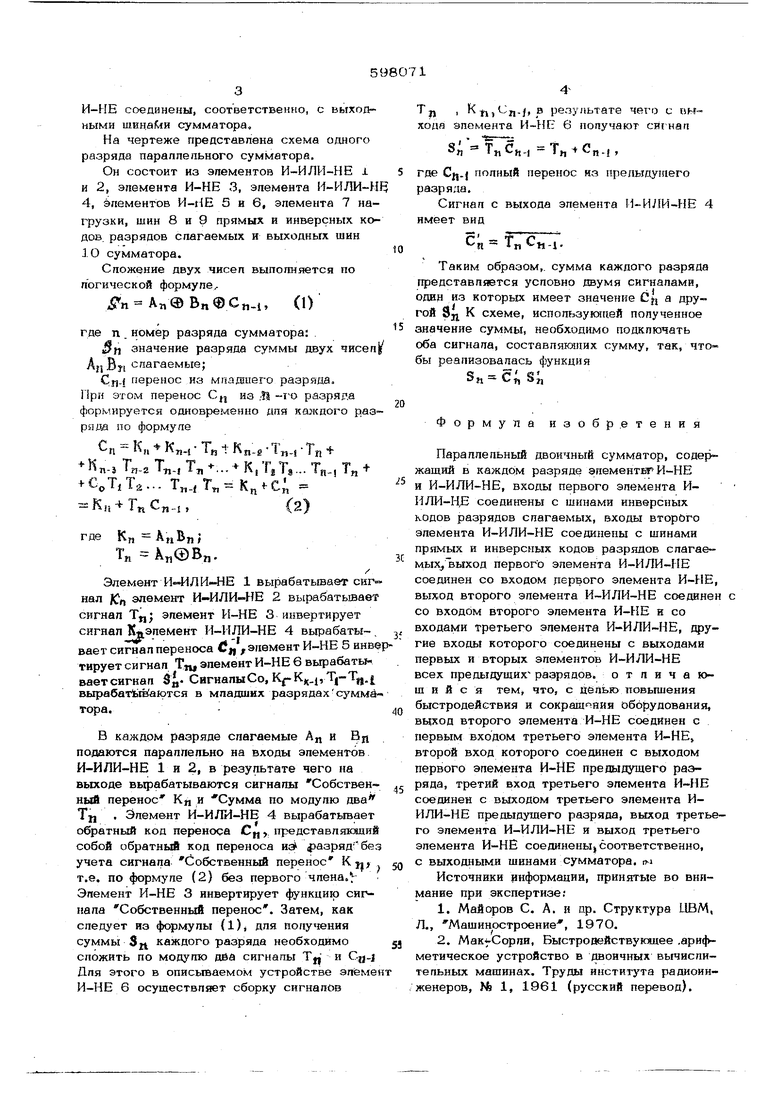

(54) ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ СУММАТОР И-НЕ соединены, соответственно, с выхоймыми шинаЛ{и сумматора. На чертеже представпена схема одного разряда параппельного сумматора. Он состоит из элементов И-ИЛИ-НЕ i и 2, эпемента И-НЕ 3, элемента И-ИЛИ-Н 4, элементов И-НЕ 5 и 6, эпемента 7 наПзуаки, шин 8 и 9 прямых и инверсных ко дов, разрядов слагаемых и выходных шин 1О сумматора. Сложение двух чисеп выполняется по логической формуле, лб п-А„@ВпФС„.1, (1) где п . номер разряда сумматора: Sn значение разряда суммы двух чисел AIJ Ву1 слагаемые; Cn-i перенос из мсгашиего разряда. При этом перенос Сд на -го разряда форлшруется одновременно для кам{дого раз ряда по формуле Сп К„ + К Т„ 1 Kn-s Т„., Т„ -ь Kn.j V, Т ... К.ТгТ,... Тп-, Т„ t СоТ,т.... т„.,т« - Kit Гц Сп-1 } К„ - А„ВП; Т- k /т о и А„(±)ВП Элемент И-ИЛИ-НЕ 1 вырабатьшает сиг нал JC элемент И-ИЛИ-НЕ 2 вырабатывает сигнал Т„; элемент И-НЕ 3 инвертирует сигнап К«элемент И-1ШИ-НЕ 4 вырабатывает сигнал переноса „, элемент И-НЕ 5 инв тирует сигнал Тп, эпемеят И-НЕ 6 вырабатывает сигнал За- Сигналы Со, Kf-K.l,T|-T,j. вырабат4 гё(а1отся в младших разрядахcjMMa тора.В каждом разряде слагаемые АП и В ц подаются параллельно на входы элементов И-ИЛИ-НЕ 1 и 2, в результате чего на выходе вьфабатываются сигналы Собственный перенос Kji и Сумма по модулю два Тп . Элемент И-ИЛИ-НЕ 4 вырабатьгаает обратный код переноса С ,, представлякяыий собой обратный код переноса иа разряд бе учета сигнала Собственный перенос Кд т.е. по формуле (2) без первого члена. Элемент И-НЕ 3 инвертирует функцию сигнала Собственный перенос . Затем, как следует из формулы (1); для получения суммы Sjt каждого разряда необходимо сложить по модулю дйа сигналы Тд и CQ-J Для этого в описываемом устройстве элеме И-НЕ 6 осуществляет сборку сигналов п tit -n-fP результате чего с «нхода эпемента И-НГ: 6 получают снгнап s;-veh-i Tn Cn.,, где Сц.} полный перенос из предыдущего разряда. Сигнал с выхода элемента И-ИЛИ-НЕ 4 имеет вид П Тг, Ctt-i. Таким образом,, сумма каждого разряда представляется условно двумя сигналами, один из которых имеет значение Cjj а другой Sji К схеме, использующей полученное значение суммы, необходимо подключать оба сигнала, составляю5 1их сумму, так, чтобы реализовалась функция S е и t П Формула изобретения Параллельный двоичный сумматор, содержащий в каждом разряде эпементвг И-НЕ и И-ИЛИ-НЕ, входы первого элемента ИИЛИ-Н В соединены с шинами инверсных кодов разрядов слагаемых, входы второго элемента И-ИЛИ-НЕ соединены с шинами прямых и инверсных кодов разрядов слагаемых Ъыход первого элемента И-ИЛИ-НЕ со входом первого элемента И-НЕ, выход второго элемента И-ИЛИ-НЕ соединен с со входом второго элемента И-НЕ и со входами третьего элемента И-ИЛИ-НЕ, другие входы которого соединены с выходами первых и вторых элементов И-ИЛИ-НЕ всех предыдуш;их разрядов, отличающийся тем что, с целью повышения быстродействия и сокрашс ния оборудования, выход второго элемента И-НЕ соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ предыдущего разряда, третий вход третьего элемента И-НЕ соединен с выходом третьего элемента ИИЛИ-НЕ предыдущего разряда, выход третьего элемента И-ИЛИ-НЕ и выход третьего элемента И-НЕ coeдинeныJ соответственно, с выходными шинами сумматора, гм Источники информации, принятые во внимание при экспертизег 1.Майоров С. А. и пр. Структура LIBM, Л., Машиностроение, 197О. 2.Мак Сорпи, Быстродействующее .арифметическое устройство в двоичных вычислительных машинах. Труды института радиоинженеров, hfe 1, 1961 (русский перевод).

VB

vi}J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения и вычитания чисел | 1975 |

|

SU598072A1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| ОДНОРАЗРЯДНОЕ СУММИРУЮЩЕЕ УСТРОЙСТВО КОМБИНАЦИОННОГО ТИПА ДЛЯ КОДА 8-4-2—1 | 1973 |

|

SU407309A1 |

| Устройство для суммирования и вы-чиТАНия дВОичНО-дЕСяТичНыХ КОдОВ | 1978 |

|

SU813415A1 |

| Параллельный сумматор кодов фибоначчи | 1984 |

|

SU1180880A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ВО) И УСТРОЙСТВО ИХ РЕАЛИЗАЦИИ | 2016 |

|

RU2641218C1 |

| Ячейка однородной структуры | 1990 |

|

SU1805461A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

i4gvdevd anmdvwy g

Авторы

Даты

1978-03-15—Публикация

1971-07-12—Подача