Изобретение относится к области вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и устройствах цифровой автоматики. Известны способы и устройства выполнения вычислительных операций сложения (ОС), логического сложения (ОЛС) и логического умножения (ОЛУ). Упомянутые способы и устройство рассмотрены в книге М.А. Карцева «Арифметика цифровых машин», издательство "Наука", 1969 г. Стр. 147-156, рис. 2-8, 2-9, стр. 552-554. Общим недостатком выполнения ОС является необходимость формирования сигнала переноса и распространение его от младших разрядов до самого старшего разряда. В том случае, если в первом разряде слагаемые A1=B1=1, вырабатывается поразрядный сигнал переноса, равный Pi'=A1B1, который распространяется до n-го разряда, если слагаемые всех старших разрядов равны Ai V Bi=1, то максимальная временная задержка переноса будет равна Тз=2nτ (τ - задержка переключения элемента И, ИЛИ; n - число разрядов суммирующего устройства (СУ)), что определяет время выполнения ОС, при прочих равных условиях. Для снижения времени распространения сигнала переноса применяются различные схемы ускорения формирования переноса, но это требует дополнительных затрат оборудования, повышения энергопотребления и дополнительных финансовых расходов. Наиболее близким прототипом предлагаемого устройства является сумматор комбинационного типа, схема которого приведена в упомянутой книге М.А. Карцева, стр. 152, рис. 2-8. По принципу работы и затратам электронного оборудования прототип и предлагаемое СУ совпадают. Но быстродействие прототипа зависит от числа двоичных разрядов, а предлагаемое устройство не зависит от этого показателя, и максимальное время задержки переноса всегда равно длительности первого временного такта t1, что делает быстродействие СУ независимым от числа двоичных разрядов. Кроме того, предложенные способы и устройство обеспечивают расширение функциональных возможностей предлагаемого СУ за счет выполнения ОЛС и ОЛУ при минимальных затратах дополнительного оборудования.

Для реализации способов выполнения ВО предложено устройство, каждый разряд которого построен на основе четырех элементов И, четырех элементов ИЛИ, одного элемента НЕ и трех входов управления (ВУ) выполнением элементарных операций формирования имитационного потенциала переноса ВУ1 и входами ВУ2, 3 выполнением операции логического сложения и логического умножения, трех информационных входов Ai, Bi, Pi-1 и двух информационных выходов Pi, Si.

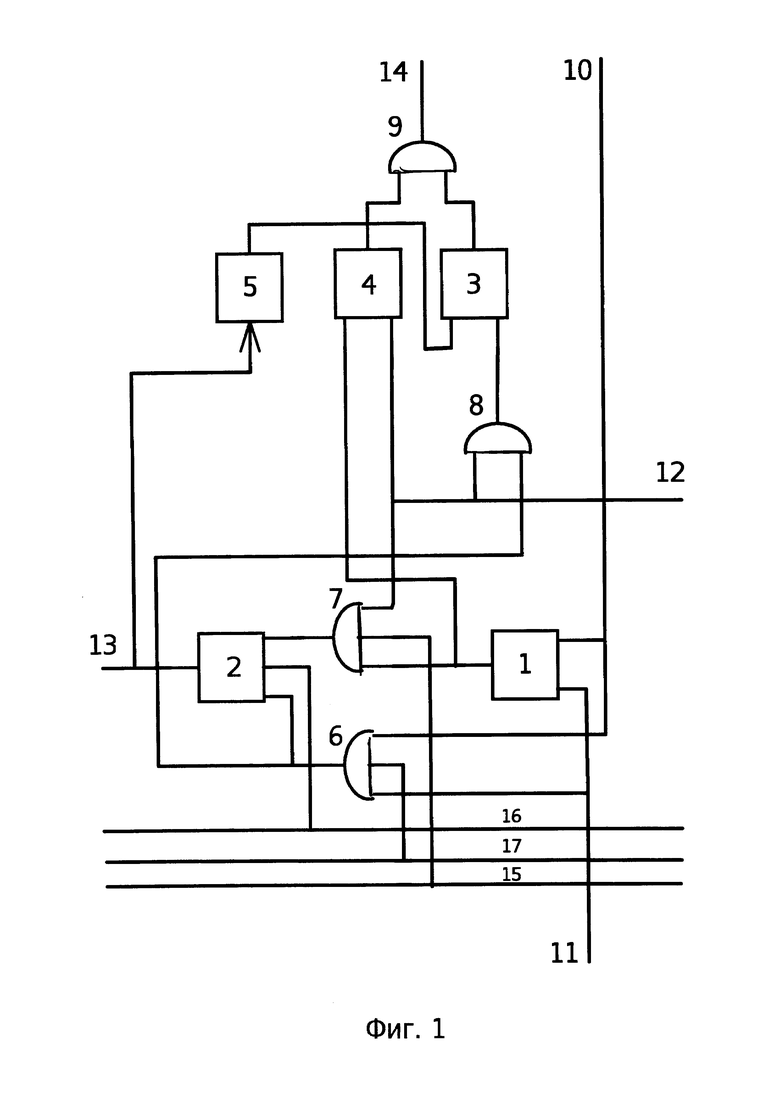

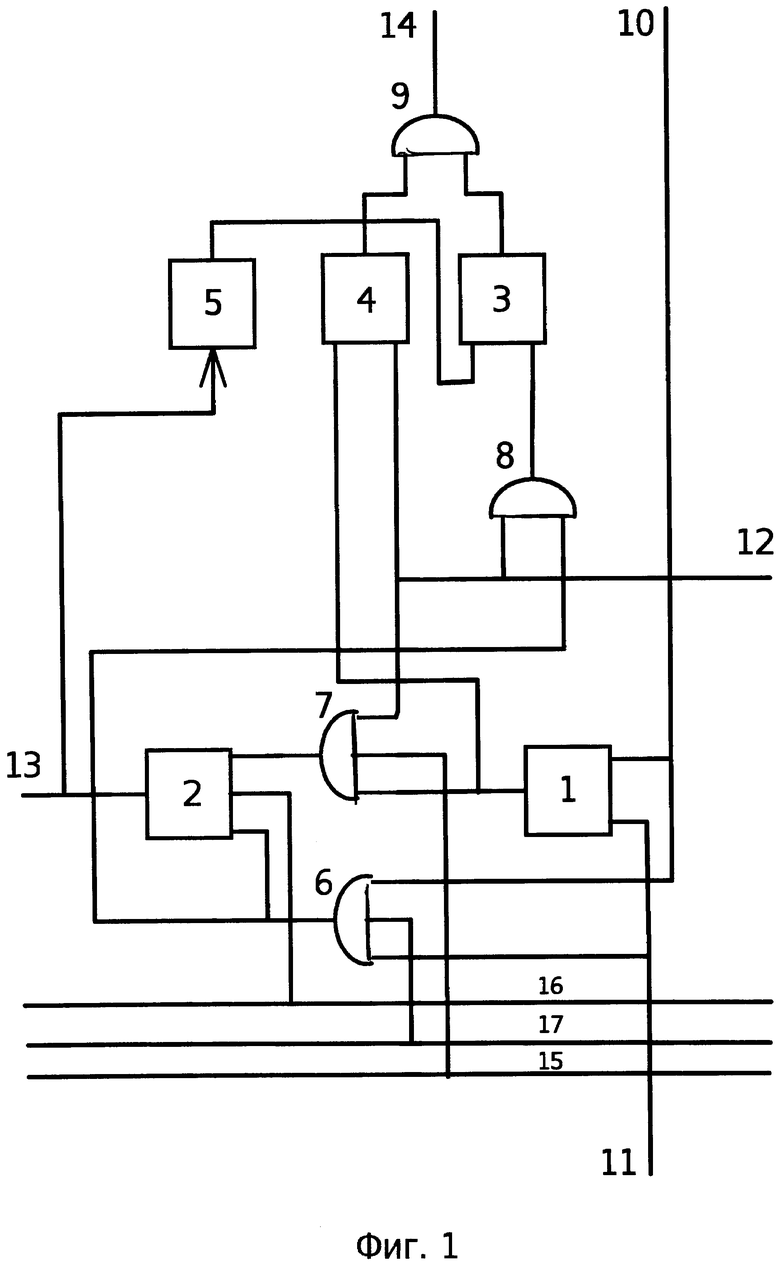

Для пояснения работы устройства при выполнении ВО на фиг. 1 приведена функциональная схема одного разряда СУ. На фиг. 1 приняты следующие обозначения: элементы И 1-4, элемент НЕ 5, элементы ИЛИ 6-9, первый - третий информационные входы (ИВ) 10-12, первый и второй информационные выходы (ИВых) 13, 14, первый вход управления ВУ1 формированием имитационного потенциала переноса (ИПП) 15, второй ВУ2 выполнением ОЛС 16, третий ВУ3 выполнением ОЛУ 17.

Устройство выполнено следующим образом. Информационные входы 10 и 11 соединены с входами И1 и ИЛИ6. Вход 12 соединен с ИЛИ 8, 7, И4. Выход И1 соединен с входами И4, ИЛИ7. Первый ВУ 15 подключен к входу ИЛИ7, выход которого соединен с И2. Выход 13 является первым информационным выходом Pi, выработанным в i-м разряде. Вход 16 подключен к входу И2. Вход 17 соединен с входом ИЛИ1. Выход И2 через НЕ5 соединен с И3. Выход ИЛИ8 связан с вторым входом И3, выход которого подключен к входу ИЛИ9. Выходы И3, 4 соединены с входами ИЛИ9, выход 14 является вторым информационным выходом Si.

Рассмотрим выполнение ВО. В исходном состоянии до начала выполнения ВО на ИВ 10-12 и ИВых 13, 14 отсутствуют высокие потенциалы (ВП). На ВУ 16 присутствует ВП, который разрешает работу И2, при наличии ВП на остальных входах упомянутого элемента.

1. Выполнение ОС. Операция выполняется за два временных такта t1 и t2. По t1 на ИВ10, 11 поступают ВП с единичных выходов триггеров n-разрядных регистров А и В (на фиг. 1 регистры не приводятся). В случае Ai=Bi=1 на выходе И1 формируется ВП поразрядного сигнала переноса i-го разряда Pi', на выходе ИЛИ6 также будет сформирован ВП при Ai V Bi=1. Упомянутые сигналы вырабатывают на выходе И2 потенциал переноса (ПП) в старший разряд. Одновременно ВП с И2 через НЕ5 запретит работу И3. Если в i-й разряд по входу 12 поступит сигнал переноса из i-1-го разряда, то на выходе 14 будет сформирован результат суммы i-го разряда Si=1. Потенциал переноса по выходу 13 будет проходить через все старшие разряды СУ, если в этих разрядах Ai V Bi=1, при этом максимальная временная задержка ПП при его прохождении из первого разряда в самый старший разряд будет равна Тз=2nτ (τ - задержка одного элемента И (ИЛИ), n - число разрядов СУ). Для исключения Тз в предлагаемом устройстве введен первый ВУ1 формированием имитационным потенциалам переноса, подключенный к третьему входу ИЛИ7. Это позволяет исключить время задержки формирования ПП при выполнении ОС. Таким образом, по t1 будут сформированы имитационные потенциалы переносов в тех разрядах, в которых Ai=Bi=1, и имитационные потенциалы переноса в каждом разряде, кроме тех разрядов, в которых Ai=Bi=0. По t2, после снятия ВП с первого ВУ15 формированием ИПП, в каждом разряде СУ останутся только реальные потенциалы переносов и реальные результаты суммирования двоичных кодов двух n-разрядных регистров А и В согласно соотношениям: Pi = AiBi v [Pi-1(Ai v Bi)]=1…1.1,  здесь Pi, Si - потенциалы переноса и суммы, выработанные в i-м разряде;

здесь Pi, Si - потенциалы переноса и суммы, выработанные в i-м разряде;  - инверсное значение Pi; Pi-1 - потенциал переноса, выработанный в i-1-м разряде, результат выполнения ОС выдают из суммирующего устройства с выходов элементов ИЛИ9 на вторые информационные выходы Si 14.

- инверсное значение Pi; Pi-1 - потенциал переноса, выработанный в i-1-м разряде, результат выполнения ОС выдают из суммирующего устройства с выходов элементов ИЛИ9 на вторые информационные выходы Si 14.

2. Выполнение ОЛС. Операция выполняется за один временной такт t1. По первому такту принимают в каждый разряд СУ по входам 10 и 11 слагаемые Ai и Bi. Снимают ВП с ВУ16, чем запрещают работу И2, при этом на выходе НЕ5 будет ВП, разрешающий прохождение Ai v Bi=1 с ИВ 10, 11 по цепи элементов ИЛИ6, 8, И3, ИЛИ9 на второй информационный выход Si14. На этом выполнение операции заканчивают.

3. Выполнение ОЛУ. Операция выполняется за один временной такт t1. По этому такту принимают по входам 10 и 11 первый и второй сомножители Ai и Bi. Подают одновременно ВП на входы 15 и 17, при этом на выходе 13 будет высокий потенциал, который через третий информационный вход 12 поступит на вход И4 старшего разряда. Если на входы 10 и 11 i-го разряда поступили коды "1", то с выхода И1, через И4 первого старшего разряда ИЛИ9, на второй информационный выход 14 поступит ВП, что соответствует результату ОЛУ, равному "1". При всех других значениях сомножителей, поступивших на входы 10 и 11, на выходе будет отсутствовать ВП, т.е. результат ОЛУ будет равен "0". На этом операцию завершают.

Таким образом, предложенные способы и устройство их реализации позволяют выполнять ОС без временных задержек ПП, что обеспечивает повышение быстродействия СУ, расширить функциональные возможности за счет выполнения ОЛС и ОЛУ при минимальных затратах аппаратурных средств (20 входов логических элементов против 17 у прототипа).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| СЧЕТЧИК ИМПУЛЬСОВ (СИ) | 2015 |

|

RU2579524C1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2505850C2 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2013 |

|

RU2537046C2 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2388041C2 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| Сумматор-вычислитель на элементах нейронной логики | 2019 |

|

RU2715177C1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство поразрядного вычисления логических и арифметических операций | 2020 |

|

RU2739343C1 |

| Устройство для определения экстремальных чисел | 1990 |

|

SU1753468A1 |

Группа изобретений относится к области вычислительной техники и может быть использована в процессорных устройствах ЭВМ и устройствах цифровой автоматики. Техническим результатом является повышение быстродействия выполнения операции сложения и расширение функциональных возможностей устройства за счет выполнения операций логического сложения и логического умножения при минимальных затратах оборудования. Каждый двоичный разряд устройства содержит четыре элемента И, четыре элемента ИЛИ, один элемент НЕ, три информационных входа, два информационных выхода, три входа управления. 4 н.п. ф-лы, 1 ил.

1. Способ выполнения операции сложения ОС двух n-разрядных кодов на основе использования оборудования сумматора комбинационного типа СУ, содержащего в каждом двоичном разряде первый - четвертый элементы И, первый - четвертый элементы ИЛИ, один элемент НЕ, первый - третий информационные входы ИВ, на которые поступают сигналы с выходов триггеров i-го разряда Ai, Bi и сигнал переноса из i-1-го разряда Pi-1 соответственно, при этом Ai и Bi соединены с входами первых элементов И, ИЛИ, третий информационный вход Pi-1 соединен с входами третьего, второго элементов ИЛИ и четвертого элемента И, первый вход второго элемента ИЛИ подключен к выходу первого элемента И и ко второму входу четвертого элемента И, выходы первого и второго элементов ИЛИ соединены со вторым и первым входами второго элемента И, выход первого элемента ИЛИ также подключен к входу третьего элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, выход второго элемента И является первым информационным выходом Pi и через первый элемент НЕ соединен со вторым входом третьего элемента И, выходы третьего и четвертого элементов И соединены с входами четвертого элемента ИЛИ, выход которого является вторым информационным выходом Si, отличающийся тем, что в состав устройства введен первый вход управления 1ВУ выработкой имитационного потенциала переноса ИПП, подключенного к третьим входам вторых элементов ИЛИ каждого разряда, по t1 на 1ВУ подают ВП, который формирует имитационный перенос P'i=1 и имитационную сумму S'i=1 во всех разрядах, кроме разрядов, в которых Ai=Bi=0, по t2 снимают ВП с 1ВУ, за счет чего в каждом разряде СУ одновременно формируются реальные результаты Si и Pi, т.е. реальная сумма двух n-разрядов, на этом операция сложения двух n-разрядных чисел заканчивается.

2. Способ выполнения операций логического сложения ОЛС двух n-разрядных кодов на основе использования оборудования сумматора комбинационного типа СУ, содержащего в каждом двоичном разряде первый - четвертый элементы И, первый - четвертый элементы ИЛИ, первый элемент НЕ, первый - третий информационные входы ИВ, на которые поступают сигналы с выходов триггеров i-го разрядов Ai, Bi и сигнал переноса из i-1-го разряда Pi-1 соответственно, первый и второй входы Ai, Bi подключены к входам первых элементов И, ИЛИ, третий информационный вход, выработанный в младшем разряде Pi-1, подключен к входам второго и третьего элементов ИЛИ и четвертого элемента И, выход первого элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход первого элемента ИЛИ подключен ко второму входу второго элемента И и к входу третьего элемента ИЛИ, выход второго элемента И через первый элемент НЕ связан со вторым входом третьего элемента И, первый вход которого подключен к выходу третьего элемента ИЛИ, выходы третьего и четвертого элементов И соединены с входами четвертого элемента ИЛИ, выход которого является вторым информационным выходом Si, отличающийся тем, что в каждый разряд устройства введен второй вход управления 2ВУ выполнением ОЛС, запрещающий работу второго элемента И во всех разрядах СУ одновременно, при этом 2ВУ подключен к третьему входу второго элемента И, выход которого через первый элемент НЕ подключен к второму входу третьего элемента И, что позволяет информационным сигналам Ai и Bi по цепи первого и третьего элементов ИЛИ, третьего элемента И и четвертого элемента ИЛИ поступить на второй информационный выход Si, что является результатом выполнения ОЛС.

3. Способ выполнения операции логического умножения ОЛУ на основе оборудования сумматора комбинационного типа СУ, содержащего в каждом разряде первый - четвертый элементы И, первый - четвертый элементы ИЛИ, первый элемент НЕ, первый - третий информационные входы ИВ, на которые поступают сигналы с выходов триггеров i-го разряда Ai, Bi и сигнал переноса из i-1-го разряда Pi-1 соответственно, при этом информационные входы Ai и Bi соединены с входами первых элементов И, ИЛИ, третий информационный вход Pi-1 соединен с входами третьего и второго элементов ИЛИ и с входом четвертого элемента И, выходы первого и второго элементов ИЛИ соединены с первым и вторым входами второго элемента И, выход второго элемента И через первый элемент НЕ соединен с входом третьего элемента И, выход третьего элемента И соединен с входом четвертого элемента ИЛИ, выход которого является вторым информационным выходом устройства Si, отличающийся тем, что в каждый разряд устройства введен первый вход управления 1ВУ выработкой имитационного потенциала переноса ИПП, который подключен через второй элемент ИЛИ к первому входу второго элемента И, введен третий вход управления 3ВУ выполнением ОЛУ, подключенный к третьему входу первого элемента ИЛИ, операцию выполняют за один временной такт t1, по которому на первый и второй информационные входы подают потенциалы Ai и Bi, при Ai=Bi=1 с выхода первого элемента И на второй вход четвертого элемента И поступает ВП, одновременно на 1ВУ и 3ВУ также подают ВП, за счет чего на выходе второго элемента И во всех разрядах формируют имитационный потенциал переноса ИПП, который поступит на входы четвертых элементов И, с выхода которых ВП через четвертый элемент ИЛИ поступает на второй информационный выход Si, на этом выполнение ОЛУ завершают.

4. Устройство реализации вычислительных операции сложения ОС, операций логического сложения ОЛС и операций логического умножения ОЛУ, выполненное на основе оборудования сумматора комбинационного типа СУ, содержащее в каждом двоичном разряде первый - четвертый элементы И, первый - четвертый элементы ИЛИ, первый элемент НЕ, первый - третий информационные входы ИВ, на которые поступают сигналы с выходов триггеров Ai, Bi и сигналы переноса из i-1-го разряда Pi-1 соответственно, каждый разряд содержит информационные выходы Pi и Si, при этом входы Ai и Bi соединены с входами первого и второго элементов И, ИЛИ, вход Pi-1 соединен с входами третьего и второго элементов ИЛИ и с входом четвертого элемента И, выход первого элемента И соединен с первым входом второго элемента ИЛИ и вторым входом четвертого элемента И, выходы второго и первого элементов ИЛИ соединены с входами второго элемента И, выход первого элемента ИЛИ также соединен с входом третьего элемента ИЛИ, выход второго элемента И является первым информационным выходом переноса, выработанном в i-м разряде Pi, выход второго элемента И через первый элемент НЕ соединен со вторым входом третьего элемента И, первый вход этого элемента И связан с выходом третьего элемента ИЛИ, выходы третьего и четвертого элементов И соединены с входами четвертого элемента ИЛИ, выход которого является вторым информационным выходом Si, отличающееся тем, что в каждый разряд устройства введен первый вход управления 1ВУ формированием имитационного потенциала переноса ИПП, предназначенного для исключения временных задержек сигналов переносов, выработанных в младших разрядах, упомянутый 1ВУ в каждом разряде подключают к третьему входу второго элемента ИЛИ, введен второй 2ВУ выполнением ОЛС, запрещающий передачу потенциала переноса в старший разряд, подключенный к третьему входу второго элемента И, первый и второй входы которого соединены с выходами второго и первого элементов ИЛИ, выход второго элемента И через первый элемент НЕ соединен со вторым входом третьего элемента И, введен третий вход управления 3ВУ выполнением ОЛУ, упомянутый 3ВУ подключен к третьему входу первого элемента ИЛИ.

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2013 |

|

RU2537046C2 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2505850C2 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| US5944772 A, 31.08.1999 | |||

| US 4920509 A, 24.04.1990. | |||

Авторы

Даты

2018-01-16—Публикация

2016-12-02—Подача