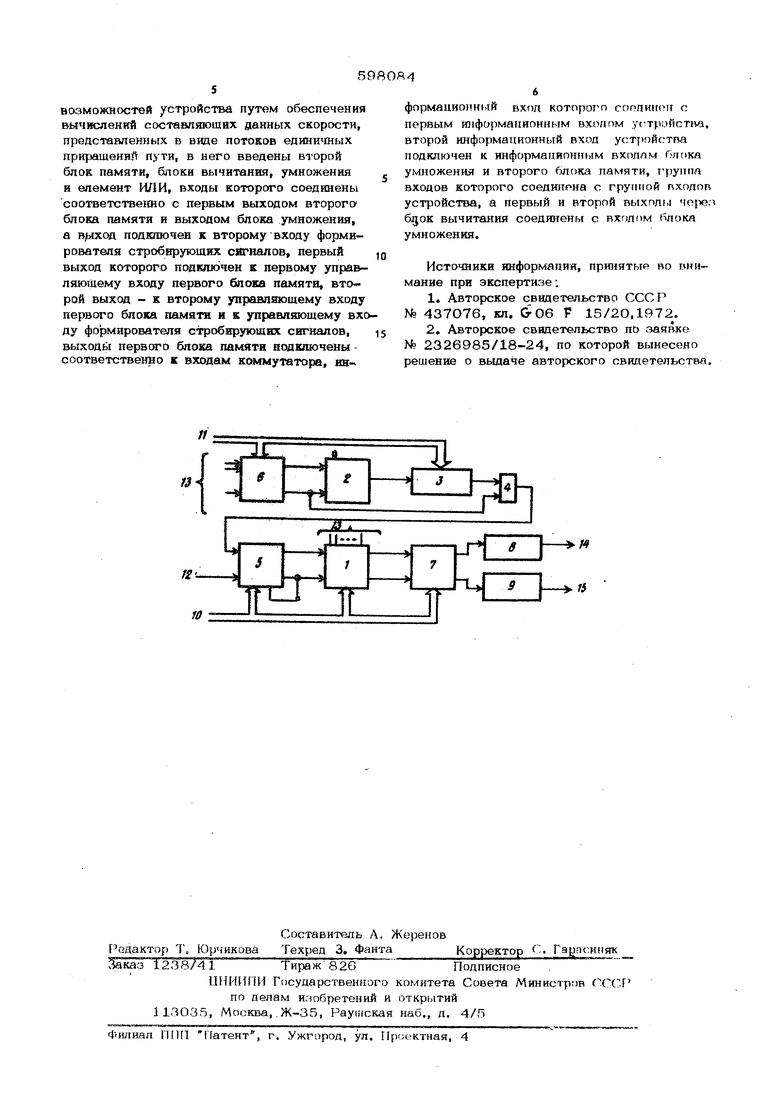

входом устройства, информационный вход подключен к первому информационному входу устройства, коммутатор, выходы которого через соответствующие делители частоты подключены к выходам устройства 2 Недсютатком йтсго устройства является ограйичеш ые функциональные возможности, так как оно предназначено для преобразования подярных координат вектора в прямоугольные. Целью изобретения является расширение фуггкционельньк возможностей устройства путем обеспечения вычислений составляюших данных скорости, представленных в виде потоков едш1ичных приращений пути, Это достигается тем, что в устройство введены второй блок памяти, блоки вычаTBHEHj утлноженйя и элемент ИЛИ, входы которого соедниены соответственно с первым вь ходом второго блока памяти и выходом блока умножеиш, а выход подключен к второму формирователя стробирующах сигналов. Первый выход последнего 1тодю1ючен к первому управляющему входу первого блока памяти, второй выход к вт рому управляющему входу первого блока памяти и к управляющему входу формврователя сТробирующих сигналов. Выходы первого блока памнйг подключены соответственн к входам коммутатрра, информационный вход которого соединен с первым информациовдьш входом у(ойстэа. Второй информационный вход устройства подключен к Ш1форма1х{й)нкым входам блока умножения н второго бпош памяти, группа входов кото рого соединена с группой входов устройства а первый и второй выходы чё зблок вычитаний соединены с входом блока умножен Схема устройства предстйвлена иа черте же. Устройстей содержит блок 1 памяти, бло 2 вычиШНйн, блок 3 у,нрженйя, элемент ИЛИ 4, формйрОБа епь S втррбирующйх сигналов, блок 6 памяти, коммутатор 7, делители 8,9 частоты н ietMeeT входы 10,11 н 12 группы входов 18 и выходы 14 и 15. Реализация множительно-функциональных {Зависимостей для опредекення горизйтапьньш составляющих 1эсущесталяется формирования чкспскнмпульсных кодов,j подававмых на соответствующие делители частоты 8,9 с приходом шждого импульса входной частс гы на вход 12.

Управление выбором частот з блока 1 памяти осуществляется с помощью реверсив кого счетчшса (на чертеже не показан), вхад$пцего в аостав Блока, на суммирующий и вычитающий входы которого поступают импульсы с формирователя 5. Эти импульсы изменяют состояние так, что на выходах

ный вход подключен к первому информационному входу устройства, формирователь стробирующих с1П Налов, первый вход которого соедшшн с входом устройства, информационный вход подключен; к первому информ.втюн.абму входу устройства, коммутатор, выходы которого через соответствующие делители частоты подключены к выходам устройства, отличающееся Т(м, что, с цельйэ расшир€ння функциональных блока в течение одного интервала времени одновременно формируется определенный набор частот, а в течение другого интервала времени - другой набор частот. Такой способ получения число-импульсных кодов позволяет в два раза расширить диапазон изменения входной частоты по сравнению с известным устройством. В .основу формирования частоты, посту- павйяёй с выхода элемента ИЛИ 4 на вход формирователя 5, положена кусочно-линейная аппроксимация функции секорса по разностной формуле полинома Лагранжа. Для атой цели на вход блока б па .яти с вх,ода 11 устройства подаются старш иэ разряды входного кода, управляющие подключением частот к входам блока 2 вычитания. Разностая частота уьшожается на код с помощью блока 3. Операция сложения осуществляется на элементе ИЛИ 4, так как частоты не имеют совпадающих импульсов, Коммутатор 7 осуществляет распределение импульсных потоков с выхода блока 1 памяти в соответствующие делители частоты в зависимости от кода номера квадранта. К достоинству устройства следует отнести простоту его стыковки с датчиками и исполнительными механизмами, высокую точность формирования выходных величин в ввде частотно-импульсных сигналов, позволяющих обеспечить длительное и точное интегргфованке. Кроме тото, оно имеет лучшие показатели по сравнению с известными устройствами, а -именно; более широкие функциональные возможности - определения горизонтальных составляющих не только шшского, но и пространственного вектора скорости, повышенное в два раза быстродейе-Пзие, сра&нктельно Небольшие аппаратурные , затраты,. Формула изобретения Устройство для определения горизонталь аых состбвяяющия пространственного вектора скорости содержащее первый блок паMHTHg группа входов которого соединена с группой входов устройства а информационвозможностей устройства путем обеспечения вычж лений ссхзтавляющнх данных скорости, представленных в виде потоков единичных приращений пути, в него введены второй блок памяти, блоки вычитания, умножения н елемент ИЛИ, входы которого соединены соответстве1шо с первым выходом второго блока памяти и выходом блока умножения, а подютючен к второму входу формирователя стробирующйх сягналов, первый выход которого поакшочен к первому управляющему входу первого блока памяти, второй выход - к второму управлтощему входу первого блока памятн и к управл51ющему входу формирователя стробирующих сигналов, выходы первого блока памятн подключены соответствеотЕО к входам коммутатора, янформациоин111Й вход которого соодиион с первым т форма1шонным входом ус-труйспуз, второй информаиионн,1Й вход подключен к информационным вхоллм блока умножения и второго блока памяти, группа входов которого соединена с группой пхолоп устройства, а первый и второй выхппр,г чо1ю.6ijoK вычитания соединены с входом tSnoKa умножения.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельс-гео ССС Р № 437О76, кл. G-06 F 15/20,1972.

2.Авторское свидетельство пЬ заявке NO 2326985/18-24, по которой вынесено решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь полярных координат вектора в прямоугольные | 1976 |

|

SU596955A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Устройство для отображения информации | 1987 |

|

SU1476523A1 |

| Устройство для контроля аналоговых объектов | 1989 |

|

SU1718189A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| Устройство для измерения части интерференционной полосы | 1987 |

|

SU1467395A1 |

| Устройство для отображения информации | 1987 |

|

SU1513439A1 |

| Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации | 1989 |

|

SU1608730A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1984 |

|

SU1168966A1 |

Авторы

Даты

1978-03-15—Публикация

1976-07-12—Подача