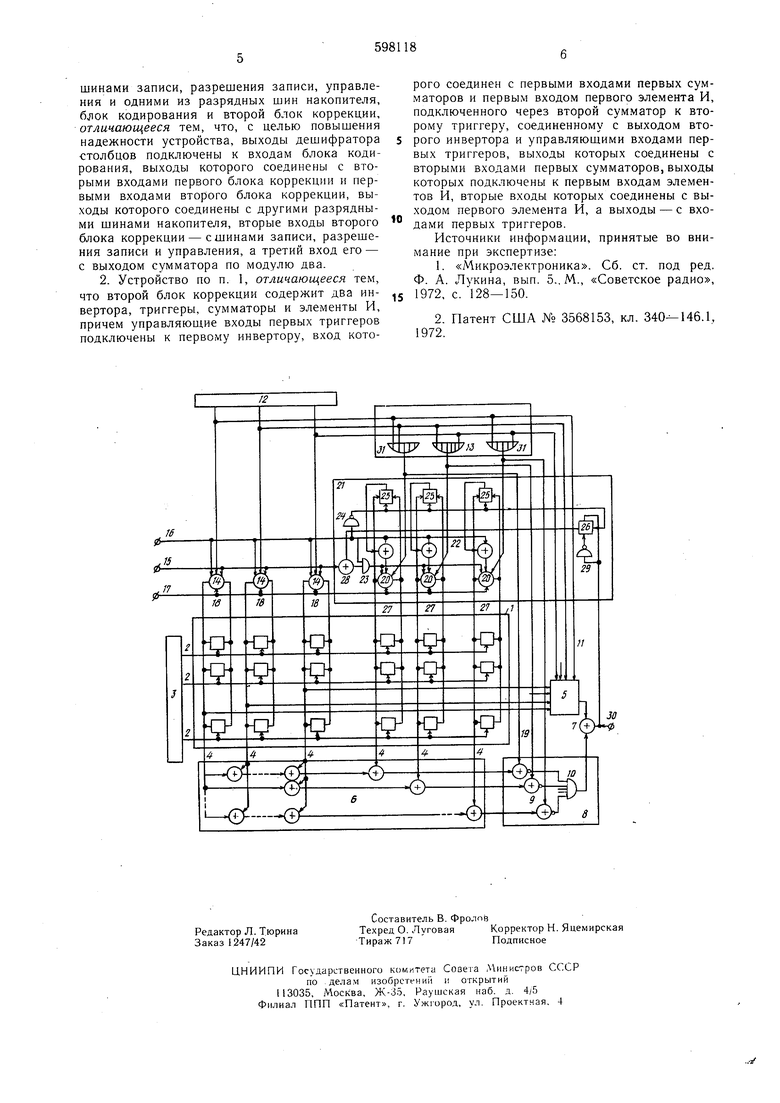

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Известно запоминающее устройство с матричной организацией, содержащее накопитель, дешифратор строк и столбцов, блок считывания, элемент И, щины записи, разрещения записи и управления 1. Это устройство обеспечивает обращение к любому одному элементу памяти накопителя. Однако его работоспособность нарущается при отказах и сбоях элементов памяти накопителя. Наиболее близким к изобретению является запоминающее устройство, содержащее накопитель, числовые шины которого соединены с выходами дешифратора строк, выходные щины - с входами блоков считывания и контроля, выходы которых подключены соответственно к первому входу сумматора по модулю два и к nepKuiM входам первого блока коррекции, выхо i которого подключен к второму входу сум.матора по модулю два, дещифратор столбцов, выходы которого соединены с управляющими входами блока считывания и подключены к элементам И, связанным с шина.ми записи, разрешения записи, управления и одним из разрядных щин накопителя, блок кодирования и второй блок коррекции 2. Это устройство характеризуется надежностью из-за сложности контроля при обращенщ к одному элементу памяти накопителя. Целью изобретения является повыщение надежности устройства. В описываемом устройстве это достигается тем, что в нем выходы дешифратора столбцов подключены к входам блока кодирования, выходы которого соединены с вторыми входами первого блока, коррекции и первыми входами второго блока коррекции, выходы которого соединены с другими разрядными шинами накопителя, вторые входы второго блока коррекции -с шинами записи, разрешения записи и управления, третий вход его - с выходом сумматора по модулю два. Кроме того, второй блок коррекции содержит два инвертора, триггеры, сумматоры и элементы И, причем управляющие входы первых триггеров подКоТючены к первому инвертору, вход которого соединен с первыми входами первых сумматоров и первым входом первого элемента И, подключенного через второй сумматор к второму триггеру, соединенному с выходом второго инвертора и управляющими входами первых триггеров, выходы которых соединены с вторыми входами первых сумматоров, выходы которых подключены к первым входам вторых элементов И, вторые входы которых соедийены с выходом первого элемента И, а выходы- с входами первых триггеров. На чертеже приведена схема описываемого устройства. Оно содержит накопитель 1, соедкпенный числовыми шинами 2 с выходами дешифратора 3 строк. Выходные шины 4 накопителя соединены с входами блоков считывания 5 и контроля 6. Выходы блоков считывания 5 и контроля 6 подключены, соответственно, к первому входу сумматора 7 по модулю два и первого блока 8 коррекции. Инверсные выходы сумматоров 9 по модулю два соединены с входами элемента И 10. Выход элемента И 10 является выходом первого блока коррекции и соединен -с вторым входом сумматора 7 по модулю два. Управляюшие входы 11 блока 5 считывания соединены с выходами дешифратора 12 столбцов и входами блока 13 кодирования и подключены через элементы И 14 к шинам записи 15, разрешения записи 16, управления 17 и к одним из разрядных шин 18 накопителя. Вторые входы 19 сумматоров по модулю два первого блока 8 коррекции соединены с выходами блока 13 кодирования и вторыми входами элементов И 20 второго блока 21 коррекции. Первые входы элементов И 20 соединены с выходами сумматоров 22 по модулю два. Первые входы сумматоров 22 по )Модулю два соединены непосредственно с HIHной разрешения записи и первьМ входом элемента И 23 и через первый инвертор 24 с управляющими входами триггеров 25 и триггера 26. Вторые входы сумматоров 22 по модулю соединены с выходами триггеров 25, сигнальные входы которых подключены к другим разрядным шинам 27 накопителя и выходам элементов И, выходы которых являются выходами второго блока коррекции. Второй вход элемента И 23 соединен с выходом су.мматора 28 по модулю. Первый вход сумматора 28 по модулю два соединен с шиной записи, а второй вход - с выходом триггера 26. Сигнальные входы триггера 26 соединены непосредственно и через второй инвертор 29 с выходом 30 сумматора 7 по модулю два, выход которого яв.чяется выходом устройства; кроме того, устройство содержит элементы ИЛИ 31. При записи информации на соответствующие шины 15 и 17 устройства подаются сигналы записи и .управления. При этом в соответствиии с кодом адреса, подаваемым на входы дешифраторов 3 и 12, происходит, возбуждение одной из числовых шин 2 накопителя 1 и одной из выходных шин дешифратора 12. Возбужденная числ-овая шина 2 отпирает разрядные шины 18 и 27 элементов памяти опрашиваемой строки накопителя 1 и подключает выходные шины 4 к сумматорам по модулю два блока 6 контроля, сигналы с вы.ходов которого поступают на первые входы сумматоров 9 по модулю два блока 8 коррек ции. Блок 6 вычисляет контрольные соотношения кода Хемминга. Результатом вычисления является проверочный вектор (синдром), который равен-нулю при отсутствии ошибок в опрашиваемой строке накопителя 1 и не равен нулю - в противном случае. Наряду с этим. сигнал с одной из возбужденных шин дешифратора 12 формирует на элементах ИЛИ блока 13 сигналы, соответствующие синдрому опрашиваемого столбца накопителя 1, которые поступают на вторые входы сумматоров 9 по модулю два первого блока 8. Если информация, хранимая в опрашиваемом елементе памяти (на чертеже не показан) накопителя 1 искажена, т.е. выходные сигналы блока контроля не равны нулю и совпадают с выходными сигналами блока 13 кодирования, то на выходе элемента И 10 первого блока 8 будет единичный сигнал, который инвертирует на правильный в сумматоре 7 сигнал о состоянии опрашиваемого элемента памяти, снимаемый с выхода блока 5. Исправленный сигнал с выхода сумматора 7 записывается для хранения в триггер 26. Кроме того, сигналы о состояниях элементов памяти контрольных столбцов опрашиваемой строки накопителя 1 поступают по разрядным шинам 27 и записываются для хранения в триггеры 25. Выходной сигнал вспомогательного триггера 26 поступает на сумматор 28, где сравнивается с сигналом записи по шине 15. На выходе сумматора 28 будет единичный сигнал, если опрашиваемый для записи элемент памяти накопителя 1 должен изменить свое состояние, и нулевой сигнал - в нротивном случае. При изменении состояния опращиваемого элемента памяти нарущаются условия, задаваемые контрольным соотношениями кода Хемминга. Поэтому для правильно.го их выполнения требуется изменя.ть состояние тех элементов памяти контрольнь1х столбцов накопителя 1, которые зависят от состояния опращиваемого элемента памяти накопителя. На выходе блока 13 кодирования формируются эти сигналы, которые поступают на первые входы элементов И 20. На вторые входы элементов И 20 при поступлении сигнала разрешения записи по шине 16 и изменении состояния опрашиваемого элемента памяти накопителя 1 поступает единичный сигнал с выхода элемента И 23, который отпирает элементы И 20. При этом вместе с записью новой информации в опрашиваемый элемент памяти накопителя происходит запись инвертированной на сумматорах 22 информации, хранимой в триггерах 25 второго блока 21 коррекции. Таким образом, повышается общая надежность хранения и воспроизведения информации. Формула изобретения 1. Запоминающее устройство, содержащее накопитель, числовые щины которого соединены с выходами дешифратора строк, выходные шины - с выходами блоков считывания и контроля, выходы которых подключены соответственно к первому входу сумматора по модулю два и к первым входам первого блока коррекции, выход которого подключен к второму входу сумматора по модулю два, дешифратор столбцов, выходы которого соединены с управляющими входами блока считывания и подключены к элементам И, связанным с

шинами записи, разрешения записи, управления и одними из разрядных шин накопителя, блок кодирования и второй блок коррекции, отличающееся тем, что, с целью повышения надежности устройства, выходы дешифратора столбцов подключены к входам блока кодирования, выходы которого соединены с вторыми входами первого блока коррекции и первыми входами второго блока коррекции, выходы которого соединены с другими разрядными шинами накопителя, вторые входы второго блока коррекции - с шинами записи, разрешения записи и управления, а третий вход его - с выходом сумматора по модулю два.

2. Устройство по п. 1, отличающееся тем, что второй блок коррекции содержит два инвертора, триггеры, сумматоры и элементы И, причем управляющие входы первых триггеров подключены к первому инвертору, вход которого соединен с первыми входами первых сумматоров и первым входом первого элемента И, подключенного через второй сумматор к второму триггеру, соединенному с выходом второго инвертора и управляюшими входами первых триггеров, выходы которых соединены с вторыми входами первых сумматоров, выходы которых подключены к первым входам элементов И, вторые входы которых соединены с выходом первого элемента И, а выходы - с входами первых триггеров.

Источники информации, принятые во внимание при экспертизе:

1.«Микроэлектроника. Сб. ст. под ред. Ф. А. Лукина, вып. 5.. М., «Советское радио 1972, с. 128-150.

2.Патент США № 3568153, кл. .1, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1975 |

|

SU602995A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Запоминающее устройство | 1981 |

|

SU1010654A1 |

| Запоминающее устройство матрич-НОгО ТипА C САМОКОНТРОлЕМ | 1979 |

|

SU841063A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU955209A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

Авторы

Даты

1978-03-15—Публикация

1975-04-09—Подача