112 80702

Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано при построении преобразователей в двоично-десятичный код, двоичный код, в двоично-десятично-шестидесятиричный, для преобразования двоичных ко- дор с масштабированием.

Цель изобретения - расширение

2

двоично-десятичный производится по одному и тому же алгоритму. Различие только в содержании программы, жестко заложенной в формирователе 4 эквивалентов. При преобразовании кодов, следующих старшими разрядами вперед, программные.линейки с меньшим адресом содержат эквиваленты старших разрядов, при преобразовании

класса решаемых задач за счет обеспе- 0 кодов, поступающих младшими разрядачения возможности преобразования двоично-шестидесятиричного кода в двоично-десятичный и двоично-десятично-шестидесятиричный коды, поступаю- шле как младшими, так и старшими разрядами вперед.

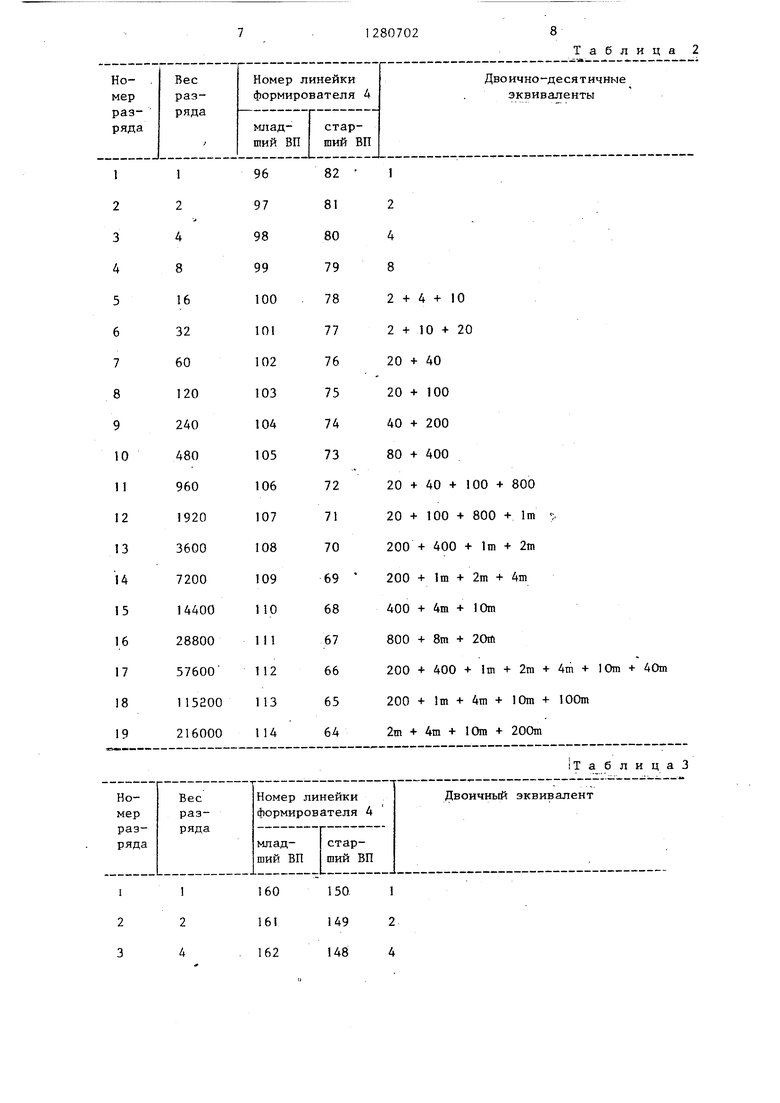

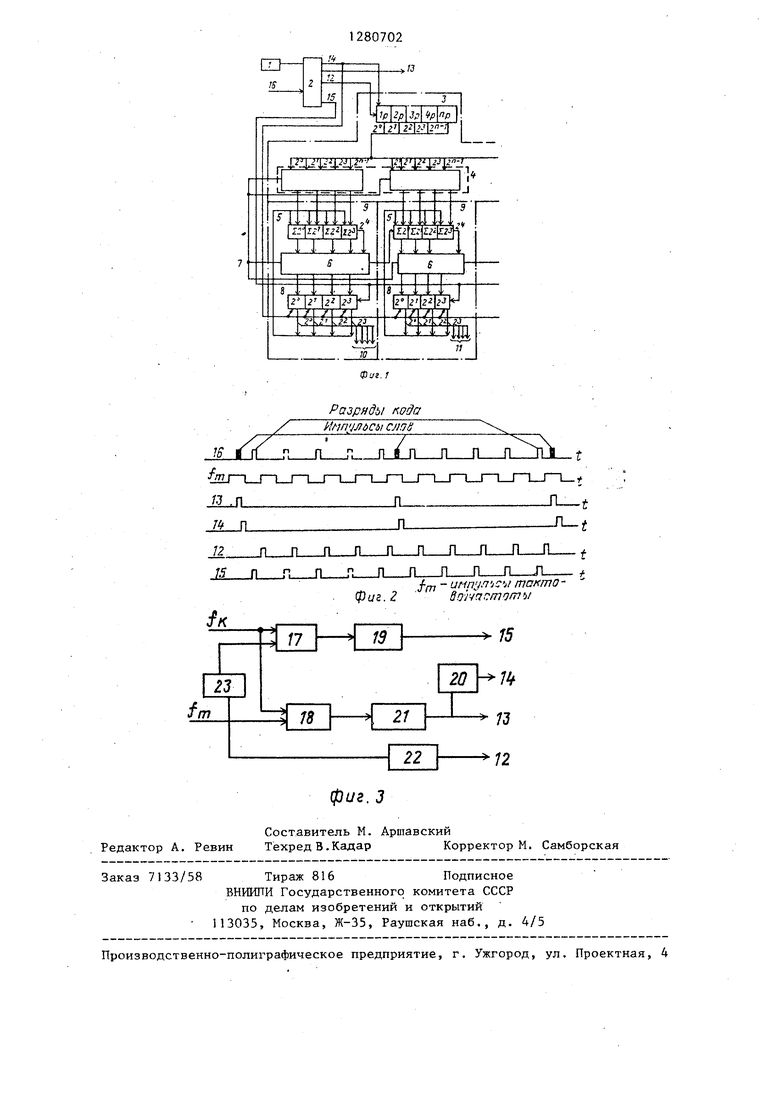

На фиг.1 изображена структурная схема предлагаемого преобразователя; на фиг.2 - временная диаграмма рабо-, ты распределителя импульсов; на фиг.3 - структурная схема распреде- лителя импульсов.

Преобразователь содержит генератор 1 импульсов, распределитель 2 импуль-сов , счетчик 3, формироват.ель 4 эквивалентов, тетрады комбинационного сумматора 5, группу блоков 6 коррекции, вход 7- выбора закона преобразования, тетрады регистра 8, Блоки 5, 6 и 8 в совокупности образуют накопительный сумматор 9, выходы кото- рого являются информационными выходами 10 и 11 преобразователя. Распределитель 2 импульсов имеет выход 12 синхросигналов, выход 13 сигналов .сопровождения, выход 14 сигнала сброса и кодовый выход 15. На вход распределителя импульсов поступает кодовая посылка с информационного входа 16 преобразователя.

Распределитель 2 импульсов обеспечивает выделение из входного сигнала импульсов кода (выход 15), импульсов слов и формирование импульсов сопровождения преобразованного кода (выход 13), формирование импульсов фа- зировки (выход 14), тактовых синхроимпульсов (выход 12). Распределитель 2 импульсов состоит из двух элементов И 17 и 18, четырех одновибрато- ров 19 - 22 и элемента НЕ 23 (фиг.З) Счетчик 3 формирует двоичный код номера разряда преобразуемого кода.

Преобразование кодов, поступающих младшими или старшими разрядами вперед, преобразование двоично-десятичного кода в двоичный, преобразование двоично-шестидесятиричного кода в

2

двоично-десятичный производится по одному и тому же алгоритму. Различие только в содержании программы, жестко заложенной в формирователе 4 эквивалентов. При преобразовании кодов, следующих старшими разрядами вперед, программные.линейки с меньшим адресом содержат эквиваленты старших разрядов, при преобразовании

5

0

5

0

ми вперед, программные линейки с меньшим адресом содержат эквиваленты младших разрядов. В предлагаемом варианте реализации количество программ, заложенных в устройстве, равно восьми.

Восемь программ, заложенных в формирователе 4, позволяют производить преобразование следующих кодов, поступающих младшими или старшими разрядами вперёд: двоичного кода в двоично-десятичный, двоичного кода в двоично-десятичный код секунд, минут и градусов, двоично-шестидесятиричного в двоично-десятичный код и двоично-десятичного кода в двоичный.

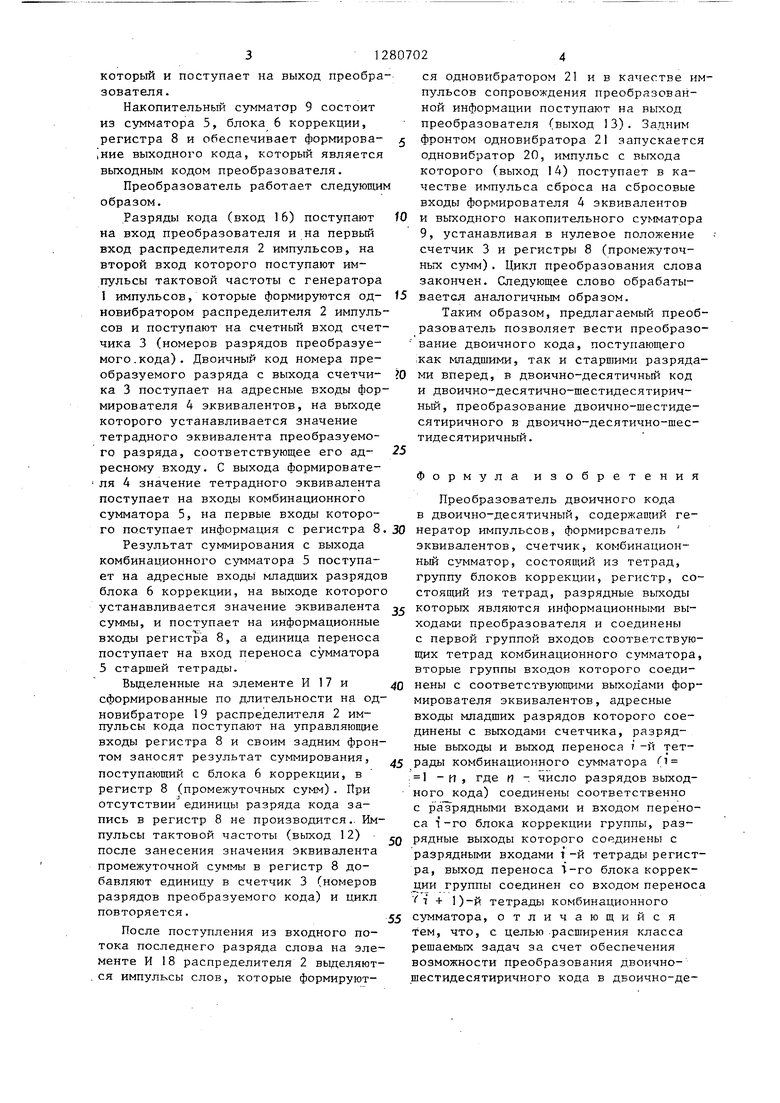

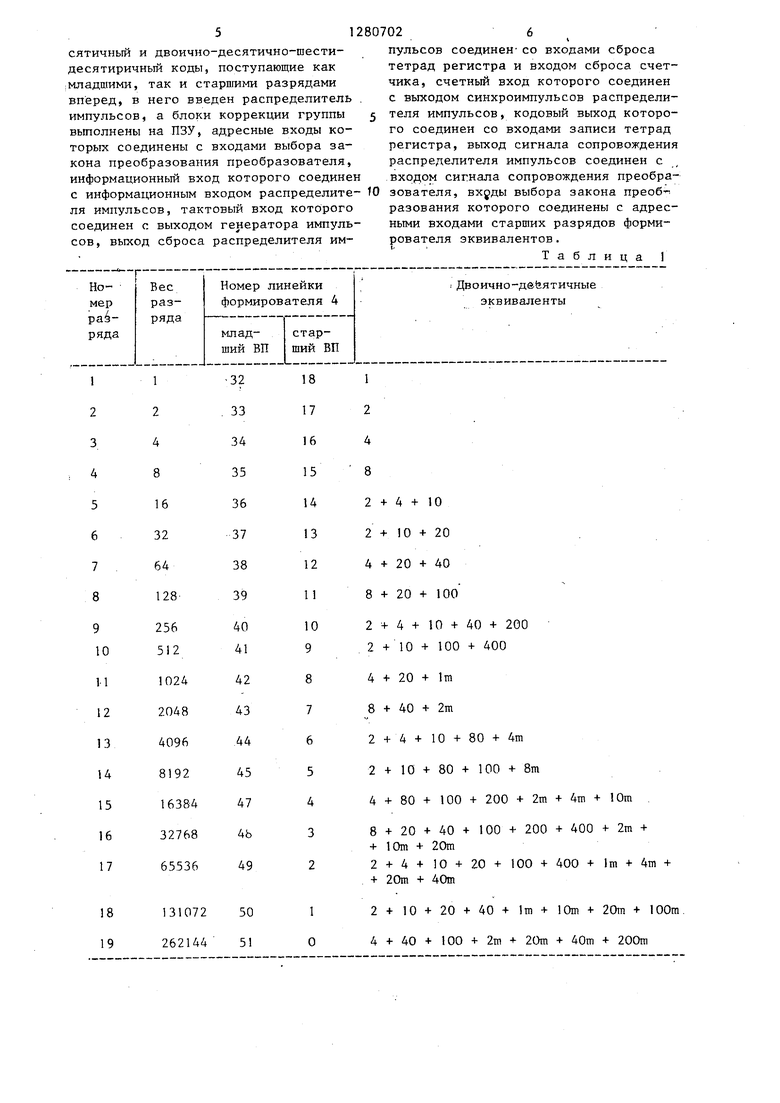

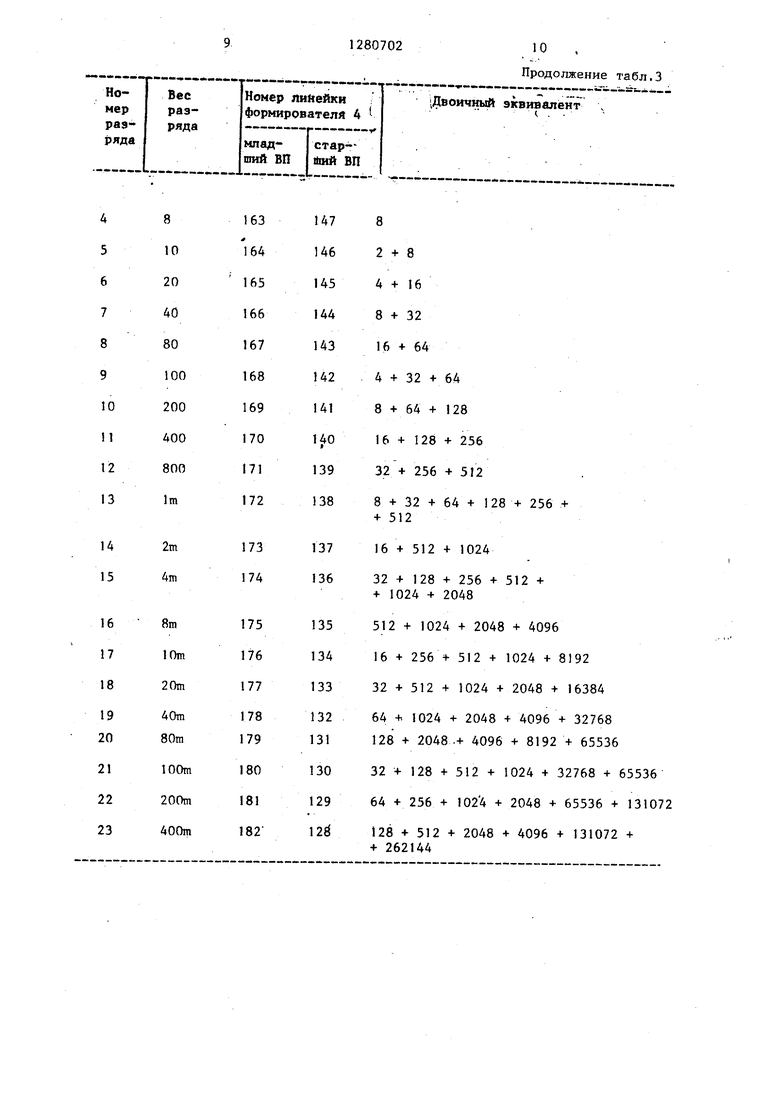

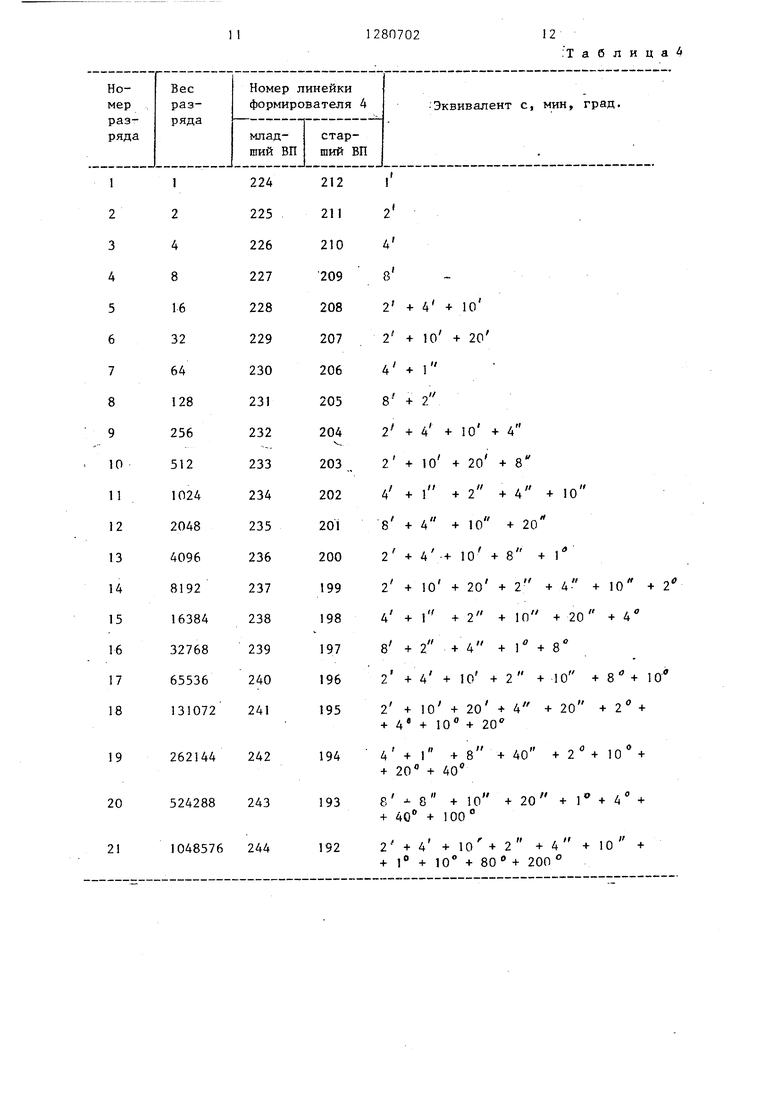

Значения соответствующих эквивалентов приведены в табл.1-4.

Выбор закона преобразования осуществляется по коду номера программы, поступающему на вход 7 преобразователя от внешнего абонента. Код но- мера программы со входа преобразователя поступает на адресные входы трех старших разрядов формирователя 4 эквивалентов и блока 6 коррекции. Количество формирователей 4 эквивалентов равно количеству тетрад преобразования.

Комбинационный сумматор 5 представляет собой двоичный сумматор и предназначен для суммирования потет- радно эквивалентов текущего разряда с суммарным значением ранее поступив- ших разрядов.

Блок 6 коррекции хранит значения эквивалентов тетрадных кодовых сумм. Выбор значения эквивалента производится по коду числа, поступающего на Q его адресные входы с выхода сумматора 5. Конструктивно блок 6 коррекции может быть реализован на постоянном

запоминающем устройстве.

f

. Регистр 8 предназначен для хранения суммарного значения тетрадных эквивалентов разрядов преобразуемого кода, т.е. на их выходах формируется результат конечного преобразования.

5

0

31

который и поступает на выход преобразователя.

Накопительный сумматор 9 состоит из сумматора 5, блока 6 коррекции, регистра 8 и обеспечивает формирова- ние выходного кода, который является выходным кодом преобразователя.

Преобразователь работает следующи образом.

Разряды кода (вход 6) поступают на вход преобразователя и на первый вход распределителя 2 импульсов, на второй вход которого поступают импульсы тактовой частоты с генератора 1 импульсов, которые формируются од- новибратором распределителя 2 импульсов и поступают на счетный вход счетчика 3 (номеров разрядов преобразуемого, кода). Двоичный код номера пре

образуемого разряда с выхода счетчи- 0 ми вперед, в двоично-десятичный код

-

ка 3 поступает на адресные входы формирователя 4 эквивалентов, на выходе которого устанавливается значение тетрадного эквивалента преобразуемого разряда, соответствующее его ад ресному входу. С выхода формирователя 4 значение тетрадного эквивалента поступает на входы комбинационного сумматора 5, на первые входы которого поступает информация с регистра 8

Результат суммирования с выхода комбинационного сумматора 5 поступает на адресные входы младших разрядо блока 6 коррекции, на выходе которог устанавливается значение эквивалента суммы, и поступает на информационные входы регистра 8, а единица переноса поступает на вход переноса сумматора 5 старшей тетрады.

Вьщеленные на элементе И 17 и сформированные по длительности на одновибраторе 19 распределителя 2 импульсы кода поступают на управляющие

входы регистра 8 и своим задним фронтом заносят результат суммирования, поступающий с блока 6 коррекции, в регистр 8 (промежуточных сумм). При отсутствии единицы разряда кода запись в регистр 8 не производится.. Р1м- пульсы тактовой частоты (выход 12) после занесения значения эквивалента промежуточной суммы в регистр 8 добавляют единицу в счетчик 3 (номеров разрядов преобразуемого кода) и цикл повторяется.

После поступления из входного потока последнего разряда слова на элементе И 18 распределителя 2 вьщеляют- ся импульсы слов, которые формируются одноБибратором 21 и в качестве импульсов сопровождения преобразованной информации поступают на выход преобразователя (выход 13). Задним фронтом одновибратора 21 запускается одновибратор 20, импульс с выхода которого (выход 14) поступает в качестве импульса сброса на сбросовые входы формирователя 4 эквивалентов и выходного накопительного сумматора 9, устанавливая в нулевое положение счетчик 3 и регистры 8 (промежуточных сумм). Цикл преобразования слова закончен. Следующее слово обрабатывается аналогичным образом.

Таким образом, предлагаемый преобразователь позволяет вести преобразование двоичного кода, поступающего как младшими, так и старшими разряда25

и двоично-десятично-щестидесятирич- ный, преобразование двоично-щестиде- сятиричного в двоично-десятично-щес- тидесятиричный.

Формула изобретения

Преобразователь двоичного кода в двоично-десятичный, содержащий генератор импульсов, формирователь эквивалентов, счетчик, комбинационный сумматор, состоящий из тетрад, группу блоков коррекции, регистр, состоящий из тетрад, разрядные выходы

которых являются информационными выходами преобразователя и соединены с первой группой входов соответствующих тетрад комбинационного сумматора, вторые группы входов которого соединены с соответствующими выходами формирователя эквивалентов, адресные входы младших разрядов которого соединены с выходами счетчика, разрядные выходы и выход переноса т -и тетрады комбинационного сумматора 1 - И , где п - число разрядов выходного кода) соединены соответственно с ра зрядными входами и входом переноса 1-го блока коррекции группы, раз- рядные выходы которого соединены с

разрядными входами т-и тетрады регистра, выход переноса 1-го блока коррекции группы соединен со входом переноса /7 + 1)-й тетрады комбинационного сумматора, отличающийся тем, что, с целью расширения класса решаемых задач за счет обеспечения возможности преобразования двоично- шестидесятиричного кода в двоично-де

t

сятичный и двоично-десятично-шеети- пульсов соединен- со входами сброса десятиричный коды, поступающие как тетрад регистра и входом сброса счет- младшими, так и старшими разрядами чика, счетный вход которого соединен вперед, в него введен распределитель . с выходом синхроимпульсов распредели- импульсов, а блоки коррекции группы 5 теля импульсов, кодовый выход которого соединен со входами записи тетрад регистра, выход сигнала сопровождения распределителя импульсов соединен с информационный вход которого соединен входом сигнала сопровождения преобра- с информационным входом распределите- tO зователя, вхрды выбора закона преоб- ля импульсов, тактовый вход которого разования которого соединены с адрес- соединен с выходом генератора импуль- ными входами старших разрядов форми- сов, выход сброса распределителя им- рователя эквивалентов.

Таблица 1

выполнены на ПЗУ, адресные входы которых соединены с входами выбора закона преобразования преобразователя.

2+4+10 2+10+20 4+20+40 8+20+100

2+4+10+40+200 2 +10 + 100 + 400

4 + 20 + 1тп + 40 + 2т 2 +4 +10 +80+ 4т 2 + 10 + ВО + 100 + 8т 4 + 80 + 100 + 200 + 2т

8 + 20 + 40 + 100 + 200 + 10т + 20т

2 + 4 + 10 + 20 + 100 + + 20т + 40т

2+ 10+20+40+ т+ 4 + 40 + 100 + 2т + 20т

119682-1

2297812

3498804

4899798

516100 . 782+4+10

632101772 + 10 + 20

7601027620 + 40

81201037520 + 100

92401047440 + 200

104801057380 +400

119601067220 + 40 + 100 + 800

1219201077120+100+800 + 1m ;,

13360010870200 + 400 + 1m + 2tn

14720010969 200 + 1m + 2m + 4m

1514400no68400 + 4m + 10m

162880011167800 + 8m + 20iti

1757600 11266200 + 400 + 1m + 2m + 4m + 10m + 40m

1811520011365200 + 1m + 4m + 10m + 100m

19216000114642m + 4m + 10m + 200m

та6лицаЗ

1 2

4

160 161

162

1501

1492

1484

Таблица 2

Продолжение табл.3

19

20

21

262144

524288

242

243

1048576 244

+ 4 + 10 4- 20

194 4 + 1 + в + 40 10% + 20 + 40

193 8 - 8 + 10 +20 + 1 -ь 4 + + 40 + 100

192 2 + 4 + 10 + 2 + 4 + 10 + + 1 + 10 + 80 + 200 °

:Т а б л и ц а 4

Разрнды кода

п. р п п ПЛППППП.

Т5П

ЛfK

17

фиг. 3

Составитель М. Аршавский Редактор А. Ревин Техред В.Кадар Корректор М. Самборская

Заказ 7133/58 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

п пппп.

/д; - y/f/7 /.vii-w тактоФиг.2 .7УУ.7.7/; 7 7/Г71/

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный код и обратно | 1990 |

|

SU1755375A1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1988 |

|

SU1529457A2 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использовано при построении двоично-десятичных преобразователей. Целью изобретения является расширение класса решаемых задач за счет обеспечения возможности преобразования двоично-шестидесятиричного кода в двоично-десятичный и двоично-десятично-шестидесятиричный коды, поступающие как младшими, так и старшими разрядами вперед. Поставленная цель достигается за счет введения в сумматор преобразователя, осуществляющий последовательное накопление разрядных эквивалентов, блока коррекции, выполненного на П3, с возможностью изменения функции коррекции, и распределения импульсов, обеспечивающего реализацию всех режимов преобразования. 3 ил,, 4 табл. ю оо о ю

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-30—Публикация

1984-12-26—Подача