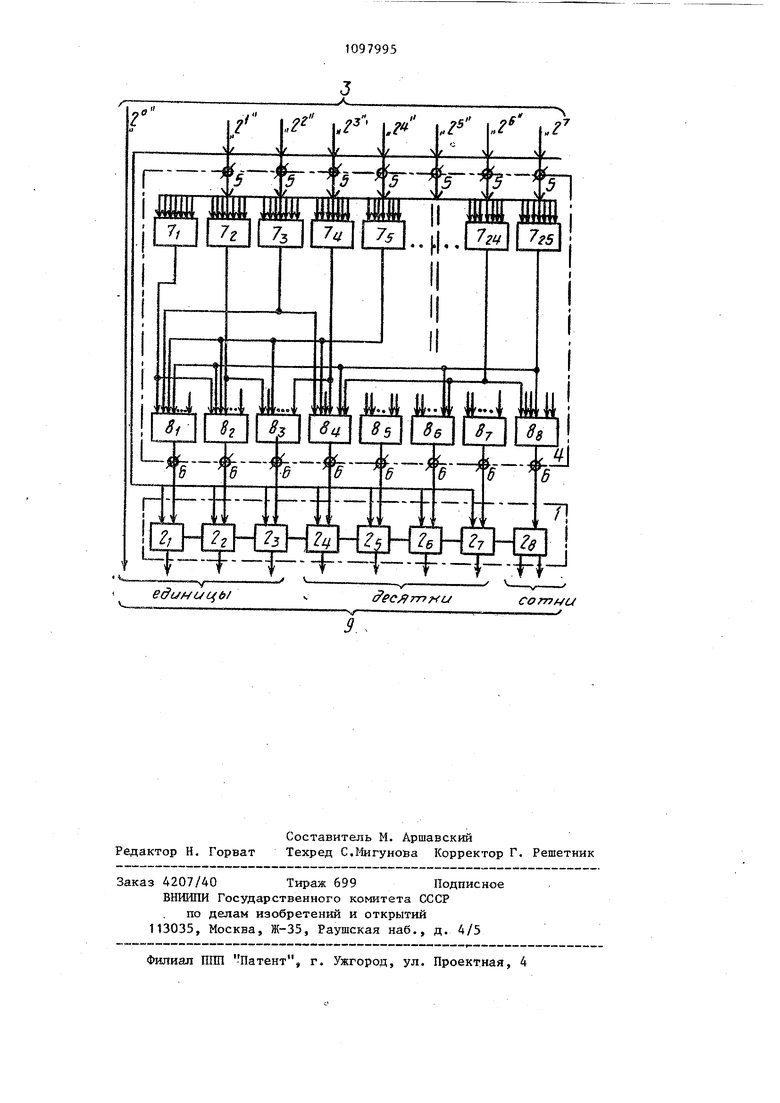

Изобретение относится к автомати ке и вычислительной технике и предназначено для преобразования кодов чисел в вычислительных системах. Известен преобразователь двоичного кода в десятичный, содержащий регистр двоичного числа, шифраторы двоичных эквивалентов, сумматоры, блоки вьйеления старшей единицы, группы элементов И, группы злементов ИЛИ, выходные регистры f1J. Недостатком этого преобразовател является низкое быстродействие, так как в нем о существляется покаскадно преобразование двоичного числа, при этом в каждом каскаде преобразовани для сотен, десятков и единиц исполь зуются операции суммирования, выделения старшей единицы и определения остатка. Такая каскадность преобразования приводит к значительной потере времени и довольно сильно снижает быстродействие преобразователя Наиболее близким к предлагаемому по технической сущности является преобразователь двоичного кода в дв ично-десятичньй код, содержащий дво ичньй сумматор, входы которого подключены ко входам преобразователя, выходы двоичного сумматора подключе ны ко входам блоков сокращения числа, выходы которых соединены с блоками вычитания и с двоично-десятичными сумматорами данного десятичног разряда, выходы блоков вычитания подключены ко входам двоично-десяти ного сумматора данного десятичного разряда и ко входам блока сокращения последующего старшего десятичного разряда, выходы двоично-десятичных сумматоров подключены к выхо дам преобразователя 2. В известном преобразователе двои ного кода в двоично-десятичный код используется комбинационная (статическая) схема. Для каждого десятичного разряда предусмотрен отдельный каскад преобразования. Каждый каскад преобразователя содержит блок сокращения числа, в котором производится сокращение суммы, получаемой в двоичном сумматоре до величины не больше, чем заданная (V) (в известном преобразователе V 29 блок вычитания из выходной величины блока сокращения числа, кратного 10, с тем, чтобы получить величину между О и 9. Недостаток этого преобразователя заключается в том, что в нем сначала осуществляется прием и суммирование весовых величин двоичного числа в двоичном сумматоре, затем последовательно для К80КЯОГО десятичного разряда производится сокращение суммы до величины не большей, чем заданная (V), вычитание из этой величины чисел, кратных 10, с последующим переносом сигналов переноса в последующий старший десятичньй разряд. Каскадность преобразования и наличие цепей переноса как между блоками внутри каскадов, так и между каскадами приводит к увеличению времени преобразования и к снижению быстродействия преобразователя. Целью изобретения является повышение быстродействия преобразователя. Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный код, содержащий двоичньш сумматор, первые входы которого соединены со входами преобразователя, кроме входа младшего разряда, который является выходом младшего разряда преобразователя, введен блок коррекции, содержащий группу дешифраторов десятков и группу элементов ИЛИ, причем входы дешифраторов десятков соединены со входами блока коррекции в соответствии с весами разрядов, выходы элементов ИЛИ группы соединены с выходами блока коррекции, выход i-ro ( 1 1 - 9) дешифратора десятков группы соединен с входами J -х ( i 1 - 5) элементов ИЛИ группы, для которых ( j-е разряды двоичного кода числа 6 i имеют единичные значения, выход К-го дешифратора десятков группы (К 10-99) соединен со входами С-х элементов ИЛИ группы ( С 1-10), для которых (Й -е) разряды двоичного кода числа бК + 96т имеют единичные значения, где tnзначение старшего десятичного разряда числа К, входы блока коррекции соединены со всеми входами преобразователя, кроме входа младшего разряда, а выходы блока коррекции соединены со вторыми входами двоичного сумматора, выходы которого являются выходами преобразователя. На чертеже представлен восъмираУрядньй преобразователь двоичного кода в двоично-десятичный, блок-схема. Преобразователь двоичного кода в двоично-десятичный код содержит двоичный суммйтор 1, содержащий последовательно соединенные одноразрядные комбинационные сумматоры , причем сумматоры 2, 2g - двухвходовые, а сумматоры трехвходовые, первые входы сумматоров 2-, подключены ко всем входам 3 npeq6разователя, кроме входа младшего разряда. , блок коррекции 4, входы 5 которого подключены ко всем входам 3 преобразователя, кроме вхо да мпадшего разряда 2°, а вькоды 6 блока коррекции 4 подключены ко вторьм входам сумматоров 2-, и к первому входу сумматора 2, Одноразрядные сумматоры 2 связаны цепями переноса. Перенос единицы из предыдущего в последующий старший разряд осуществляется следуюощм образом. С выхода переноса сумматора 2 на третий вход сумматора 22, с выхода переноса сумматора 22 на третий вход сумматора 2 и т.д. до 2, с выхода переноса сумматора. 2 . на второй вход сумматора 2g. Выходы сумматоров 2, 2, 2 вмес те с выходом младшего разряда 2° образуют выходы разрядов двоично-десятичного кода единиц преобразуемого числа, причем выход сумматора 2 является выходом разряда 2 , выход сумматора 2 является выходом разряда 2, выход сумматора 2 является выходом разряда 2. Выходы сумматоров 2., 2,, 2,, 2-J образуют выходы разрядов двоично-десятичного кода де сятков преобразуемого числа, причем выход cyMMaropia 2. является выходом разряда 2, выход сумматора 2j. является выходом разряда , выход сумматора 2 является выходом разряд 2, выход сумматора 2 является выходом разряда 2. Выход сумматора 2е и выход переноса сумматора 2g образуют выходы разрядов двоично-десятичного кода сотен преобразуемого числа, причем выход сумматора 2 является выходом разряда 2, выход переноса сумматора 2д является выходом разряда . Выходы единиц, десятков и сотен двоично-десятичного числа сумматора 1 вместе с выходом младшего разряда 2° являются одновременно и выходами преобразовател 9 двоичного кода в двоично-десятичный код. Блок коррекции 4 содержит группу 7 дешифраторов десятков - . ус , ВХОДЫ которых подключены ко входам 5 блока коррекции 4, выходы дешифраторов десятков 72с подключены ко входам элементов ИЛИ группы 8 в соответствии с единичными разрядами корректирующего числа, а именно: дешифратор второго десятка Z.i подключен ко входам элементов ИЛИ 8. и 8, дешифратор третьего десятка 7 подключен ко входам элементов ИЛИ 8 и 8j, дешифратор четвертого десятка 7j подключен ко входам -элементов ИЛИ 8 и 8., дешифратор пятого десятка 7 подключен ко входам элементов ИЛИ 8, и 8., дешифратор шестого десятка 7 подключен ко входам элементов ИЛИ 8, 82 8 и 8. и т.д. Дешифратор двадцать пятого десятка 724 подключен ко входам элементов ИЛИ 8, 8 и 8д, дешифратор двадцать шестого десятка 725 подключен ко входам элементов ИЖ 8.., 8-, 8, , вькоды элементов ИЛИ группы 8 подключены к выходам 6 блока коррекции 4. Работа преобразователя основана на принципе сложения двух чисел, выраженных в двоичном коде, в двоичном сумматоре. Проанализируем числа, вьфаженные в двоичном и двоично-десятичном кодах . Возьмем число 10. Ю 010102 ОООО.о Если теперь из этого числа, выраженного в двоично-десятичном коде, но записанного в вцде двоичного кода, вычесть то же самое число, выраженное в двоичном коде, то получим lOOOOz 01010, 001lOj Число 00110 2 6.,(, является дополнением к числу OlOIOj, чтобы, просуммировав их, получить число 10000-, являющееся двоичной записью двоичнодесятичного числа. Нетрудно убедиться, что любое число, большее О, но меньшее 100, выраженное в двоичном коде, можно дополнить до числа, выраженного в двоично-десятичном коде, если воспользоваться формулой А 6(Х-1), где А - корректирующее число-,

5

порядковый номер десятка

числа;

2 + 2 01

10., - константа. Возьмем, например, число 95. 01011111, 6(10-1) 54 0011011 Сложим два двоичных числа. 01011111г ООПОПОг ТооТоТоТг Или, если представить в виде дво ично-десятичного числа, то 01012-10 9-V Для чисел от 100 до 999 корректи рующее число рассчитывается по формулеА 6(Х-1) + 96(У-1), где У - порядковый номер сотни чис ла; 2 011000002 - кон станта. Для чисел от 1000 до 9999 коррек тирующее число рассчитывается по формуле А 6(Х-1) + 9б(У-1) + 1536(Z-1) где Z - порядковый номер тысячи чис ла; 7 10 011000000000 153.6,0 10константа. Например, возьмем максимальное число, которое может быть представлено в восьмиразрядном двоичном коде. Оно равно: 111111112 Для этого числа корректирующим числом будет А 6 (26-1) + 96 (3-1) 342,0 1010101102 Сложим два этих числа 0111111112 1010101102 looToToToT Представим сумму в виде двоичнодесятичного числа 0010 0101 01012.0 Преобразователь работает следующим образом. На входы 3 преобразователя посту пает параллельный двоичный код. Пер вые входы двоичного сумматора 1 под ключены ко входам 3 преобразователя причем на первый вход одноразрядно2 поступает двоичный сумматора го разряд на первый вход однораз

1097995

22 поступает дворядного сумматора ичньп4 разряд 2 , на первый вход од2, поступает норазрядного

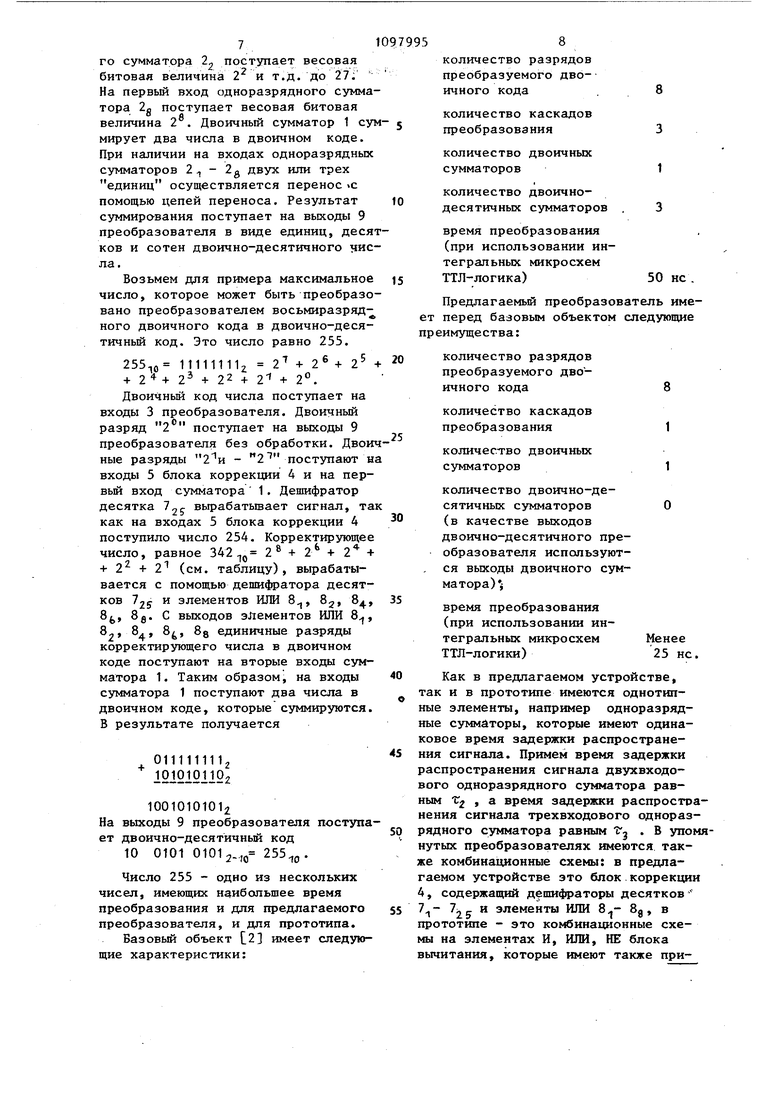

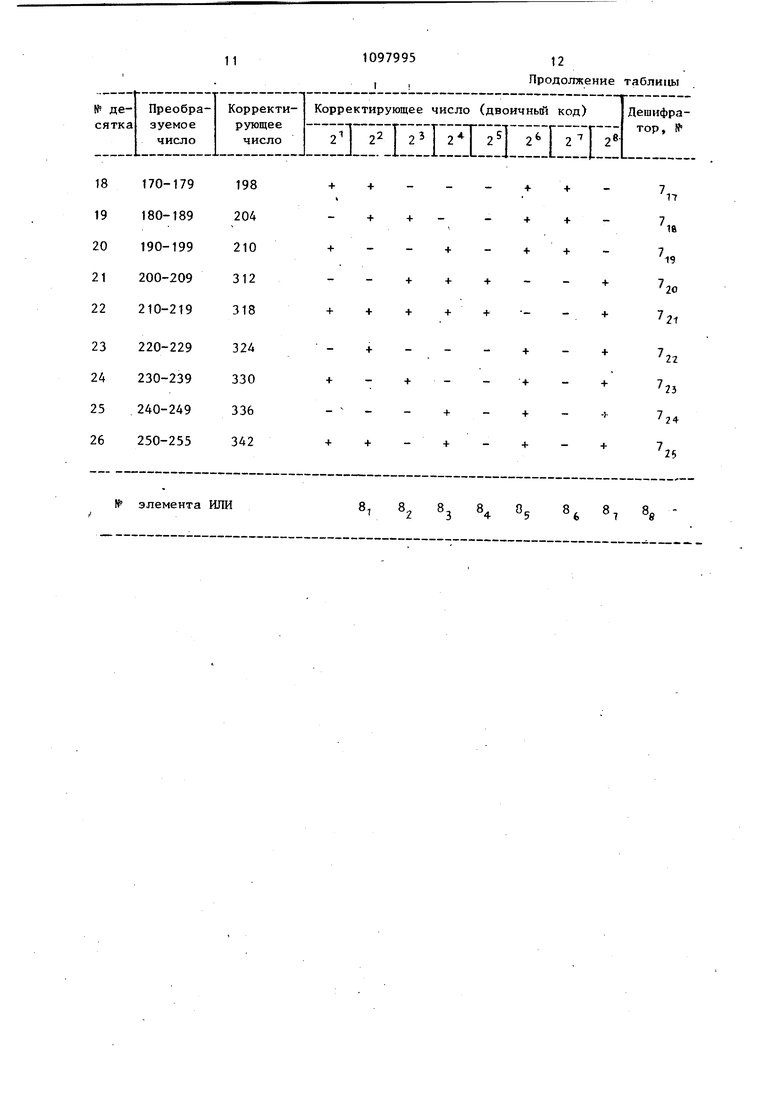

сумматора 23 и двоичньй разряд т.д., на первыи вход одноразрядного сумматора 2-, поступает двоичный разряд 2. Двоичный разряд 2° поступает на выходы 9 преобразователя без обработки, так как на результат преобразования он не влияет. На входы дешифраторов десятков 7 - подключенных ко входам 5 блока коррекции 4, поступают все разряды преобразуемого двоичного числа, кроме разрятак как при вьщелении дополнительного числа этот разряд не используется. Дешифраторы десятков 7-,- дешифрируют двоичный код преобразуемого числа, причем сигнал на выходе дешифратора 7-, вырабатывается в том случае, если на вход блока коррекции 4 поступают числа; 10, 12, 14, 16, 18. Сигнал на выходе дешифратора 7 вьфабатывается в том слу чае, если на вход блока 4 поступают числа: 20, 22, 24, 26, 28 и т.д. Сигнал на выходе дешифратора 72 вырабатывается в том случае, если на вход блока коррекции 4 поступают числа: 250, 252, 254 (см, таблицу). Корректирующее число вырабатывается с помощью дешифраторов десятков 7 - 7 и элементов ИЛИ Sg. Выходы дешифраторов десятков 7 подключены ко входам элементов ИЛИ 8 -- 8д в соответствии с единичными разрядами корректирующего числа. Таким образом на выходах элементов и 8т вьфабатывается число ИЛИ 8, г- 7 в двоичном коде 2 + 2 6 для чисел, находящихся в пределах от 10 до 19. На выходах элементов ИЛИ 8 и 8 вьфабатьшается корректирующее число в двоичном коде 2 12 для чисел, находящихся в пределах от 20 до 29, и т.д. На выходах элементов ИЛИ 8, 8, 8, 8g вырабатьшается корректирующее число в двоичном коде 342 для чисел, находящихся в пределах от 250 до 255 (см. таблицу). С выходов 6 блока коррекции 4 число в двоичном коде поступает на вторые входы одноразрядных сумматоров 2 - 2 и на первый вход одноразрядного сумматора 2g, причем на второй вход одноразрядного сумматора 2 поступает весовая битовая величина 2 , на второй вход одноразрядного сумматора 2 поступает весовая битовая величина 2 и т.д. до 27: На первый вход одноразрядного сумматора 2g поступает весовая битовая величина 2 . Двоичный сумматор 1 сум- 5 мирует два числа в двоичном коде. При наличии на входах одноразрядных сумматоров 2 - 2g двух или трех единиц осуществляется перенос «с помощью цепей переноса. Результат 10 суммиро-вания поступает на вькоды 9 преобразователя в виде единиц, десятков и сотен двоично-десятичного числа. Возьмем для примера максимальное 15 число, которое может быть преобразовано преобразователем восьмиразрядного двоичного кода в двоично-десятичный код. Это число равно 255. 111111112 2+ 2 +20 + 2 + 22 + 2 + 2°. Двоичный код числа поступает на входы 3 преобразователя. Двоичный разряд 2 поступает на выходы 9 преобразователя без обработки. Двоичные разряды 2и - поступают на входы 5 блока коррекции А и на первьй вход сумматора 1 . Дешифратор десятка 72г вьфабатьтает сигнал, так как на входах 5 блока коррекции А поступило число 254. Корректирующее число, равное 342 р 2°+ 2 + 2 (см. таблицу), вырабаты+ 2 + с помощью депшфратора десятваетсяков 7 и злементов ИЛИ 8, 8, 8 2 °4 С выходов элементов ИЛИ 8, 8 / , 81 (, °в 82 8 Of 8i, 83 единичные разряды корректирующего числа в двоичном коде поступают на вторые входы сумматора 1. Таким образом, на входы сумматора 1 поступают два числа в двоичном коде, которые суммируются. В результате получается . 011111111, 1212101122 10010101012 На выходы 9 преобразователя поступает двоично-десятичньй код 10 0101 010l2-,o . Число 255 - одно из нескольких чисел, имеющих наибольшее время преобразования и для предлагаемого преобразователя, и для прототипа. Базовый объект С2 имеет следующие характеристики: 1097995 ет пр та ны ны ко ни ра во ны не ря ну же га 4, 7 пр мы вы 8 количество разрядов преобразуемого двоичного кода количество каскадов преобразования количество двоичных сумматоров количество двоичнодесятичных сумматоров время преобразования (при использовании интегральных микросхем ТТЛ-логика) 50 НС . Предлагаемый преобразователь имеперед базовым объектом следующие имущества: количество разрядов преобразуемого двоичного кода8 количество каскадов преобразования1 количество двоичных сумматоров1 количество двоично-десятичных сумматоров О (в качестве выходов двоично-десятичного преобразователя используются выходы двоичного сумматора); время преобразования (при использовании инМенеетегральных микросхем ТТЛ-логики) 25 НС. Как в предлагаемом устройстве, и в прототипе имеются однотипэлементы, например одноразрядсумматоры, которые имеют одинаое время задержки распространесигнала. Примеь время задержки пространения сигнала двухвходоо одноразрядного сумматора равт , а время задержки распростраия сигнала трехвходового одноразного сумматора равным f, . В упомяых преобразователях имеются таккомбинационные схемы: в предламом устройстве это блок коррекции содержащий деошфраторы десятков 1. и элементы ИЛИ 8 тотипе - это комбинационные схена элементах И, ШШ, НЕ блока итания, которые имеют также при910блиэительно равное время срабатьгаания ввиду одинакового количества каскадов последовательно включенных элементов И, ШШ, НЕ. Примем это время равнымt, тогда м(жко выразить максимапьное время преобразования предлагаемого устройства Т в виде . С -f + . Т - С 2 f, + 6, . Максимальное время преобразования npoTOTiffla Т2 можно вцразить .в виде Tg - 2Г, .+ Sr + llfj . Если сравнить время задержки распространения сигнала Tj и. Т , можно сделать вывод, что 510 раза превосходит быстродействие прототипа. Каскадность преобразова ния и наличие цепей переноса как между блоками внутри каскадов, так и между каскадами, затрудняет введение в прототип схем параллельного переноса, которые еще более усложняют структуру прототипа. ПредлагаемЛ преобразователь имеет всего одну последовательную цепь переносов между одноразрядньми сумматорами 2 . Это позволяет ввести ОДНУ последовательную цепь схем параллельного переноса, при этом бьютро

eduHi cfb/

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1984 |

|

SU1221758A1 |

| Реверсивный преобразовательдВОичНОгО КОдА B дВОичНО-дЕСяТичНый | 1979 |

|

SU849198A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU723567A1 |

| Преобразователь двоичного кода угла в двоично-десятичный код градусов и минут | 1983 |

|

SU1116425A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь двоично-десятичного кода в двоичный Редчина | 1988 |

|

SU1646057A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в десятичный | 1979 |

|

SU868747A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД, содержащий двоичный сумматор, первые входы которого соединены со входами преобразователя, кроме входа младшего разряда, который является выходом младшего разряда преобразователя, отличающийся тем, что, с целью повьшения быстродействия преобразователя, ев него введен блок коррекции, содержащий группу дешифраторов десятков и группу элементов ИЛИ, причем входы дешифраторов десятков соединены со входами блока коррекции в соответствии с весами разрядов, выходы элементов ИЛИ группы соединены с выходами блока коррекции, выход i-го ( i 1-9) дешифратора десятков группы соединены со входами х( ) элементов ИЛИ группы, для которых ( j-е разряды двоичного кода числа 6 имеют единичные значения, выход k -го дешифратора десятков группы ( k 10-99) соединен со входами 6-х элементов ИЛИ группы (t 1 ), для которых

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь двоичного кодаВ дЕСяТичНый | 1979 |

|

SU830371A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

Авторы

Даты

1984-06-15—Публикация

1982-08-26—Подача