(54) МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ -УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Множительно-делительное устройство | 1980 |

|

SU900294A1 |

| Коррелятор | 1975 |

|

SU526917A1 |

| Времяимпульсное множительное устройство | 1988 |

|

SU1642481A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Корреляционный демодулятор сигналов с угловой модуляцией | 1983 |

|

SU1166338A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Преобразователь величины мощности и действующего значения напряжения в цифровой код | 1986 |

|

SU1404952A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1985 |

|

SU1242801A1 |

| Множительно-делительное устройство | 1975 |

|

SU568056A1 |

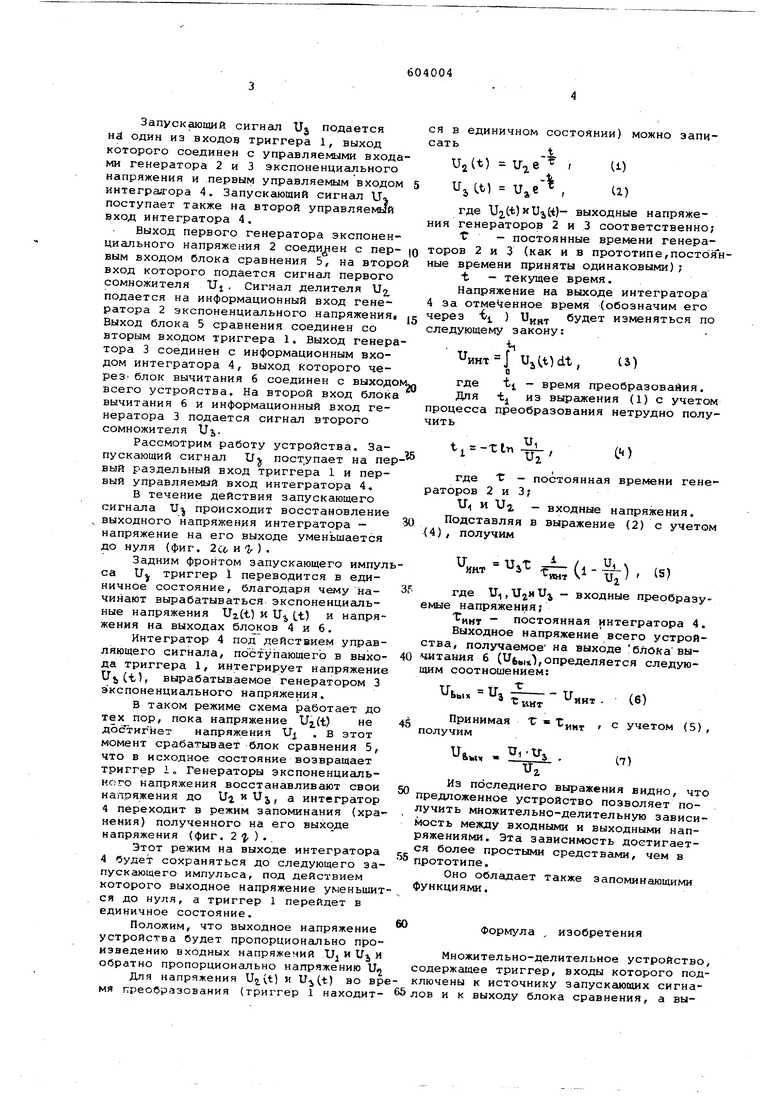

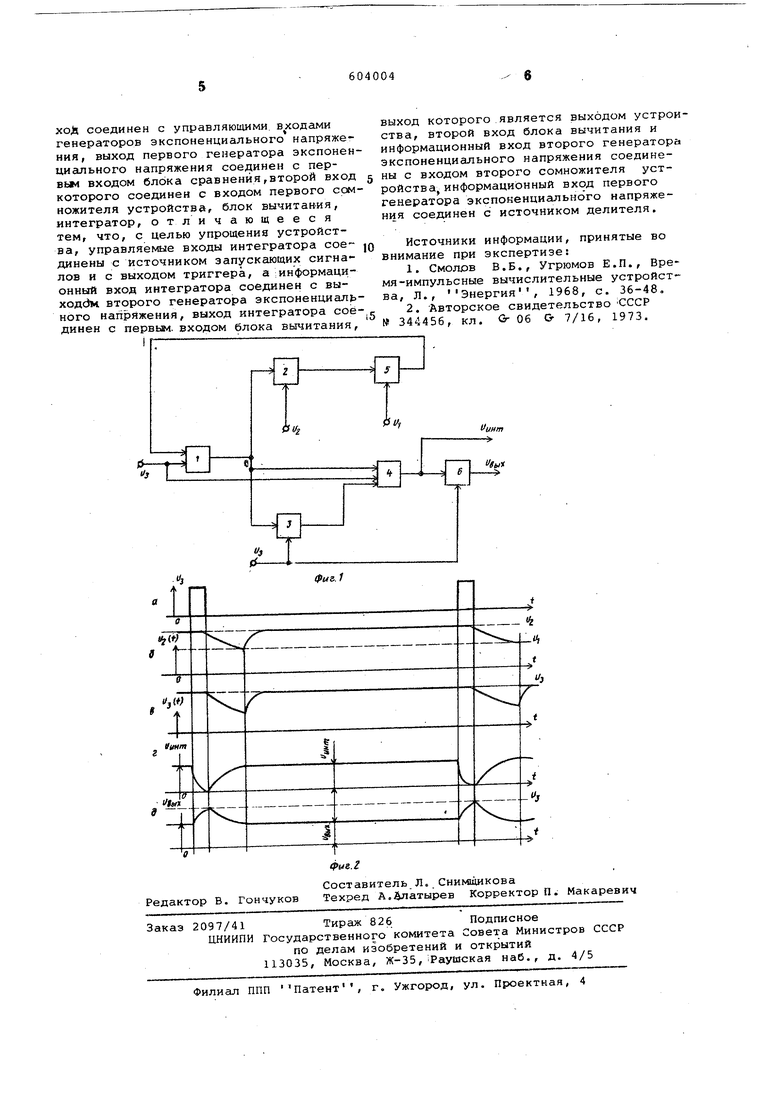

Изобретение относится к вычислитель ной технике и может найти применение в устройствах автоматики и контроля, Для получения множительно-делитель ных зависимостей широкое распространение получили время-импульсные вычислительные устройства, достоинством которых является возможность получения высокой статической точности функциональ ного преобразования 1 Однако для них характерна высокая динамическая погрешность, обусловленна наличием импульсных делителей напряжения, обладающих большой инерционностью. Известно также множительно-делитель ное устройство, содержащее триггер, шходы которого подключены к источнику запускающих сигналов и к выходу блока сравнения, а выход соединен с управляй щими входами генераторов экспоненциаль ного Напряжения, выход первого генератора экспоненциального напряжения соединен с первым входом блока сравнения, второй вход которого соединен с входом первого сомножителя устройства, блок вычитания, интегратор 2. Схема такого устройства сложна и ле обеспечивает запоминания полученного в результате преобразования напря жения. Целью изобретения является упрощение устройства. Это достигается тем,что в предложенном устройстве управляемые входы интегратора соединены с источником запускающих сигналов и с выходом триггера, а информационный вход интегратора соединен с выходом второго генератора экспоненциального напряжения, выход .интегратора соединен с первым входом блока вычитания,выход : соторого является выходом устройства,второй вход блока вычитания и информационный вход второго генератора экспоненциального напряжения соединены с входом второго сомножителя. устройства,информационный вход первого генератора экспоненциального напряжения соединен с источником делителя. На фиг. 1. приведена структурная схема предложенного устройства, где приняты следующие обозначения: 1 триггер, 2 и 3 - генераторы экспонен циального напряжения, 4 - интегратор 5 - блок сравнения, 6 - блок вычитания. На фиг. 2 приведены временные диаграммы, поясняющие работу устройства. Запускающий сигнал Uj подается Het один из входов триггера 1, выход которого соединен с управляемыми вход ми генератора 2 и 3 экспоненциального напряжения и первым управляемым входом интеграя-ора 4. Запускающий сигнал Uj поступает также на второй управляемый вход интегратора 4. Выход первого генератора экспоненциального напряжения 2 соединен с пер вым входом блока сравнения 5, на второ вход которого подается сигнал первого сомножителя Ut . Сигнал делителя U2, подается на информационный вход генератора 2 экспоненцисшьного напряжения. Выход блока 5 сравнения соединен со вторым входом триггера 1. Выход генера тора 3 соединен с информационным входом интегратора 4, выход которого череЗ блок вычитания 6 соединен с выходо всего устройства. На второй вход блок вычитания 6 и информационный вход генератора 3 подается сигнал второго сомножителя Uj. Рассмотрим работу устройства. Запускающий сигнал Uj поступает на пе вый раздельный вход триггера 1 и первый управляемый вход интегратора 4, В течение действия запускающего сигнала U происходит восстановление выходного напряжения интегратора - напряжение на его выхода уменьшается до нуля (фиг. 2сг-и2. ) . Задним фронтом запускающего импул са U) триггер 1 переводится в единичное состояние, благодаря чему начинают вырабатываться экспоненциальные напряжения U2.(t) и U (.t) и напряжения на выходах блоков 4 и 6. Интегратор 4 под действием управляющего сигнала, поступающего в выхода триггера 1, интегрирует напряжение UjCt), вырабатываемое генератором 3 экспоненциального напряжения. В таком режиме схема работает до тех пор, пока напряжение 1/2,(t) не достигнет напряжения U . В этот момент срабатывает блок сравнения 5, что в исходное состояние возвращает триггер 1, Генераторы экспоненциального напряжения восстанавливают свои напряжения до , а интегратор ч переходит в режим запоминания (хранения) полученного на его выходе напряжения (фиг. 2 {. ) . , Этот режим на выходе интегратора 4 Оудет сохраняться до следующего запускающего импульса, под действием которого выходное напряжение уменьшит ся до нуля, а триггер 1 перейдет в единичное состояние. Положим, что выходное напряжение устройства Оудет пропорционально произведению входных напряжений U и Uj И обратно пропорционально напряжению U Для напряжения U(t) и UjCt) во вр мя преовразования (триггер 1 находится в единичном состоянии) можно записатьUjlt) I U) Uj U) , C2) где U2,Ct)fUjtt)- выходные напряжения генераторов 2 и 3 соответственно; Т - постоянные времени генераторов 2 и 3 (как и в прототипе,постоянные времени приняты одинаковыми); t - текущее время. Напряжение на выходе интегратора 4 за отмеченное время (обозначим его через ij, ) будет изменяться по следующему закону: U5tt)dt, CS) где t. - время преобразовайия. Для ± из вырё1жения (1) с учетом процесса преобразования нетрудно получитьЧ где Т - постоянная времени генераторов 2 и 3; Ui и Ui - входные напряжения. Подставляя в выражение (2) с учетом (4), получим Ujt Л- (ч1 JWT Ч и, / где Ui, UjM Uj - входные преобразуемые напряжения; постоянная интегратора 4. Выходное напряжение всего устройства, получаемое на выходе блока вычитания б (,определяется следующим соотношением: Ubb.. из: UHT «« Принимая Т « с учетом (5), получим Ub«x . HiiHs Из последнего выражения видно, что предложенное устройство позволяет получить множительно-делительную зависимость между входными и выходными напряжениями. Эта зависимость достигается более простыми средствами, чем в прототипе. Оно обладает также запомингиощими функциями. Формула , изобретения Множительно-делительное устройство, содержащее триггер, входы которого подключены к источнику запускающих сигналов и к выходу блока сравнения, а вы

Авторы

Даты

1978-04-25—Публикация

1976-01-04—Подача