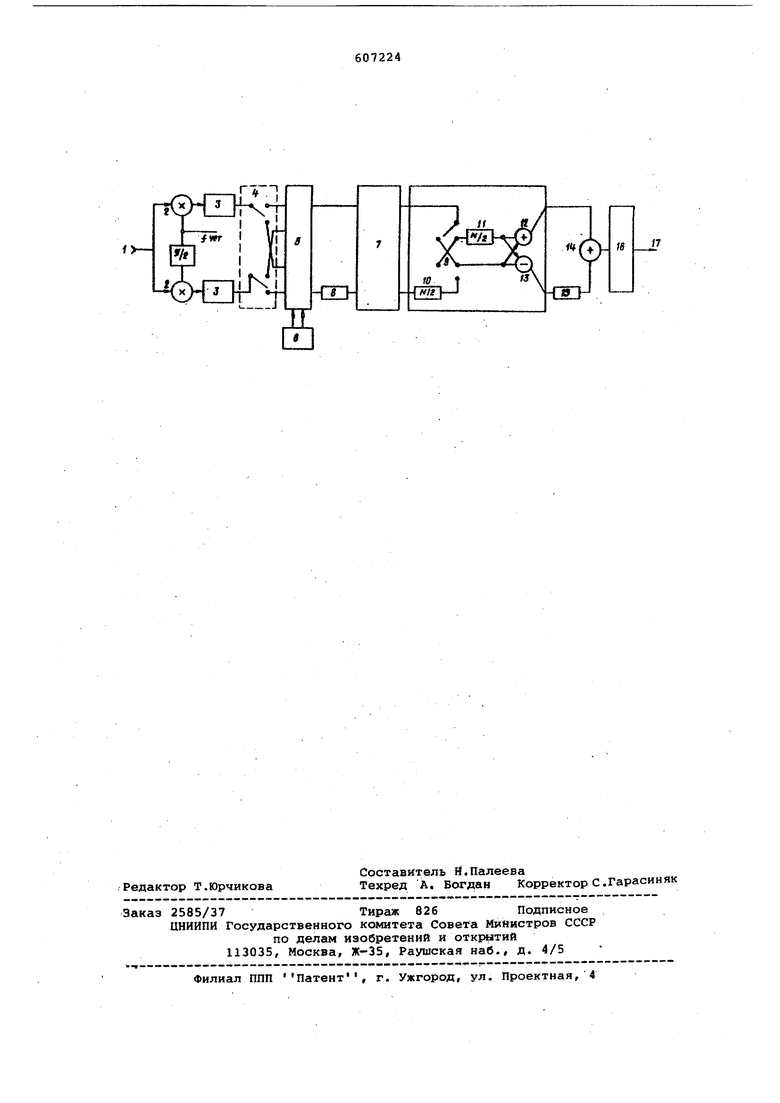

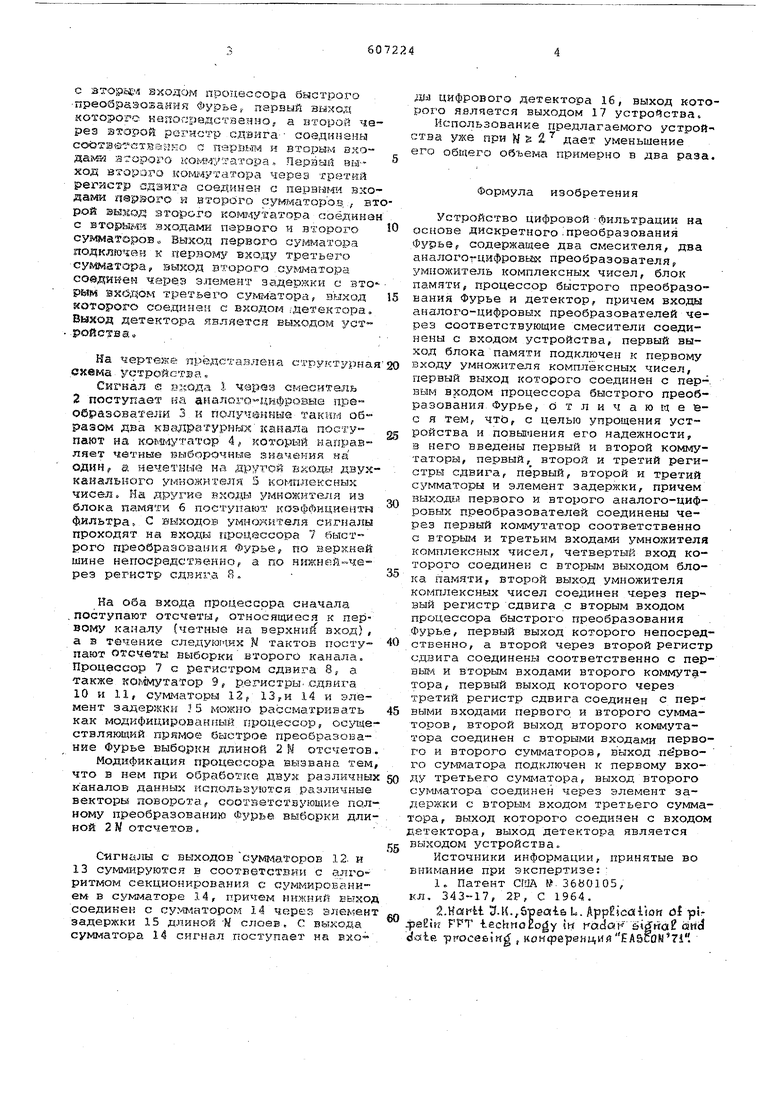

(54) УСТРОЙСТВО ЦИФРОВОЙ ФИЛЬТРАЦИИ НА ОСНОВЕ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ с 3TOS3c 4 ВХОДОМ процвссора быстрого Преобразования Фурье первый выход которого капопрадстванног а второй чареэ второй регистр сдвига- соединаны соотве;ствйнко с парйьш и вторым входа1 «и a opoj;4} ког ту гатора, Пераый выход втораго коьшугатора через третий pernc-sp адзига соединен с первыми входами первого и второго сумматоров, , вт рой эьзкой зто-рого .1утахора соёдина с вторыгд й входами параого и второго сумматоров „ Выход первого суш.-штора яодклю ен к первоад- входу третьего сумматора (, выход второго сум матора соадйнен через элемент задержки с вто рым ахо-дюм третьего су.шатора, выход которого соедннеи с входом ;детектора Выход детектора является выходотл устройства На чертеже гтрёясгавлвиа структурная схема устройства« Сигнал е в;-;ода -I чврваз смеситель 2 поступает на аналого-цифровые преобразователи 3 к полученные таким образом два KBtyipsrypHHx канала поступакэт на ко Фаутатор 4, который направляет четные выборочные значения на ОДИН а нечетные на лругсй входы двух канального умножителя 3 комшшксвых чисел. На другие входда умножителя из блока памятк б поступают коэфйициеитн фильтра. С выходов умножителя сигналы проходят на входы процессора 7 быстрого преобразования Фурье, по верхней шине непосредственноf а по нижнйй--через регистр сдБиг.а S, Ка оба вкода процессора сначала .поступают отсчеты, относящиеся к первому каналу (четные на BepxHPiff вход) , а в течение сле,цую1пих М тактов поступают отсчеты выборки второго канала. Процессор 7 с регистром сдвиг-а 8, а также кo йvIyтaтop 9, р.егистры .сдвига 10 и 11, сумматоры 12t 13,и 14 и элемент задержки 3 5 можно рассматривать как лодифиц1фованиый процессор, осуще ствляющий прямое быстрое преобразование Фурье выборкн длиной 2 N отсчетов Модификация процессора вызвана тем что в нем при обработке двух различны каналов данных используются различные векторы поворота, соответствующие пол ному преобразованию Фурье выборки дли ной 2W отсчетов, Сигналы с выходов сумматоров 12. и 13 суммируются в cooTBeTCTBHirS с алх оритмом секционирования с суммированием в cyNMaTope 14, причем н ганий ЕЫКО соедикек с су лтлатором 14 через элемен задержки 15 дл.иной М слоев, С выхода сумматора 14 сигнал поступает на вхо дуо цифрового детектора 16, выход которого является выходом 17 устройства. Использование предлагаемого устройтва уже при Мй 2 дает уменьшение го общего объема примерно в два раза. Формула изобретения Устройство цифровой -фильтрации на основе дискретного .преобразования Фурьер содержащее два смесителя, два аналогогцифровьж преобразователя, умножитель комплексных чисел, блок памятк, процессор быстрого преобразования Фурье и детектор, причем входы аналого-цифровых преобразователей через соответствующие смесители соединены с входом устройства, первый выход блока памяти подключен к первому входу умножителя комшшксных чисел, первый выход которого соединен с пер-, вым входом процессора быстрого преобразования. Фурье, d т л и ч а ю м е ес я тем, , с целью упрощения устройства и повьлиения его надежности, в него введены первый и второй коммутаторы, первый, второй и третий регистры сдвига, первый, второй и третий сумматоры и элемент задержки, причем выходы первого и второго аналого-цифровых преобразователей соединены через парный коммутатор соответственно с вторЫ./ и третьим входами умножителя комплексных чисел, четвертый вход которого соединен с вторым выходом блока памяти, второй выход умножителя комплексных чисел соединен через первый регистр сдвига с вторым входом процессора быстрого преобразования Фурь.е, первый выход которого непосредственно, а второй через второй регистр сдвига соединены соответственно с первюд и вторым входами второго коммут тора, первый выход которого через третий регистр сдвига соединен с первыми входами первого и второго сумматоров , второй выход второго коммутатора соединен с вторыми входами первого и второго cyMiviaToppB, выход .пйрвого сумматора подключен к первому входу третьего сумматора, выход второго сум:.1атора соединен через элемент задержки с вторым входом третьего сумматора, выход которого соединен с входом детектора, выход детектора является выходом устройства. Источники информации, принятые во внимание при экспертизе:; 1. Патент crUA .36Й0105, кл, 343-17, 2Р, С 1964. S.KafH 3.K.,Spgaiu L. AppEicaiioH df pi-psEiK FPT techno ogy m radaF attd date pfoceeiitg , конференций EA5cQW7i.

/7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрацииНА OCHOBE диСКРЕТНОгО пРЕОбРАзОВА-Ния фуРьЕ | 1979 |

|

SU840922A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Устройство диагностики динамических объектов | 1986 |

|

SU1352394A1 |

| СПОСОБ (ВАРИАНТЫ) И УСТРОЙСТВО (ВАРИАНТЫ) ОЦЕНИВАНИЯ НЕСУЩЕЙ ЧАСТОТЫ | 1998 |

|

RU2137143C1 |

| Устройство для измерения относительной задержки импульсных сигналов | 1982 |

|

SU1068886A1 |

| Устройство для контроля работы транспортного средства | 1986 |

|

SU1345222A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ | 1995 |

|

RU2090902C1 |

| ПРИЕМНИК СПУТНИКОВЫХ НАВИГАЦИОННЫХ СИГНАЛОВ С БЛОКОМ БЫСТРОГО И ВЫСОКОЧУВСТВИТЕЛЬНОГО ПОИСКА | 2010 |

|

RU2444027C2 |

Авторы

Даты

1978-05-15—Публикация

1975-03-27—Подача