входом узля и с выходом узла, а вторые входы элементов группы элементов И соединены с третьим управляющим входом узла 3,

Недостаток вычислительного узла состоит в том, что при решении с его помощью трехмерных задач математической физики значительно возрастают затраты оборудования и время вычислений.

Цель изобретения - сокращение оборудования и времени вычислений.

Это достигается тем, что вычислительный узел содержит блок умножения, последовательный вход, параллельные входы и выход которого соединены соответственно с выходом миоговходового сумматора, с группой кодовых входов узла и последовательным входом регистра сдвига.

Кроме того, в вычислительном узле блок умножения .содержит п-разрядный сумматор с запоминанием переносов и элементы И, причем первые, вторые входы и выходы элементов И соединены соответственно с параллельными входами блока, с последовательным входом блока и входами п-разрядного сумматора С запоминанием переносов, в котором выход суммы к1аждого разряда соединен с входом соседнего младшего разряда, выход переноса разряда - с входом разряда, а выход младшего разряда сумматора соединен с выходом блока умножения.

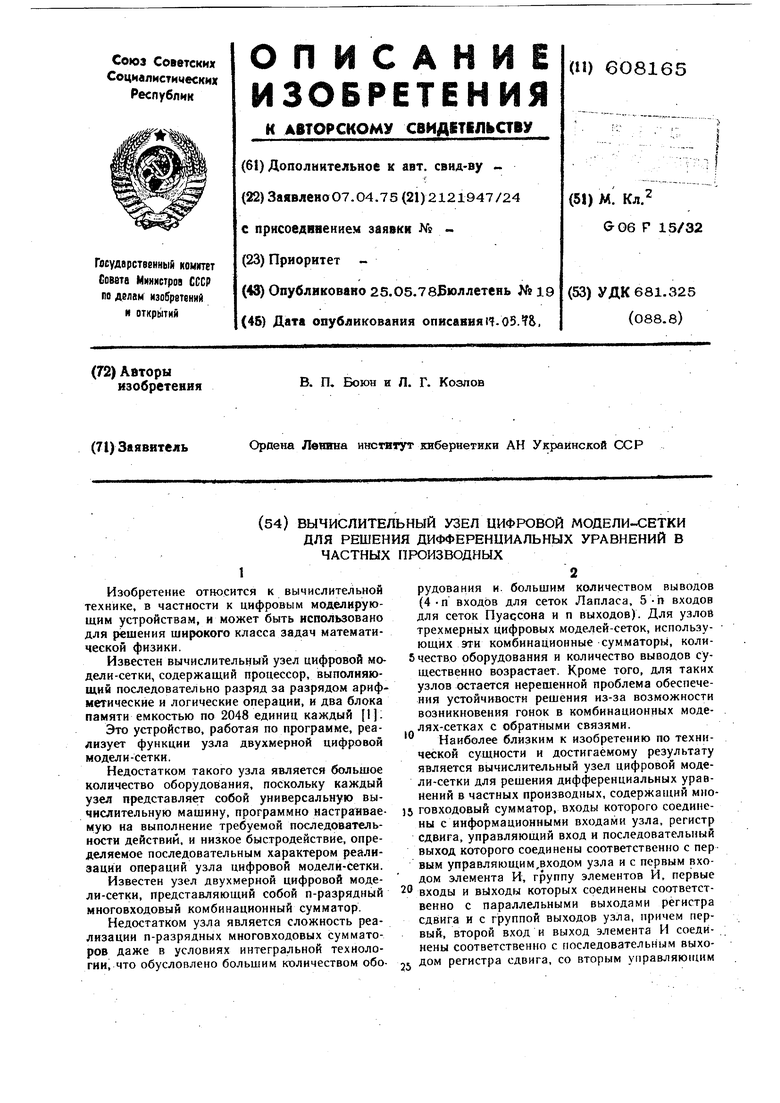

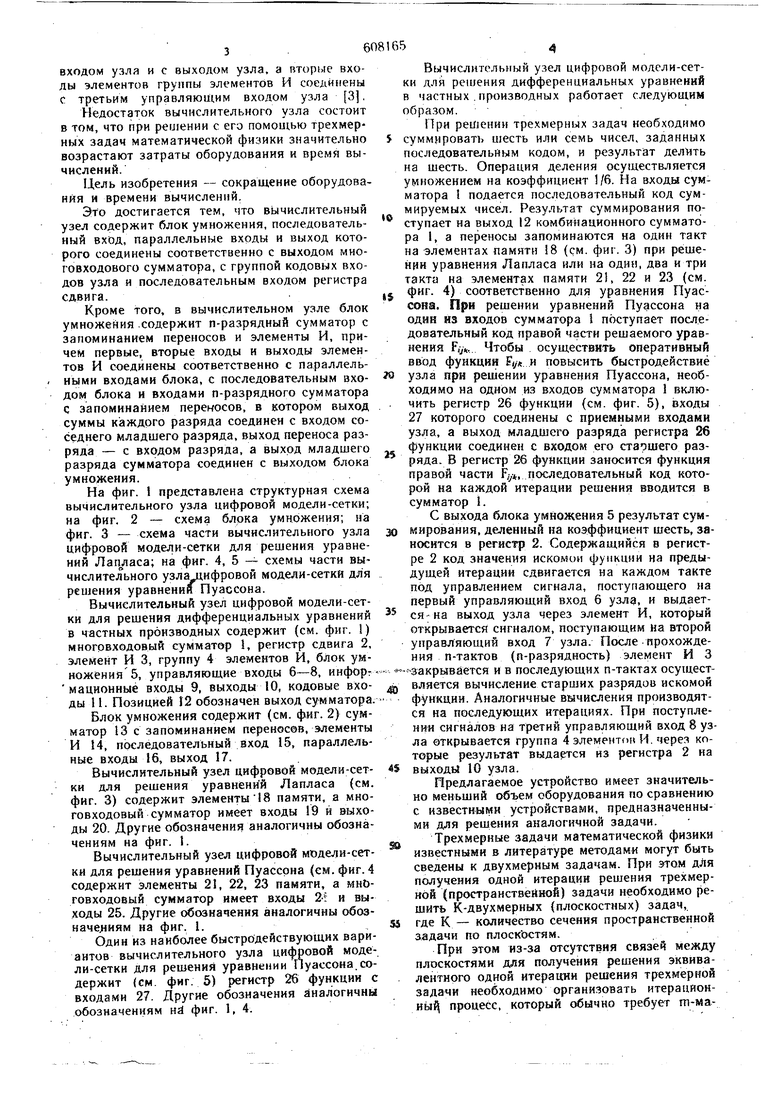

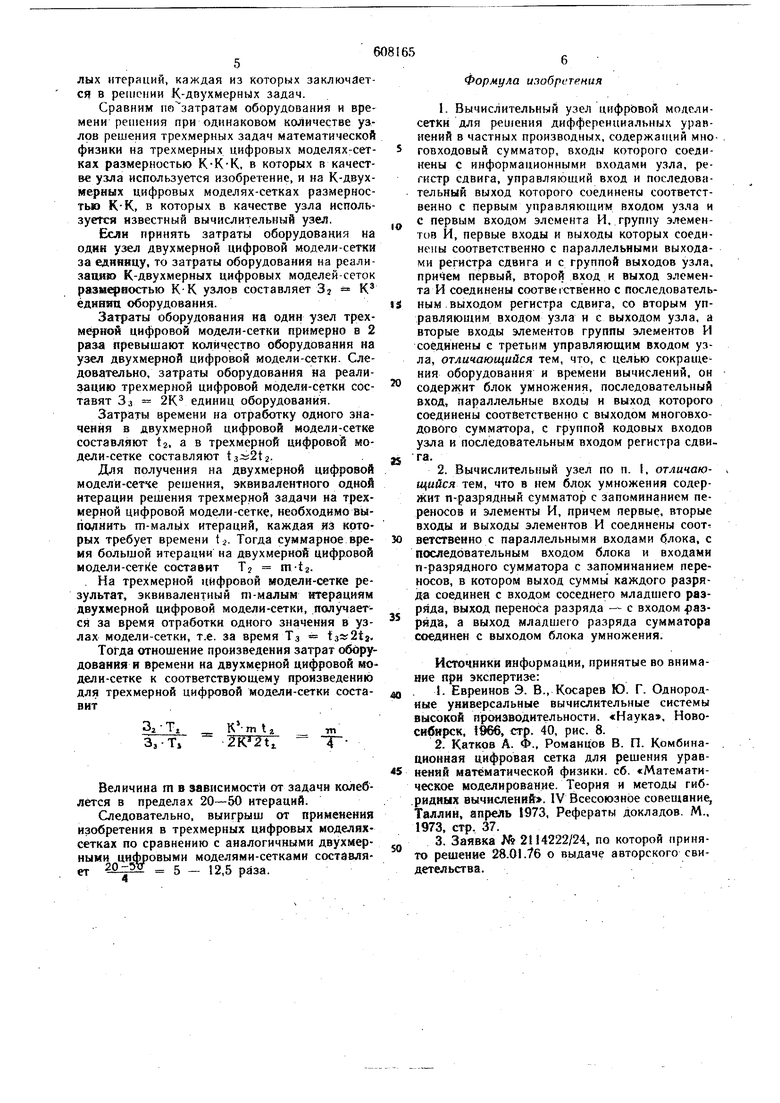

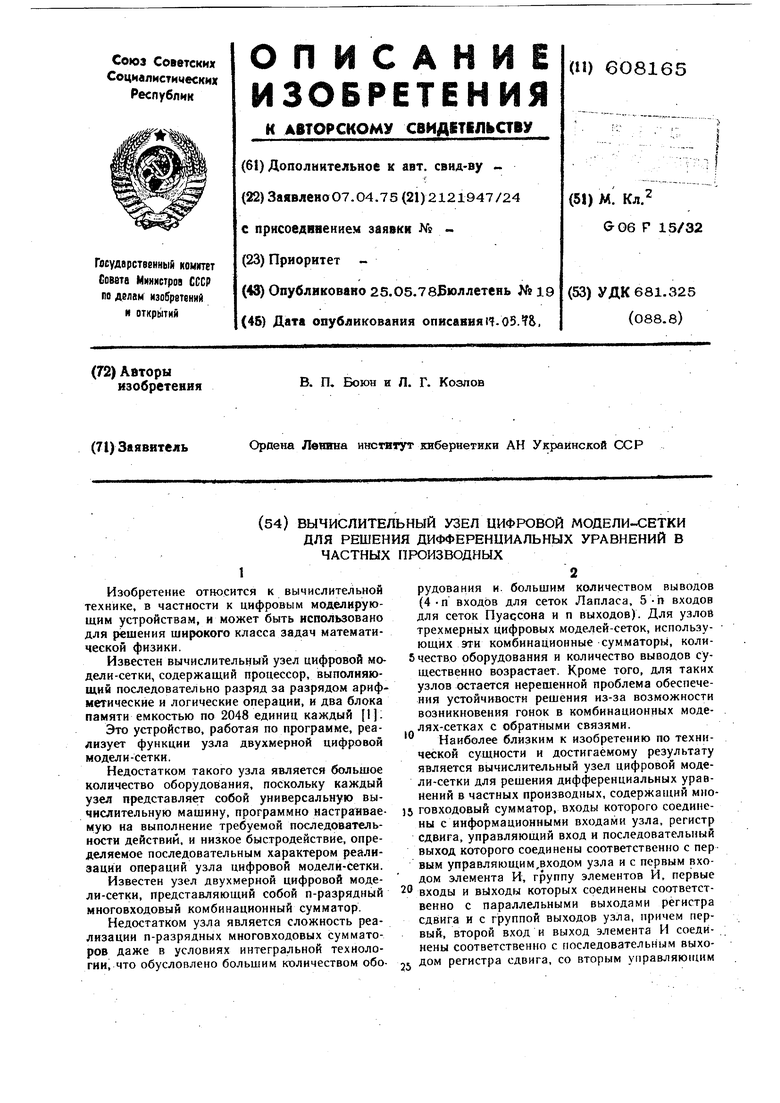

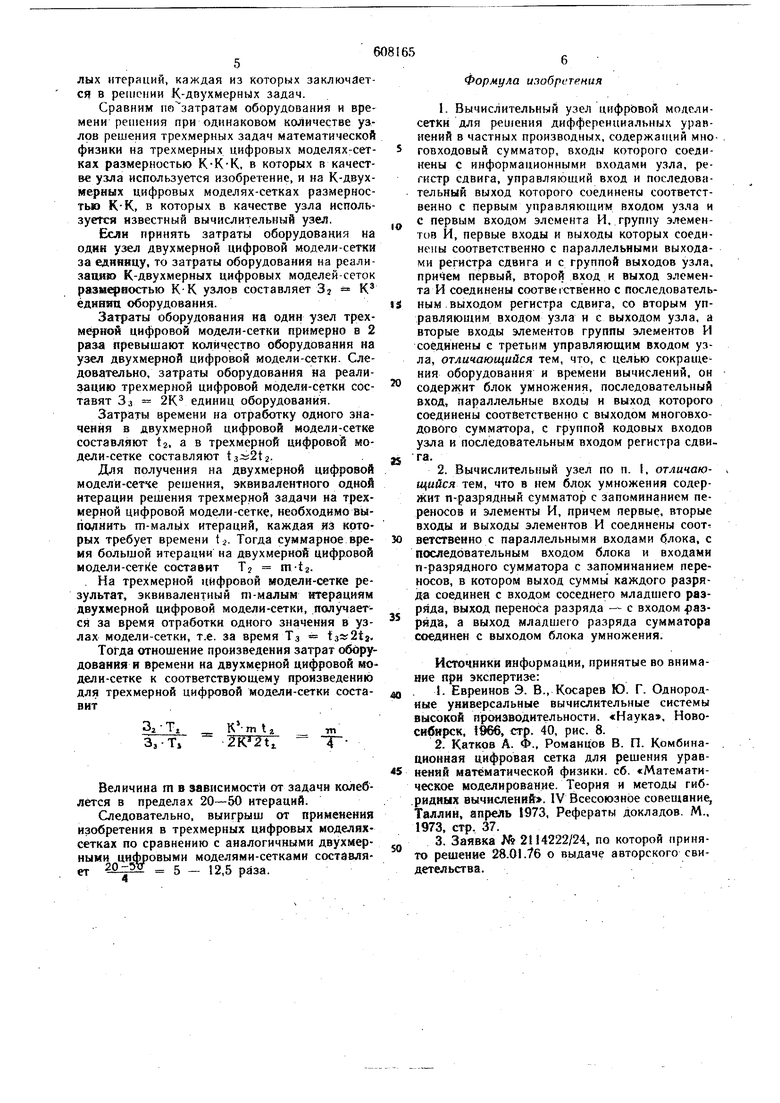

На фиг. 1 представлена структурная схема вычислительного узла цифровой модели-сетки; на фиг. 2 - схема блока умножения; на фиг. 3 - схема части вычислительного узла цифровой модели-сетки для решения уравнений Лапласа; на фиг. 4, 5 -- схемы части вычислительного узлал ифровой модели-сетки для решения уравнении Пуассона.

Вычислительный узел цифровой модели-сетки для решения дифференциальных уравнений в частных производных содержит (см. фиг. 1) многовходовый сумматор 1, регистр сдвига 2, элемент И 3, группу 4 элементов И, блок умножения 5, управляющие входы 6-8, информационные входы 9, выходы 10, кодовые входы 11. Позицией 12 обозначен выход сумматораБлок умножения содержит (см. фиг. 2) сумматор 13 с запоминанием переносов, элементы И 14, последовательный вход 15, параллельные входы 16, выход 17.

Вычислительный узел цифровой модели-сетки для рещения уравн ений Лапласа (см. фиг. 3) содержит элементы18 памяти, а многовходовый сумматор имеет входы 19 и выходы 20. Другие обозначения аналогичны обозначениям на фиг. 1.

Вычислительный узел цифровой модели-сетки для решения уравнений Пуассона (ем. фиг. 4 содержит элементы 21, 22, 23 памяти, а мнЬговходовый сумматор имеет входы 2-i и выходы 25. Другие обозначения аналогичны обозначед1иям на фиг. 1.

Один из наиболее быстродействующих вариантов вычислительного узла цифровой модели-сетки для решения уравнении Пуассона содержит см. фиг. 5) регистр 26 функции с входами 27. Другие обозначения аналогичны обозначениям ни фиг. 1, 4.

Вычислительный узел цифровой модели-сетки для решения дифференциальных уравнений в частных . производных работает следующим образом.

При решении трехмерных задач необходимо J суммировать шесть или семь чисел, заданных последовательным кодом, и результат делать на шесть. Операция деления осуществляется умножением на коэффициент 1/6. На входы сумматора I подается последовательный код суммируемых чисел. Результат суммирования поступает на выход 12 комбинационного сумматора 1, а переносы запоминаются на один такт на элементах памяти 18 (см. фиг. 3) при рещенин уравнения Лапласа или на один, два и три такта на элементах памяти 21, 22 и 23 (см.

фиг. 4) соответственно для уравнения Пуассона, При решении уравнений Пуассона на один из входов сумматора 1 поступает последовательный код правой части решаемого уравнения Fyv Чтобы осуществить оперативный ввод функции Fly и повысить быстродействие

узла при peaieHHH уравнения Пуассона, необходимо на одном из входов сумматора 1 включить регистр 26 функции (см. фиг. 5), входы 27 которого соединены с приемными входами узла, а выход младшего разряд;а регистра 26 функции соединен с входом его ставшего разряда. В регистр 26 функции заносится функция правой части F;,, последовательный код которой на каждой итерации решения вводится в сумматор 1.

С выхода блока умножения 5 результат суммирования, деленный на коэффициент шесть, заносится в регистр 2. Содержащийся в регистре 2 код значения искомой функции на предыдущей итерации сдвигается на каждом такте под управлением сигнала, поступающего на первый управляющий вход 6 узла, и выдает ся-на выход узла через элемент И, который открывается сигналом, поступающим на второй управляющий вход 7 узла. После прохождения п-тактов (п-разрядность) элемент И 3 «-Закрывается и в последующих п-тактах осуществляется вычисление старших разрядов искомой функции. Аналогичные вычисления производятся на последующих итерациях. При поступлении сигналов на третий управляющий вход 8 узла открывается группа 4 элементом И. через которые результат выдается из регистра 2 на

S выходы 10 узла.

Предлагаемое устройство имеет значительно меньший объем оборудования по сравнению с известными устройствами, предназиаченными для решения аналогичной задачи.

Трехмерные задачи математической физики известными в литературе методами могут быть сведены к двухмерным задачам. При этом для получения одной итерации рещения трехмерной (пространственной) задачи необходимо решить К-двухмерных (плоскостных) задач,

5 где К - количество сечения пространствениой задачи по плоскостям.

При этом из-за отсутствия связей между плоскостями для получения решения эквивалеитного одной итерации решения трехмерной задачи необходимо организовать итерационны процесс, который обычно требует т-малых итераций, каждая из которых заключается 8 решении К-двухмерньзх задач. Сравним позатратам оборудования и времени решения при одинаковом количестве узлов решения трехмерных задач математической физики на трехмерных цифровых моделях-сетках размерностью К-К-К. в которых в качестве узла используется изобретение, и на К-двухмерных цифровых моделях-сетках размерностью К-К, в которых в качестве узла используется известный вычислительный узел. Если принять затраты оборудования на один узел двухмерной цифровой модели-сетки за единицу, то затраты оборудования на реализацию К-двухмерных цифровых моделей-сеток разнервостью К-К узлов составляет 3 К ёднниц оборудования. Затраты оборудования на один узел трехмерной цифровой модели-сетки примерно в 2 раза превышают количество оборудования на узел двухмерной цифровой модели-сетки. Следовательно, затраты оборудования на реализацию трехмерной цифровой модели-сетки составят Зз 2К единиц оборудования. Затраты времени на отработку одного значения в двухмерной цифровой модели-сетке составляют t2, а в трехмерной цифровой модели-сетке составляют . Для получения на двухмерной цифровой моделй-сетче решения, эквивалентного одной итерации решения трехмерной задачи на трехмерной цифровой модели-сетке, необходимо выполнить т-малых итераций, каждая из которых требует времени t. Тогда суммарное время большой итерации на двухмеркой цифроеой модели-сетКе составит Тг m-ta На трехмерной цифровой модели-сетке результат, эквивалентный т-малым итерациям двухмерной цифровой модели-сетки, получается за время отработки одного значения в узлах модели-сетки, т.е. за время Тз , Тогда отношение произведения затрат оборудования и времени на двухмерной цифровой модели-сетке к соответствующему произведенииэ для трехмерной цифровой модели-сетки составитК у t г Величина m в зависимости от задачи колеблется в пределах 20-50 итераций. Следовательно, выигрыш от применения изобретения в трехмерных цифровых моделяхсетках по сравнению с аналогичными двухмерными цифровыми моделями-сетками составляет 2fir52 5 - 2,5 раза. Формула изобр1-тения 1.Вычислительный узел цифровой моделисетки для решения дифференциальных уравнений в частных производных, содержащий многовходовый сумматор, входы которого соединены с информационными в.ходами узла, регистр сдвига, управляющий вход и последовательный выход которого соединены соответственно с первым управляющим входом узла и с первым входом элемента И. группу элементов И, первые в.ходы и выходы которых соединены соответственно с параллельными выходами регистра сдвига и с группой выходов узла, причем первый, второй вход и выход элемента И соединены соотвегственно с последовательным, выходом регистра сдвига, со вторым управляющим входом узла и с выходом узла, а вторые входы элементов группы элементов И соединены с третьим управляющим входом узла, отличающийся тем, что, с целью сокращения оборудования и времени вычислений, он содержит блок умножения, последовательный вход, параллельные входы и выход которого соединены соответственно с выходом многовходового сумматора, с группой кодовых входов узла и последовательным входом регистра сдвига. 2.Вычислительный узел по п. I, отличающийся тем, что в нем блок умножения содержит п-разрядный сумматор с запоминанием переносов и элементы И, причем первые, вторые входы и выходы элементов И соединены соот ветственно с параллельными входами блока, с последовательным входом блока и входами п-разрядного сумматора с запоминанием переносов, в котором выход суммы каждого разряда соединен с входом соседнего младшего разряда, выход переноса разряда - с входом разряда, а выход младшего разряда сумматора соединен с выходом блока умножения. Источники информации, принятые во внимание при экспертизе: 1.Евреинов Э. В., Косарев Ю. Г. Однородные универсальные вычислительные системы высокой производительности. «Наука, Новоибирск, 1966, стр. 40, рис. 8. 2.Катков А. Ф., Романцов В. П. Комбина- . ционная цифровая сетка для решения уравнений математической физики, сб. «Математическое моделирование. Теория и методы гибридиых вычислений. IV Всесоюзное совещание, аллин, апрель 1973, Рефераты докладов. М., 1973, стр. 37. 3.Заявка М« 2114222/24, по которой принято решение 28.01.76 о выдаче авторского свидетельства.

-Ч

АО./

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел устройства для решения уравнений в частных производных | 1991 |

|

SU1833892A1 |

| Вычислительный узел цифровой моделисетки для решения дифференциальных уравнений в частных производных | 1975 |

|

SU546891A1 |

| Вычислительный узел цифровойСЕТКи | 1979 |

|

SU800997A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ТРЕХМЕРНЫХ ЗАДАЧ МАТЕМАТИЧЕСКОЙ ФИЗИКИ | 1991 |

|

RU2051411C1 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Сеточный микропроцессор | 1978 |

|

SU763904A1 |

| Устройство для решения трехмерных задач математической физики | 1975 |

|

SU603997A1 |

| Вычислительный узел для однородной вычислительной системы | 1979 |

|

SU982008A1 |

| Устройство для решения двумерных задач математической физики | 1991 |

|

SU1833891A1 |

in

J i IN iai

r,.....-, Ф R

Ла.4

Я

Авторы

Даты

1978-05-25—Публикация

1975-04-07—Подача