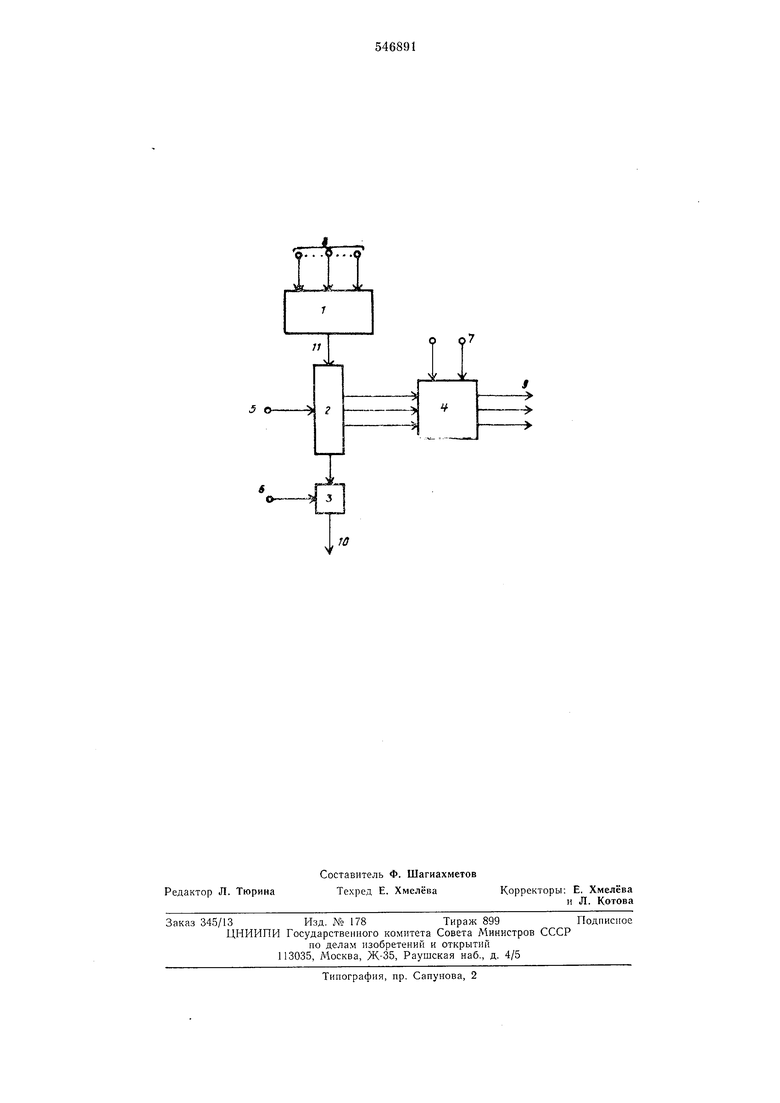

или пяти (для уравнения Пуассона) чисел младо.1ими разрядами вперед. Каждый г-й разряд этих чисел поступает на входы 8 сумматора 1, на выходе 11 которого формируется результат суммирования. Переносы в следующие разряды запоминаются на соответствуюUUIX элементах памяти сумматора 1 (не показаны), причем при решении уравнения Лапласа все три переноса используются в следующем такте при суммировании (i+l)-ro разряда чисел, а при решении уравнеиия Пуассона одии из переносов запоминается на один такт и используется при суммировании (t + + 1)-го разряда чисел, а второй перенос запоминается на два такта и используется при суммировании (t + 2)-ro разряда чисел. При решеиии уравнения Пуассона на один из входов 8 подается последовательный код Гц правой части уравнения.

Для оперативного ввода значения Рц во всех вычислительных узлах цифровой моделисетки и повышения быстродействия величина Fij может быть предварительно занесена параллельным кодом на предусмотренный для этой цели регистр, на выходе которого формируется последовательный код величины Рц на каждой итерации решения.

Результат суммирования каждого разряда чисел, полученный на выходе 11 многовходового сумматора 1, заносится в регистр сдвига 2, содержащийся в регистре сдвига 2 код значения искомой функции на предыдущей итерации сдвигается на каждом такте под управлением сигнала, поступающего на первый управляющий вход 5 узла и выдается на выход 10 через элемент И 3, который открывается сигналом, поступающим на второй управляющий вход 6. После прохождения п (где п- разрядность) тактов элемент И 3 закрывается и в последующих двух тактах осуществляется сдвиг содержимого регистра сдвига 2 на два разряда (т. е. деление на четыре), что и требуется для реализации известной зависимости

fij-i + fij-n + fi-ij + ,j + 1

Последующие итерации осуществляются аналогично и, когда решение получено, на третий управляющий вход 7 поступает сигнал, который открывает группу 4 элементов И, через которую результат выдается из регистра сдвига 2 на группу выходов 9 узла.

Технико-экономический эффект изобретения заключается в том, что описываемый узел превосходит известные узлы цифровых сеток как по наименьщим затратам оборудования, так и ио устойчивости рещения. В известном узле цифровой сетки содержится п многовходовых сумматоров 1, а в описываемом узле один многовходовый сумматор 1 и другие блоки (регистр сдвига 2, элемент И 3, группа 4 элементов И), которые по суммарным аппаратурным затратам (при ) не превосходят затрат оборудования на один многовходовый сумматор. Таким образом, изобретение позволяет достичь сокращения затрат оборудования

не менее, чем в-- раз. Поскольку изобретение

значительно проще известных, то оно может быть использовано в цифровых сетках, содержащих больщое количество узлов, что необходимо для достижения высокой точности рещения. Введение синхронизации и искусственной инерционности в устройство позволяет получать устойчивую модель, исключает положительные обратные связи и тем самым расширяет область применения описываемого узла.

Формула изобретения

Вычислительный узел цифровой модели- сетки для решения дифференциальных уравнений в частных производных, содержащий многовходовый сумматор, входы которого соединены со входами узла, отличающийся тем, что, с целью повышения устойчивости процесса решения и сокращения оборудования, он содержит регистр сдвига, элемент И и группу элементов И, причем выход сумматора соединен с последовательным входом регистра сдвига, управляющий вход и последовательный выход которого соединены соответственно с первым управляющим входом узла и первым входом элемента И, второй вход и выход которого соединены соответственно со вторым управляющим входом и выходом узла, параллельные выходы регистра сдвига соединены с первыми входами элементов И группы элементов И, вторые входы которых соединены с третьим управляющим входом узла, группа выходов которого соединена с выходами элементов И группы элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел цифровой моделисетки для решения дифференциальных уравнений в частных производных | 1975 |

|

SU608165A1 |

| Вычислительный узел устройства для решения уравнений в частных производных | 1991 |

|

SU1833892A1 |

| Устройство для решения двумерных задач математической физики | 1991 |

|

SU1833891A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ТРЕХМЕРНЫХ ЗАДАЧ МАТЕМАТИЧЕСКОЙ ФИЗИКИ | 1991 |

|

RU2051411C1 |

| Сеточный микропроцессор | 1978 |

|

SU763904A1 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Вычислительный узел цифровойСЕТКи | 1979 |

|

SU800997A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1981 |

|

SU976448A1 |

| Устройство для решения двумерныхзАдАч МАТЕМАТичЕСКОй физиКи | 1978 |

|

SU811272A1 |

Авторы

Даты

1977-02-15—Публикация

1975-03-17—Подача