1

Изобретение относится к области вычислительной и измерительной техники и может бытьиспользовано для контроля исправности многоканальных программируемых систем синхронизации, для которых важное значение имеют временные фазовые соотношения формируемых синхроимпульсов.

Известно устройство для контроля систем а-1 1хронизации, содержащее два триггера, выходы которых соединены со входом элемента сравнения, выход которого через исполнительный элемент подсоединен к счетному входу одного из триггеров и два элемента ИЛИ , входы которых подсоединены соответственно к нечетным и четным выходам источника последовательности импульсов, а выходы - к нулевому и единичному входу второго триггера I.

Недостатками такого устройства являются ограниченное быстродействие и число режимов контроля фазовых соотношений в системе синхронизации.

Наиболее близклм техническим решением к изобретению является устройство для контроля систем синхронизации, содержащее схему сравнения, входы которой соединены с выходами триггеров, а выход является контрольным выходом устройства 2.

Известное устройство имеет недостаточное быстродействие, которое определяется двойной задержкой в триггере, задержкой в эле.менте неравнозначности и элементах, образующих обратную связь между выходом триггера и его вторым входом синхронизации, а также задержкой на задание тактового импульса, поступаю. щего на вторые входы элементов. Это ограничивает также разрешающую способность устройства при проверке фазовых соотношений в каналах контролируемого устройства.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство введены элементы И, ИЛИ, инверторы и дополнительные триггеры, входы которых являются входами установки режимов контроля устройства. Прямой и инверсный выходы первого триггера соединены соответственно с первыми входами первого и третьего и первыми входами второго и четвертого элементов И, прямой и инверсный выходы второго дополнительного триггера соединены соответственно со вторыми входа.ми первого и второго и вторыми входа.ми третьега и четвертого элементов И. Третьи входы перв;)го и второго элементов И соединены соответственно со входом первого и входом второго инверторов, а также с первым

и вторым информационными входами устпойст ва. Третьи входы третьего и четвертого элементов И соединены соответственно с выходом первого и второго инверторов. Выходы элементов И подключены ко входам элемента ИЛИ, выход которого соединен со входом синхронизации триггеров, информационные входы и выходы которых являются соответственно входами и выходами устройства.

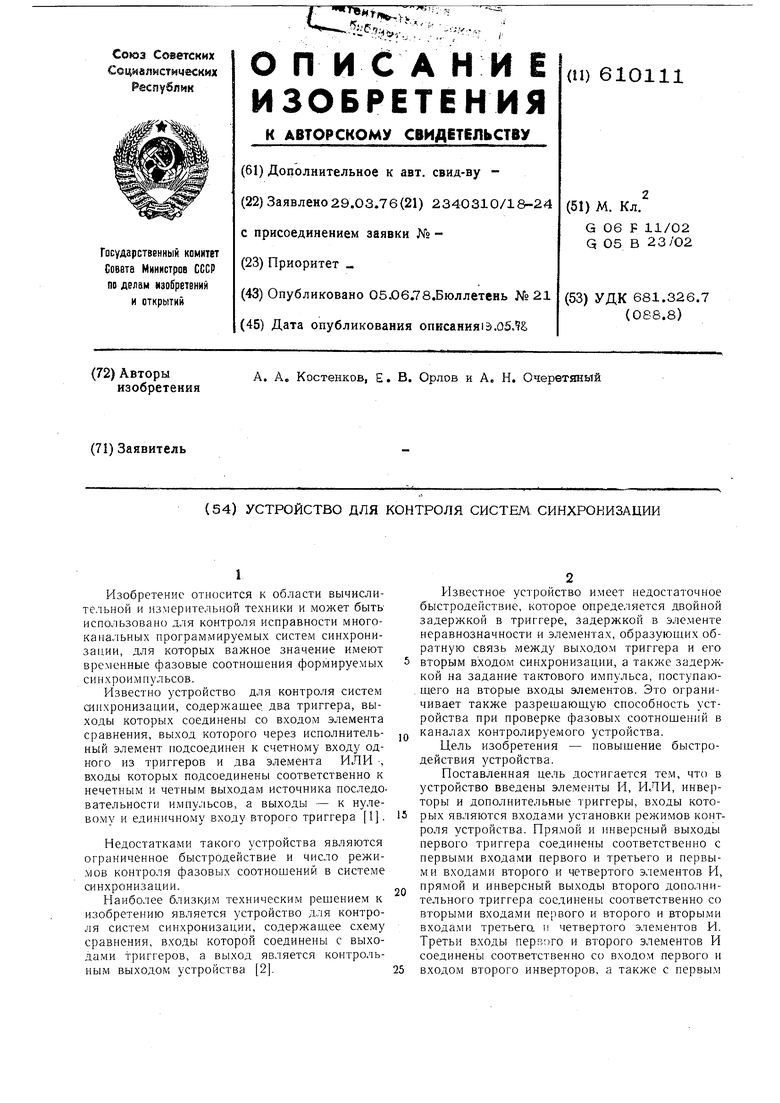

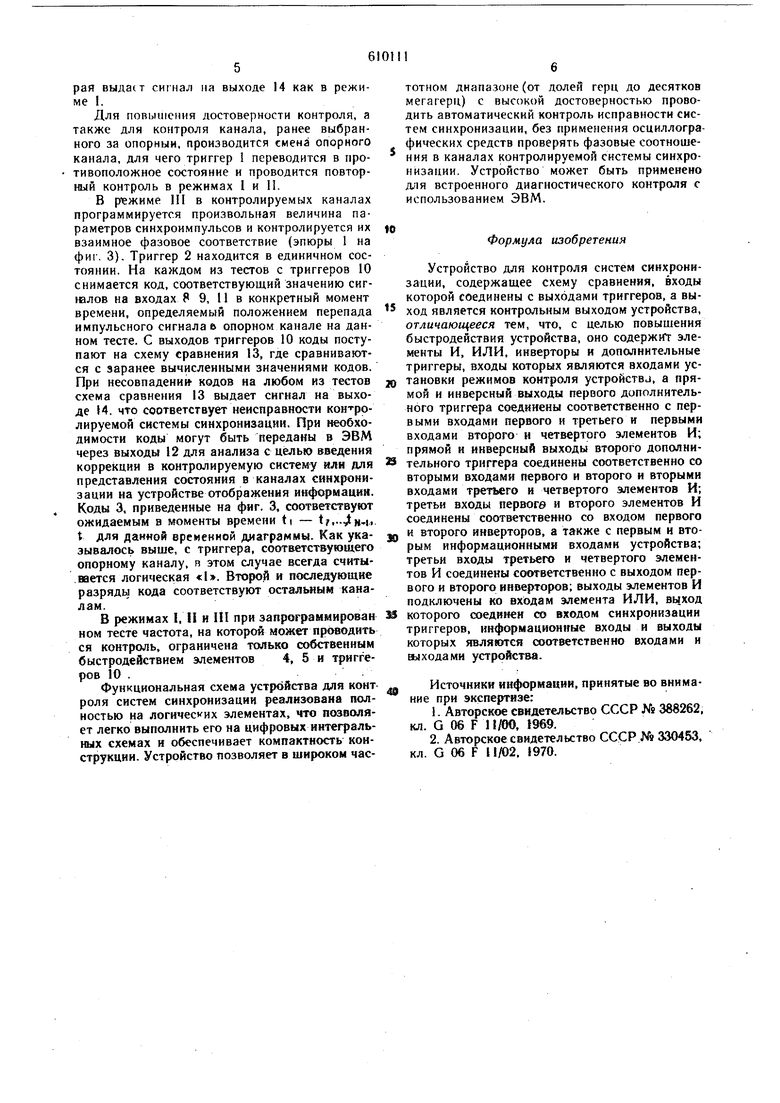

Структурная схема устройства дана на фиг. 1, где обозначены дополнительные триггеры 1 и 2, входы 3 установки режимов контроля, элементы И 4, элемент ИЛИ 5, инверторы 6 и 7, первый 8 и второй 9 информационные входы устройства, триггеры 10, информационные входы 11 устройства, выходы устройства 12, схема сравнения 13 и контрольный выход 14,

Принц|1п работы устройства основан на одновременной записи сигналов с информационных входов 8, 9 и П устройства, к которым подключены выходы контролируемых каналов системы синхронизации, в триггеры 10 в моменты времени, определяемые положением одного из перепадов импульсного сигнала в одном из двух каналов, принятых за опорные (в данном примере выбраны триггеры 10, срабатывающие по положительному перепаду импульсного сигнала). Информация с выходов триггеров 10 подается на входы схемы сравнения 3, где сравнивается с кодом, вычисленным заранее и соответствующим правильной работе контролируемой системы. Кроме того, с выходов триггеров 10 код через выходы 12 устройства считывается в ЭВМ для анализа. По результатам анализа при необходимости вводится коррекция в контролируемые каналы системы синхронизации. Выбор опорного канала производится триггером 1, выбор режима контроля (фазы фронта нлн фазы среза) - триггером 2.

Устройство работает в трех режимах контроля информационных сигналов: режиме I (контроль фазы фронта), режиме И (контроль фазы среза) и режиме 1,11 (контроль соотношений запрограммированных в каналах системы синхронизацин параметров сигналов величина задержки и длительности синхроимпульса в различных точках диапазона).

Контрольным тестом будем считать соотношение импульсных сигналов в опорном канале и во всех остальных при заданных величинах параметров синхроимпульса (задержка и длительность) во всех каналах контролируемой системы при определенном состоянии триггеров 1 и 2.

При работе устройства в режиме I трнггер 2 устанавливается в единичное состояние на первом выходе.

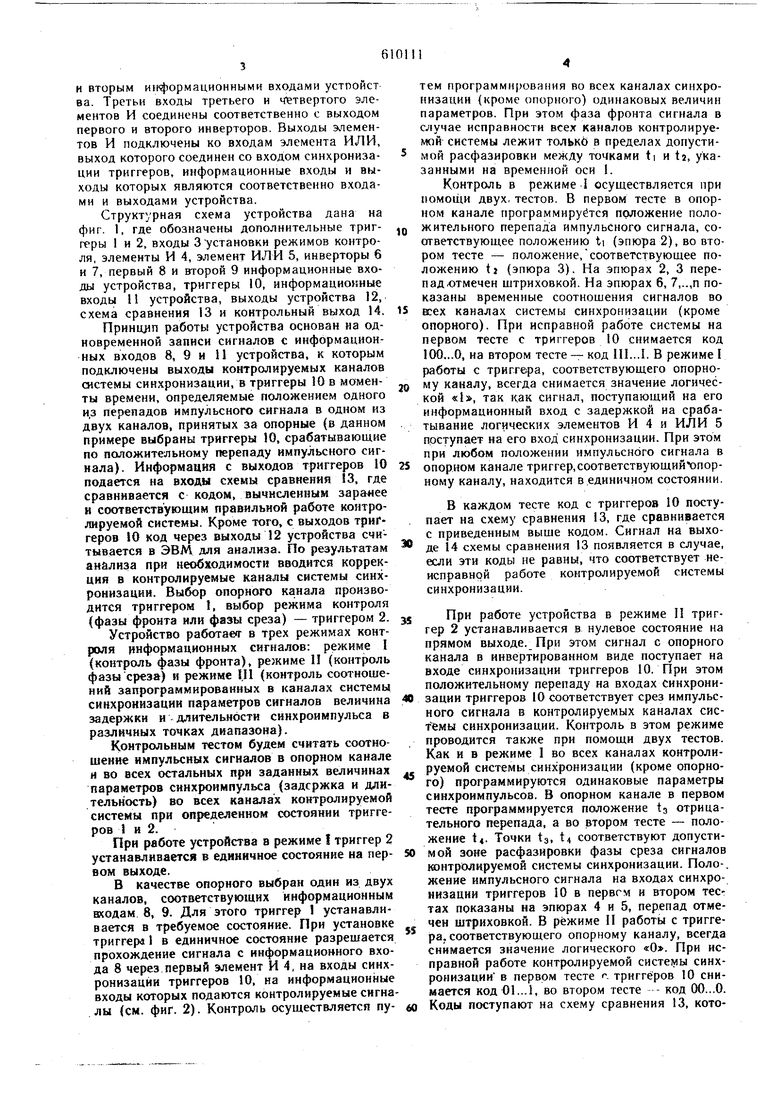

В качестве опорного выбран один на двух каналов, соответствующих информационным входам 8, 9. Для этого трнггер 1 устанавливается в требуемое состояние. При установке триггера 1 в еднннчное состояние разрешается прохождение сигнала с информационного входа 8 через первый элемент И 4, на входы синхронизации триггеров 10, на информационные входы которых подаются контролируемые снгналы (см. фиг. 2). Контроль осуществляется путем программирования во всех каналах синхронизации (кроме опорного) одинаковых величин параметров. При этом фаза фронта сигнала в случае исправности всех каналов контролируемой системы лежит только а пределах допустимой расфазировки между точками ti и tj, указанными на временной оси 1.

Контроль в режиме i осуществляется при iioMoiiui двух, тестов. В первом тесте в опорном канале программируется положение положительного перепада импульсного сигнала, сосггветствующее положению ti (эпюра 2), во втором тесте - положен не,соответствующее положению tj (эпюра 3). На эпюрах 2, 3 перепад ютмечен щтриховкой. На эпюрах 6, 7,..,п показаны временные соотношения сигналов во всех каналах системы синхронизации (кроме опорного). При нсправной работе системы на первом тесте с триггеров 10 снимается код 100...О, на втором тесте - код II1...I. В режиме I работы с триггера, соответствующего опорному каналу, всегда снимается значение логической «1, так как сигнал, поступающий на его информационный вход с задержкой на срабатывание логических элементов И 4 и ИЛИ 5 поступает на его вход синхронизации. При этом при любом положении импульсного сигнала в опорном канале триггер,соответствующийЧ)порному каналу, находится в единичном состоянии.

В каждом тесте код с триггеров 10 поступает на схему сравнения 13, где сравнивается с приведенным выще кодом. Сигнал на выходе 14 схемы сравнения 13 появляется в случае, если эти коды не равны, что соответствует неисправной работе контролируемой системы синхронизации.

При работе устройства в режиме II триггер 2 устанавливается в нулевое состояние на прямом выходе. При этом сигнал с опорного канала в инвертированном виде поступает на входе синхронизации триггеров 10. При этом положительному перепаду на входах синхронизацин триггеров 10 соответствует срез импульсного сигнала в контролируемых каналах системы синхронизации. Контроль в этом режиме проводится также прн помощн двух тестов. Как н в режиме 1 во всех каналах контролируемой системы синхронизации (кроме опорного) программируются одинаковые параметры синхроимпульсов. В опорном канале в первом тесте программируется положение tj отрицательного перепада, а во втором тесте - положенне ti. Точки ta, t4 соответствуют допустимой зоне расфазнровки фазы среза сигналов контролируемой системы синхронизации. Поло-, женне импульсного сигнала на входах сннхроннзацни триггеров 10 в первгм и втором тестах показаны на эпюрах 4 и 5, перепад отмечен штриховкой. В режиме II работы с триггера, соответствующего опорному каналу, всегда снимается значение логического «О. При исправной работе контролируемой системы синхронизации в первом тесте f. триггеров 10 снимается код 01...1, во втором тесте - код 00...0. Коды поступают на схему сравнения 13, которая выдан сигма; на выходе 14 как в режиме 1.

Для повыигения достоверности контроля, а также для контроля канала, ранее выбранного за опорный, производится смена опорного канала, для чего триггер 1 переводится в противоположное состояние и проводится повторный контроль в режимах I и П.

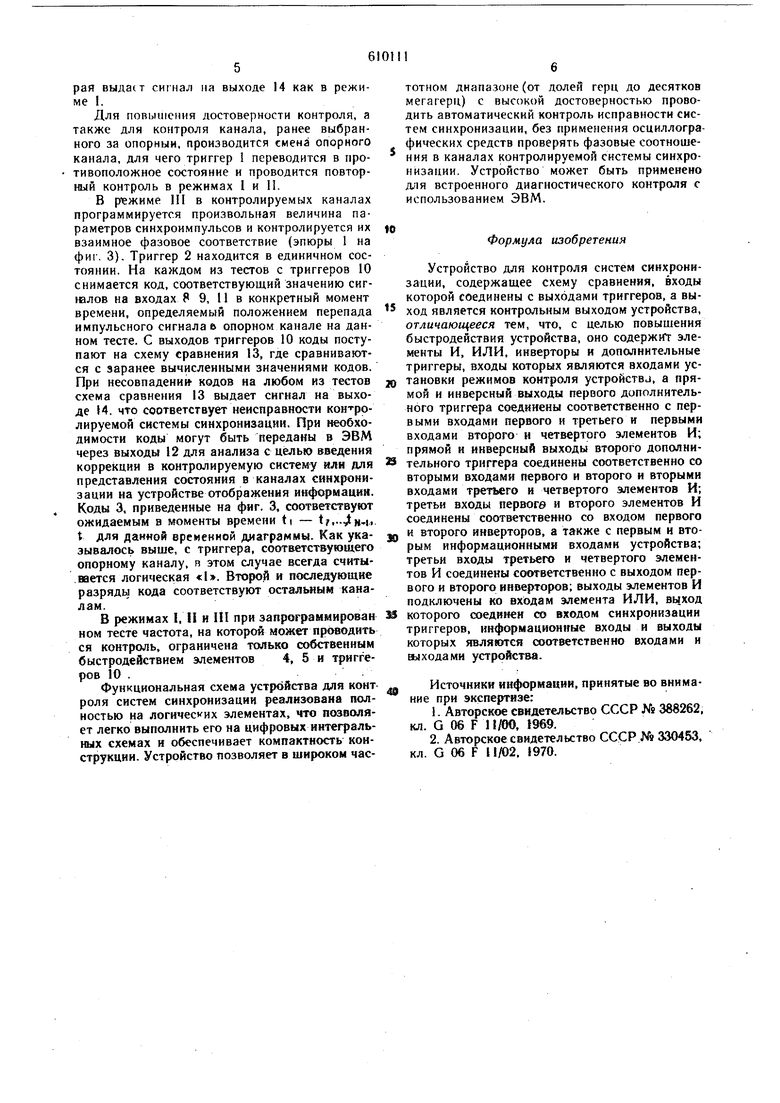

В р ежиме III в контролируемых каналах программируется произвольная величина параметров синхроимпульсов и контролируется их to взаимное фазовое соответствие (эпюры 1 на фи1. 3). Триггер 2 находится в единичном состоянии. На каждом из тестов с триггеров 10 снимается код, соответствующий значению сигналов на входах 8 9, 11 в конкретный момент времени, определяемый положением перепада импульсного сигнала в опорном канале на данном тесте. С выходов триггеров 10 коды поступают на схему сравнения 13, где сравниваются с заранее вычисленными значениями кодов. При несовпадени кодов на любом из тестов JQ схема сравнения 13 выдает сигнал на выходе 14, что соответствует неисправности контролируемой системы синхронизации. При необходимости коды могут быть переданы в ЭВМ через выходы 12 для анализа с целью введения коррекции в контролируемую систему или для 29 представления состояния в каналах синхронизации на устройстве отображения информация. Коды 3, приведенные на фиг. 3, соответствуют ожидаемым в моменты времени ti - tj,..jt,i, t для данной временной диаграммы. Как ука- у) зывалось выше, с триггера, соответствующего опорному каналу, в этом случае всегда считывается логическая «1. Второй и последующие разряды кода соответствуют остальным каналам.

В режимах I, П и III при запрограммирован 3S иом тесте частота, иа KOTOpcrft может проводить ся контроль, ограничена только собственным быстродействием элементов 4, 5 и триггеров 10 .

Функциональная схема устройства для конт- „ роля систем синхронизации реализована полностью на логичес их элементах, что позволяет легко выполнить его на цифровых интегральных схемах и обеспечивает компактность конструкции. Устройство позволяет в широком частотном диапазоне(от долей герц до десятков мегагерц) с высокой достоверностью проводить автоматический контроль исправности систем синхронизации, без применения осциллографическнх средств проверять фазовые соотношения в каналах контролируемой системы синхронизации. Устройство может быть применено для встроенного диагностического контроля с использованием ЭВМ.

Формула изобретения

Устройство для контроля систем синхронизации, содержащее схему сравнения, входы которой соединены с выходами триггеров, а выход является контрольным выходом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно coдepж rr элементы И, ИЛИ, инверторы и дополнительные триггеры, входы которых являются входами установки режимов контроля устройства, а прямой и инверсный выходы первого дополнительного триггера соединены соответственно с первыми входами первого и третьего и первыми входами второго и четвертого элементов И; прямой и инверсный выходы второго дополнительного триггера соединены соответственно со вторыми входами первого и второго и вторыми входами третьего и четвертого элементов И; третьи входы первоге и второго элементов И соединены соответственно со входом первого и второго инверторов, а также с первым и вторым информационными входами устройства; третьи входы третьего и четвертого элементов И соединены соответственно с выходом первого и второго инверторов; выходы элементов И подключены ко входам элемента ИЛИ, выход которого соединен со входом синхронизации триггеров, информационные входы и выходы которых являются соответственно входами и Еыхода ми устройства.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР № 388262, кл. G 06 F П. 1969.

2.Авторское свидетельство СССР № 330453, кл. G 06 F И/02, {970.

6-lQMl

,,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многоканальных систем синхронизации | 1978 |

|

SU744482A1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1987 |

|

SU1443745A1 |

| Устройство магнитной записи и воспроизведения двухчастотных сигналов | 1983 |

|

SU1129648A1 |

| Устройство для задержки импульсов | 1981 |

|

SU993455A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Устройство контроля амплитуды переменного напряжения | 1986 |

|

SU1354122A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Многоканальный формирователь одиночных импульсов | 1985 |

|

SU1243115A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

j i i i Hi

att

tj i« t

i,t2

Pi;, 2

г t, t2 tj и tf is tr «ч n t

1 i t t I

0 1 I 1 1 0 00 0 a a a 1 ito

0 0 I I 0

1 0 0 0 -0 000

0

Авторы

Даты

1978-06-05—Публикация

1976-03-29—Подача