(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МНОГОКАНАЛЬНЫХ СИСТЕМ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля систем синхронизации | 1976 |

|

SU610111A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| МИКРОПРОЦЕССОРНЫЙ ЭЛЕКТРОПРИВОД | 1998 |

|

RU2141164C1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1982 |

|

SU1077539A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для контроля времени установления цифроаналогового преобразователя | 1990 |

|

SU1786660A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

. ;: .1,

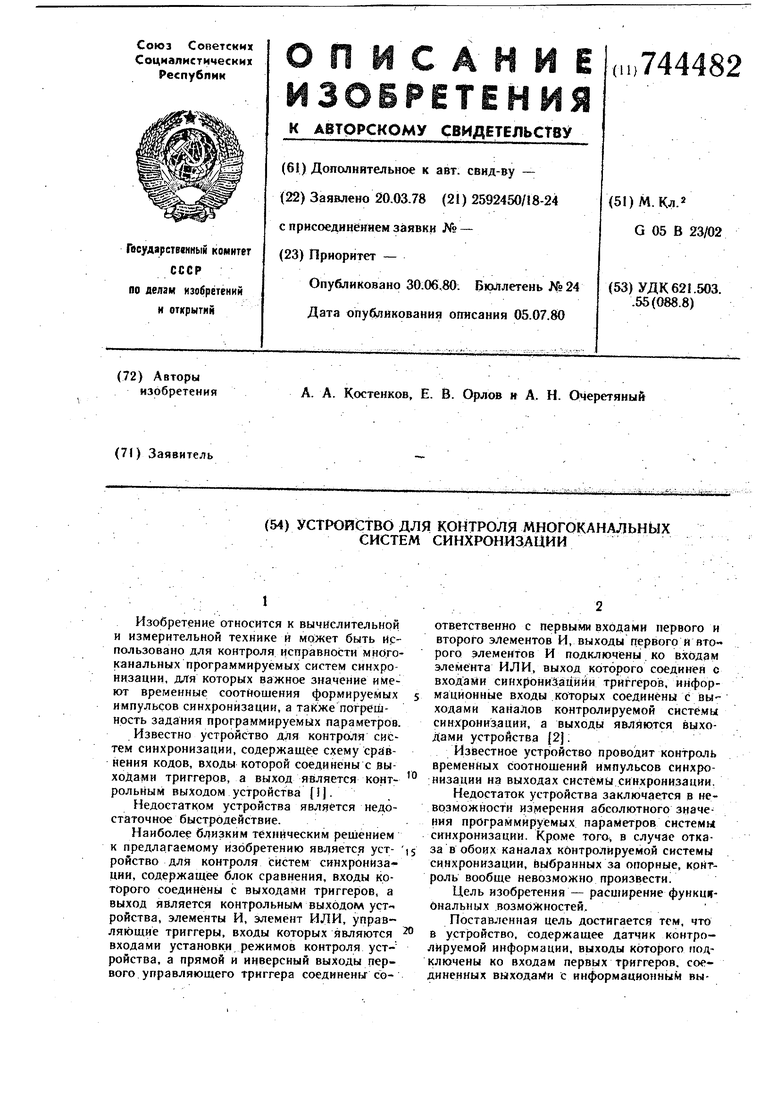

Изобретение относится к вычислительной и измерительной технике и может быть Использовано для контроля исправности мн)гоканальных программируемых систем синхронизации, для которых важное значение имеют временные соотношения формируемых импульсов синхронизации, а также погрешность задания программируемых параметров.

Известно устройство для контроля систем синхронизации, содержащее схему сравнения кодов, входы которой соединеиы с выходами триггеров, а выход является контрольным выходом устройства (.

Недостатком устройства является недостаточное быстродействие.

Наиболее близким техническим решением к предлагаемому изобретению является устройство для контроля систем синхронизации, содержаш ее блок сравнения, входы которого соединены с выходами триггеров, а выход является контрольным выходом устройства, элементы И, элемент ИЛИ, управляющие триггеры, входы которых являются входами установки режимов контроля устройства, а прямой и инверсный выходы первого управляющего триггера соединены соответственно с первыми входами первого и второго элементов И, выходы первого и второго элементов И подключены .ко входам элемента ИЛИ, выход которого соединен с входами сннхрониЗацййи триггеров, информационные входы которых соединены с выходами каналов контролируемой системы синхронизации, а выходы являются выходами устройства (2J.

Известное устройство проводит контроль

временных соотношений Импульсов синхроto

:низаиии на выходах системы синхронизации.

Недостаток устройства заключается в невозможности измерения абсолютного значения программируемых параметров снстемы синхронизации. Кроме тога, в случае отказа в обоих каналах контролируемой системы

15 синхронизации, выбранных за опорные, контроль вообще невозможно произвести.

Цель изобретения - расширение функциональных возможностей.

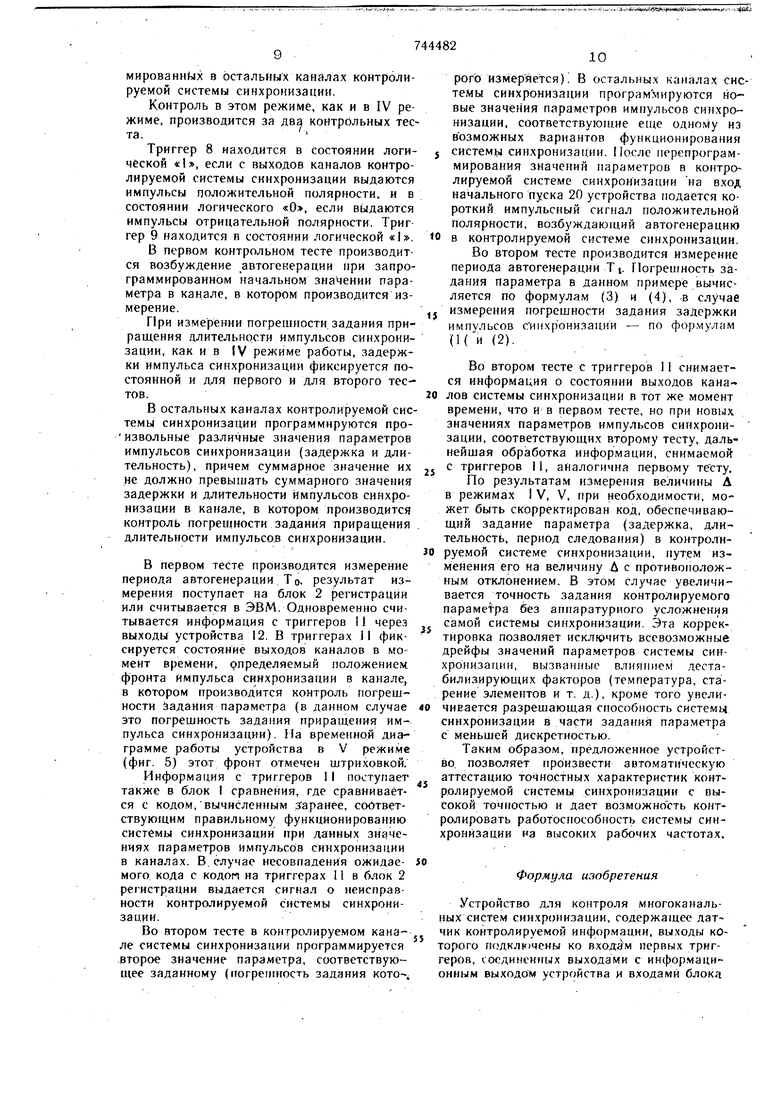

Поставленная цель достигается том, что

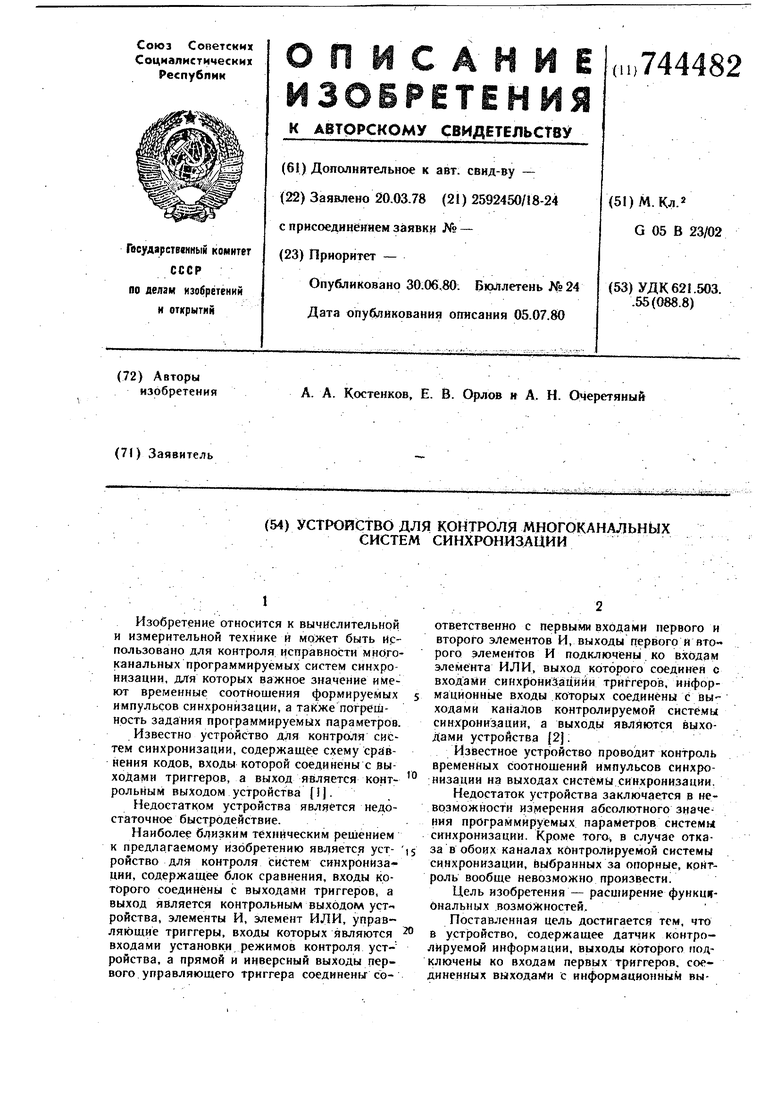

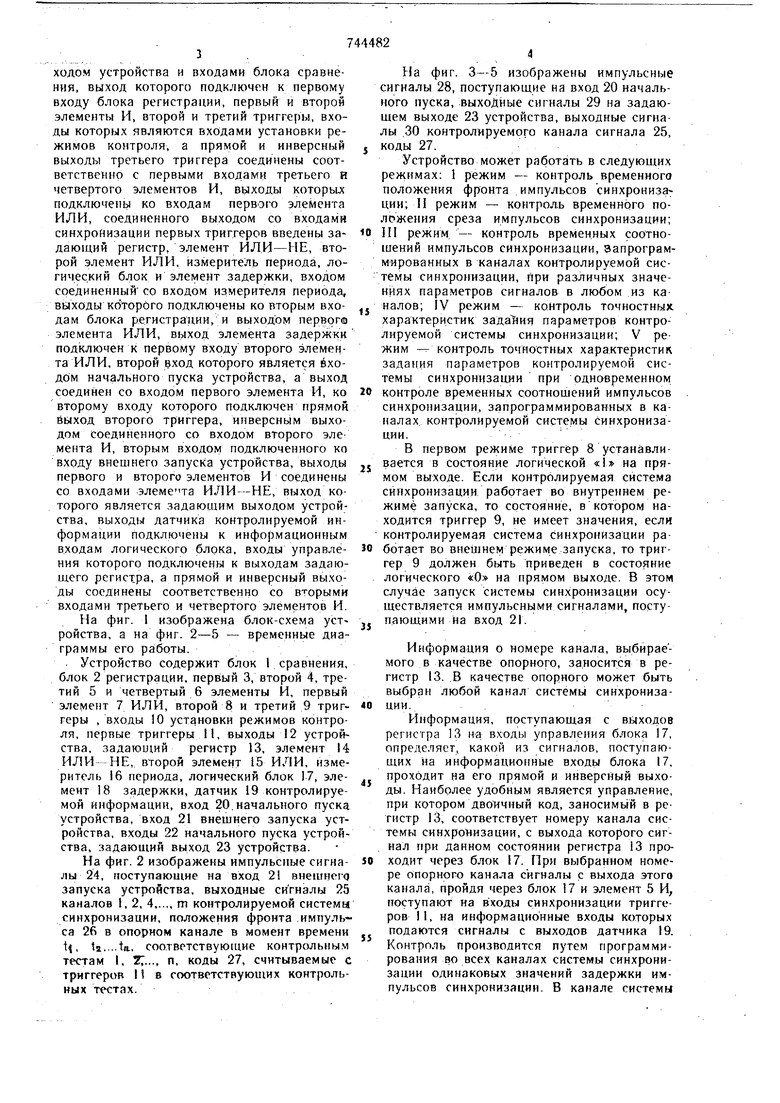

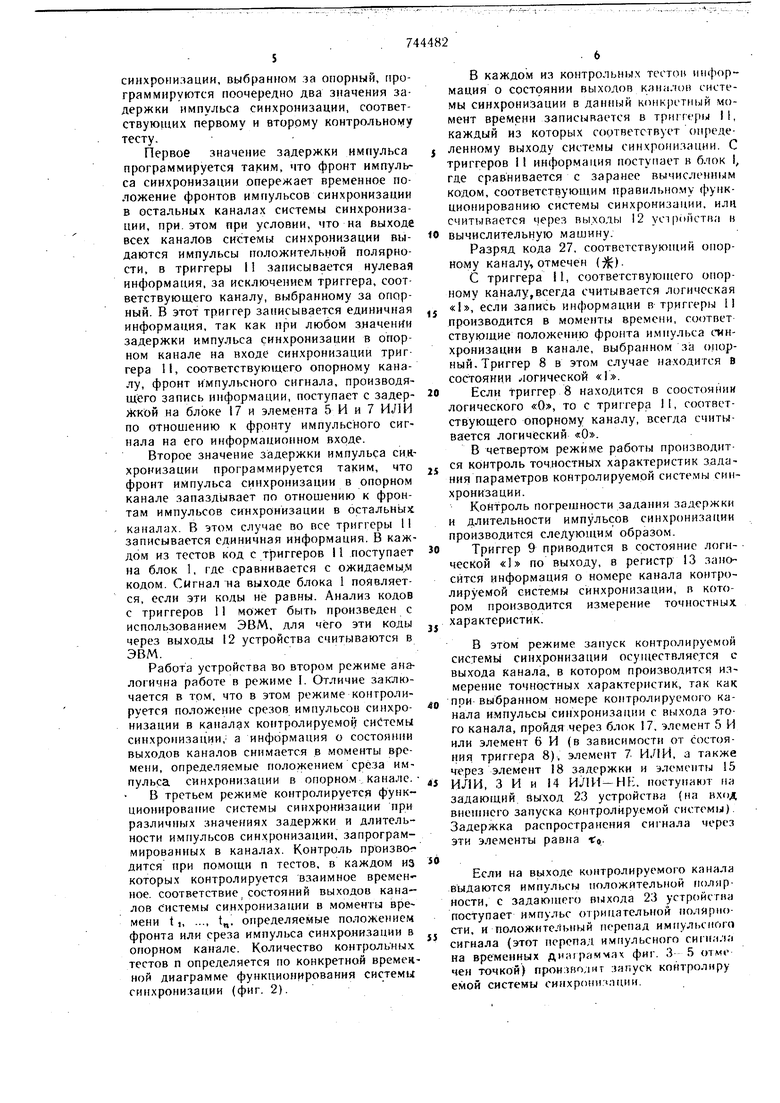

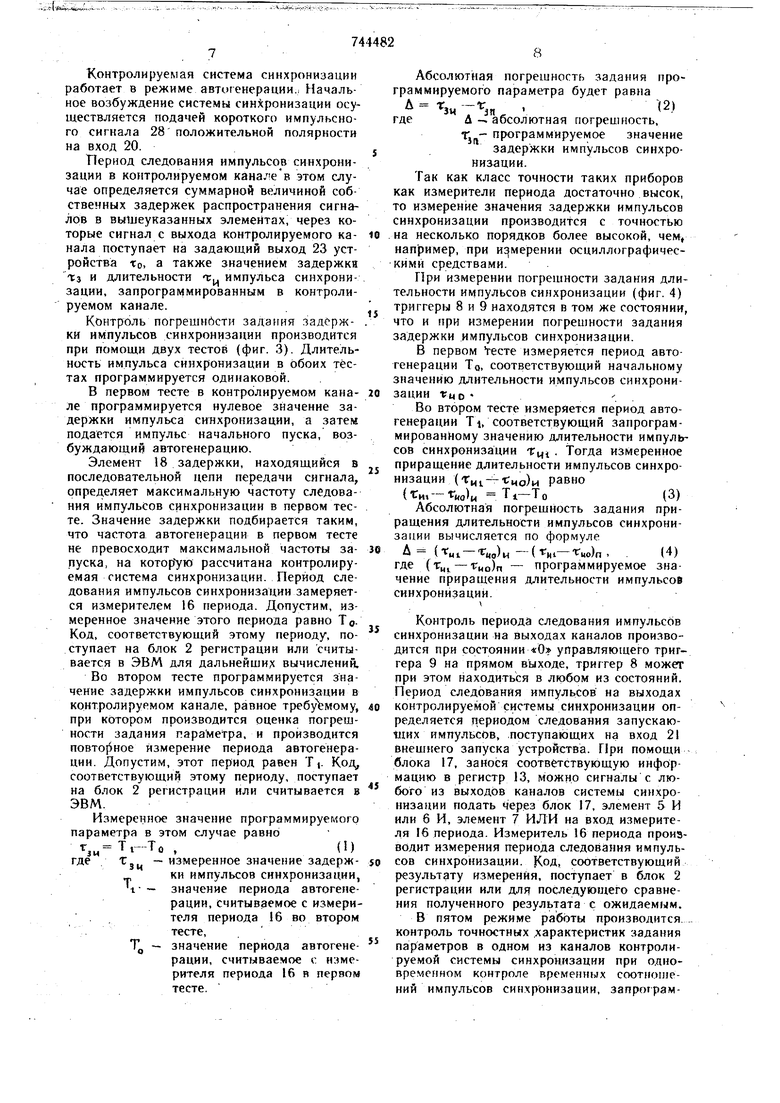

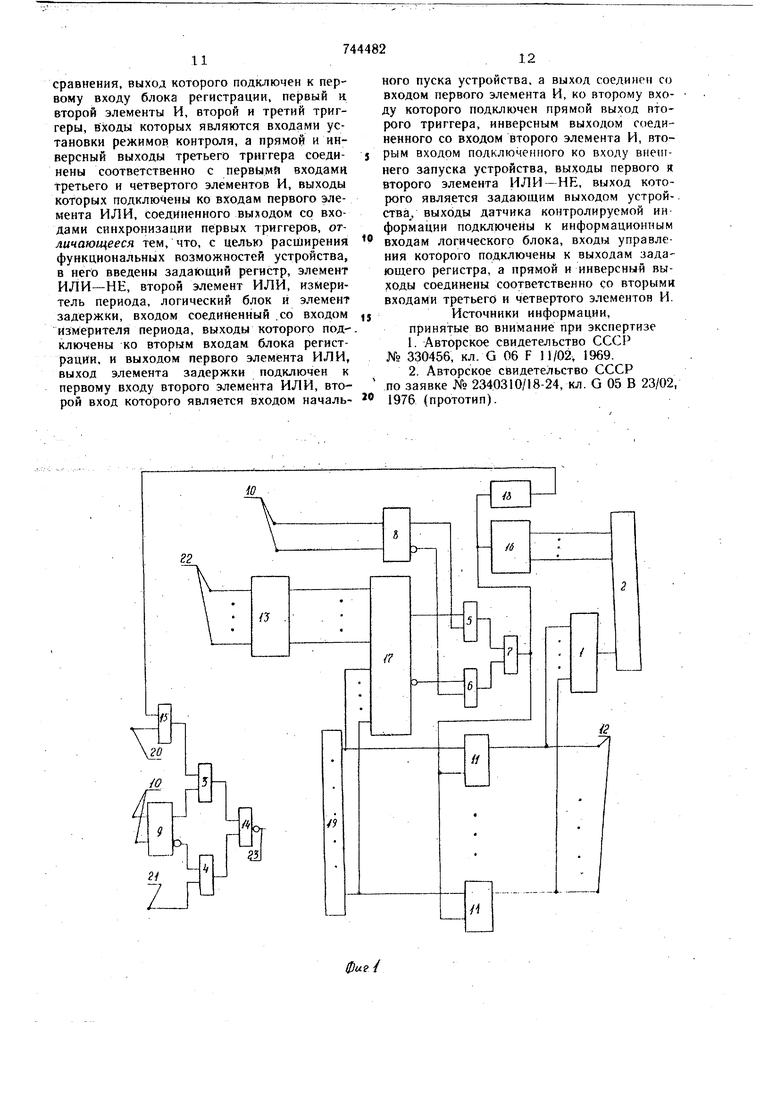

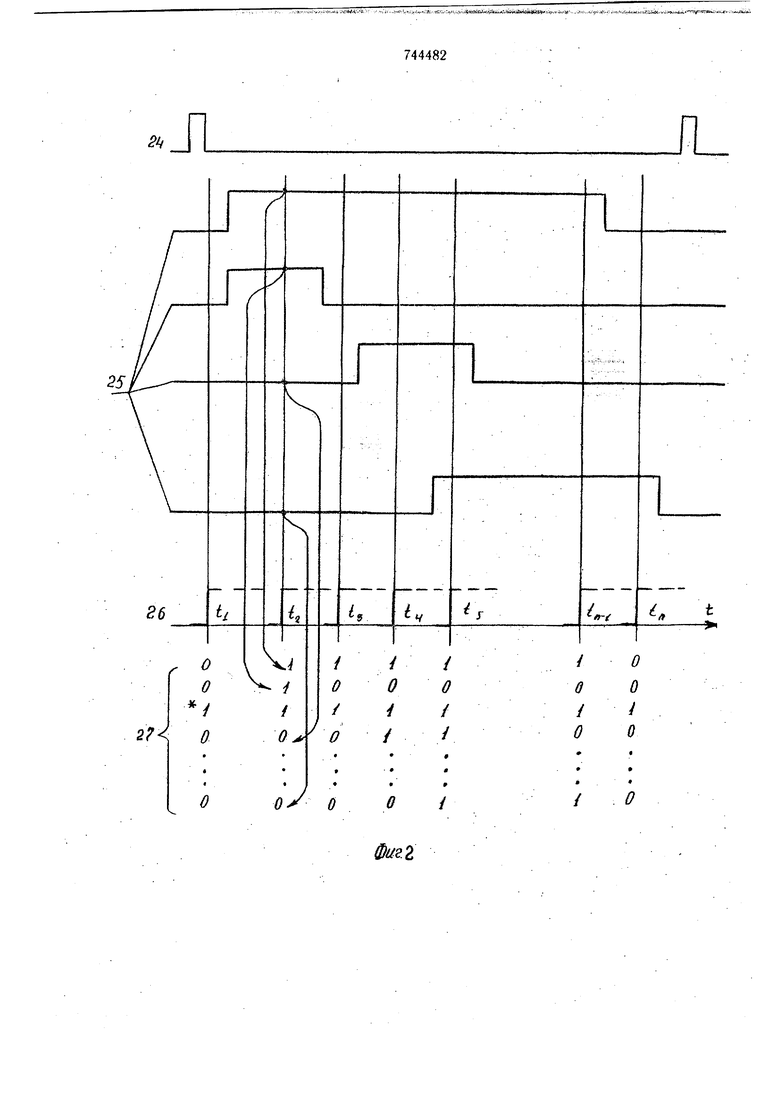

20 в устройство, содержащее датчик контролируемой информации, выходы которого подключены ко входам первых триггеров, соединенных выходами с информационным выХОДОМ устройства и входами блока сравнения, выход которого подключен к первому входу блока регистрации, первый и второй элементы И, второй и третий триггеры, входы которых являются входами установки режимов контроля, а прямой и инверсный выходы третьего триггера соединены соответственно с первыми входами третьего и четвертого элементов И, выходы которых подключены ко входам первого элемента ИЛИ, соединенного выходом со входами синхронизации первых триггеров введены задающий регистр, элемент ИДИ-ИЕ, второй элемент ИЛИ, измеритель периода, логический блок и элемент задержки, входом соединенный со входом измерителя периода, выходы которого подключены ко вторым входам блока регистрации, и выходом первого элемента ИЛИ, выход элемента задержки подключен к первому входу второго элемента ИЛИ, второй вход которого является входом начального пуска устройства, а выход соединен со входом первого элемента И, ко второму входу которого подключен прямой выход второго триггера, инверсным выходом соединенного со входом второго эле мента И, вторым входом подключенного ко входу внешнего запуска устройства, выходы первого и второго элементов И соединены со входами элеме та ИЛИ--НЕ, выход которого является задающим выходом устройства, выходы датчика контролируемой информации подключены к информационным входам логического блока, входы управления которого подключены к выходам задающего регистра, а прямой и инверсный выходы соединены соответственно со вторыми входами третьего и четвертого элементов И. На фиг. 1 изображена блок-схема устройства, а на фиг. 2-5 - временные диаграммы его работы. Устройство содержит блок 1 сравнения, блок 2 регистрации, первый 3, второй 4, третий 5 и четвертый 6 элементы И, первый элемент 7 ИЛИ, второй 8 и третий 9 триггеры , входы 10 установки режимов контроля, первые триггеры П, выходы 12 устройства, задающий регистр 13, элемент 14 ИЛИ НЕ, второй элемент {5 ИЛИ, измеритель 16 периода, логический блок 7, элемент 18 задержки, датчик 19 контролируемой информации, вход 20.начального пуска устройства, вход 2 внешнего запуска устройства, входы 22 начального пуска устройства, задающий выход 23 устройства. На фиг. 2 изображены импульсные сигналы 24, поступающие на вход 21 внешнего запуска устройства, выходные сигналы 25 каналов I, 2, 4,..., m контролируемой система синхронизации, положения фронта .импульса 26 в опорном канале в момент времени ii, ta,...ttt, соответствующие контрольным тестам I, 2Г..., п, коды 27, считываемые с триггеров 11 8 соответствуюишх контрольных тестах. На фиг. 3-5 изображены импульсные сигналы 28, поступающие на вход 20 начального пуска, выходные сигналы 29 на задающем выходе 23 устройства, выходные сигналы .30 контролируемого канала сигнала 25, коды 27. Устройство может работать в следующих режимах: 1 режим - контроль временного положения фронта импульсов синхронизации; И режим - контроль временного положения среза импульсов синхронизации; П1 режим - контроль временных соотнощений импульсов синхронизации, запрограммированных в каналах контролируемой системы синхронизации, при различных значениях параметров сигналов в любом из каналов; iV режим - контроль точностных характеристик задания параметров контролируемой системы синхронизации; V режим - контроль точностных характеристик задания параметров контролируемой системы синхронизации при одновременном контроле временных соотнощений импульсов синхронизации, запрограммированных в каналах контролируемой систе.мы синхронизации. В первом режиме триггер 8 устанавливается в состояние логической «1 на прямом выходе. Если контролируемая система синхронизации работает во внутреннем режиме запуска, то состояние, в котором находится триггер 9, не имеет значения, если контролируемая система синхронизации работает во внешнем режиме запуска, то триггер 9 должен быть приведен в состояние логического «О на прямом выходе. В этом случае запуск системы синхронизации осуществляется импульсными сигналами, поступающими на вход 21. Информация о номере канала, выбираемого в качестве опорного, заносится в регистр 13. .8 качестве опорного может быть выбран любой канал системы синхронизации.. Информация, поступающая с выходов регистра 13 на входы управления блока 17, определяет, какой из сигналов, поступающих На информационные входы блока 17, проходит на его прямой и инверсный выходы. Наиболее удобным является управление, при котором двоичный код, заносимой в регистр 13, соответствует номеру канала системы синхронизации, с выхода которого сигнал при данном состоянии регистра 13 проходит через блок 17. При выбранном номере опорного канала сигналы с выхода этого канала, пройдя через блок 17 и элемент 5 И, поступают на входы синхронизации триггеров 11, на информационные входы которых подаются сигналы с выходов датчика 19. Контроль производится путем программирования во всех каналах системы синхронизации одинаковых значений задержки импульсов синхронизации. В канале системы синхронизации, выбранном за опорный, гфограммируются поочередно два значения задержки импульса синхронизации, соответствующих первому и второму контрольному тесту. Первое значение задержки импульса программируется таким, что фронт импульса синхронизации опережает временное положение фронтов импульсов синхронизации в остальных каналах системы синхронизации, при. этом при условии, что на выходе всех каналов системы синхронизации выдаются импульсы положительной полярности, в триггеры II записывается нулевая информация, за исключением триггера, соответствующего каналу, выбранному за опорный. В этот триггер записывается единичная информация, так как при любом значении задержки импульса синхронизации в опорном канале на входе синхронизации триггера II, соответствующего опорному каналу, фронт импульсного сигнала, производящего запись информации, поступает с задержкой на блоке 17 и элемента 5 И и 7 ИЛИ по отношению к фронту импульсного сигнала на его информационном входе. Второе значение задержки импульса сидхрокизации программируется таким, что фронт импульса синхронизации в опорном канале запаздывает по отнощению к фронтам импульсов синхронизации в остальных каналах. В этом случае во все триггеры 11 записывается единичная информация. В каждом из тестов код с триггеров I1 поступает на блок 1, где сравнивается с ожидаемым кодом. Сигнал на выходе блока 1 появляется, если .эти коды не равны. Анализ кодов с триггеров 11 может быть произведен с использованием ЭВМ, для чего эти коды через выходы 12 устройства считываются в ЭВМ. Работа устройства во втором режиме аналогична работе в режиме I. Отличие заключается в том, что в этом режиме контролируется положение срезов импульсов синхронизации в каналах контролируемой системы синхронизации,: а информация о состоянии выходов каналов снимается .в моменты времени, определяемые положением среза импульса синхронизации в опорном канале. В третьем режим1е контролируется функционирование системы синхронизации при различных значениях задержки и длительности импульсов синхронизации, запрограммированных в каналах. Контроль произволдится при помощи п тестов, в каждом из которых контролируется взаимное временное, соответствие, состояний выходов каналов системы синхронизации в моменты вреt, определяемые положением мени 11, фронта или среза импульса синхро.низации в опорном канале. Количество контрольных тестов п определяется по конкретной временной диаграмме функционирования системы синхронизации (фиг. 2). В каждом из контрольных тестой информация о состоянии выходов кяналои системы синхронизации в данный конкретный момент времени записывается в триггеры II, каждый из которых соответствует определенному выходу системы синхроиилацни. С триггеров 11 информация поступает в блок I, где сравнивается с заранее вычисленным кодом, соответствующим правильному функционированию системы синхронизации, или считывается через выходы 12 устринстиа в вычислительную машину. Разряд кода 27, соответствук)П1нй опорному каналу, отмечен (). С триггера 11, соответствующего опорному каналу,всегда считывается логическая «I, если запись информации в триггеры 11 производится в моменты времени, соответ ствующие положению фронта им ульса синхронизации в канале, выбранном за опорный. Триггер 8 в этом случае находится в состоянии логической «Г. Если триггер 8 находится в соостоянин логического «О, то с тригтера 11, соответствующего опорному каналу, всегда считывается логический «О. В четвертом режиме работы производится контроль точностных характеристик задания параметров контролируемой системы синхронизации. Контроль погрешности задания задержки и длительности импульсов синхронизации производится следующим образом. Триггер 9 приводится в состояние логической «1 по выходу, в регистр 13 заносится информация о номере канала контролируемой системы синхронизации, в котором производится измерение точностных характеристик В этом режиме запуск контролируемой системы синхронизации осуществляется с выхода канала, в котором производится измерение ТОЧНО.СТНЫХ характеристик, так как при выбранном номере контролируемого канала импульсы синхронизации с выхода этого канала, пройдя через блок 17, элемент 5 И или элемент 6 И (в зависимости от состояния триггера 8), элемент 7 И.ПИ, а также ч:ерез элемент 18 задержки и элементы 15 ИЛИ, 3 И и 14 ИЛИ-НН. поступают Fia задающий выход 23 устройства (на вход внешнего запуска контролируемой системы). Задержка распространения сигнала через эти элементы равна ft. Если на выходе контролируемого канала ыдаются импульсы положительной полярости, с задающего выхода 23 устройстна поступает импульс отрицательной поляриоти. и положительный перепад импульсного игнала (этот перепад импульсного сиги,ч;|,1 а временных ди;пр;шмях фиг. 35 отмс ей точкой) произволит запуск кпнтролнру мой системы сиихрпнн:пцин. Контролируемая система синхронизации работает в режиме автогенерации,) Начальное возбуждение системы син ронизации осуществляется подачей короткого импульсного сигнала 28 положительной полярности на вход 20. Период следования импульсов синхронизации в контролируемом кана. этом случае определяется суммарной величиной собственных задержек распространения сигналов в вышеуказанных элементах, через которые сигнал с выхода контролируемого канала поступает на задающий выход 23 устройства TO, а также значением задержка гз и длительности тгц импульса синхронизации, запрограммированным в контролируемом канале. Контроль погрешнбсти задания задсржки импульсов синхронизации производится при помощи двух тестов (фиг. 3). Длительность импульса синхронизации в обоих тестах программируется одинаковой. В первом тесте в контролируемом канале программируется нулевое значение задержки импульса синхронизации, а затем подается импульс начального пуска, возбуждающий автогенерацию. Элемент 18 задержки, находящийся в последовательной цепи передачи сигнала, определяет максимальную частоту следования импульсов синхронизации в первом тесте. Значение задержки подбирается таким, что частота автогенерации в первом тесте не превосходит максимальной частоты запуска, на которую рассчитаиа контролируемая система синхронизации. Период следования импульсов синхронизации замеряется измерителем 16 периода. Допустим, измеренное значение этого периода равно Т. Код, соответствующий этому периоду, поступает на блок 2 регистрации или считывается в ЭВМ для дальнейщих вычислений. Во втором тесте программируется значение задержки импульсов синхронизации в контролируемом канале, рапное требуемому, при котором производится оценка погрешности задания параметра, и производится повто{5ное измерение периода автогенерации. Допустим, этот период равен TI. Код, соответствующий этому периоду, поступает на блок 2 регистрации или считывается в ЭВМ. Измеренное значение программируемого параметра в этом случае равно г и Тг-То,(1) где т - измеренное значение задержки импульсов синхронизации, значение периода автогенерации, считываемое с измерителя периода 16 во втором тесте, Тд - значение периода автогенерации, считываемое о измерителя периода 16 в первом тесте.

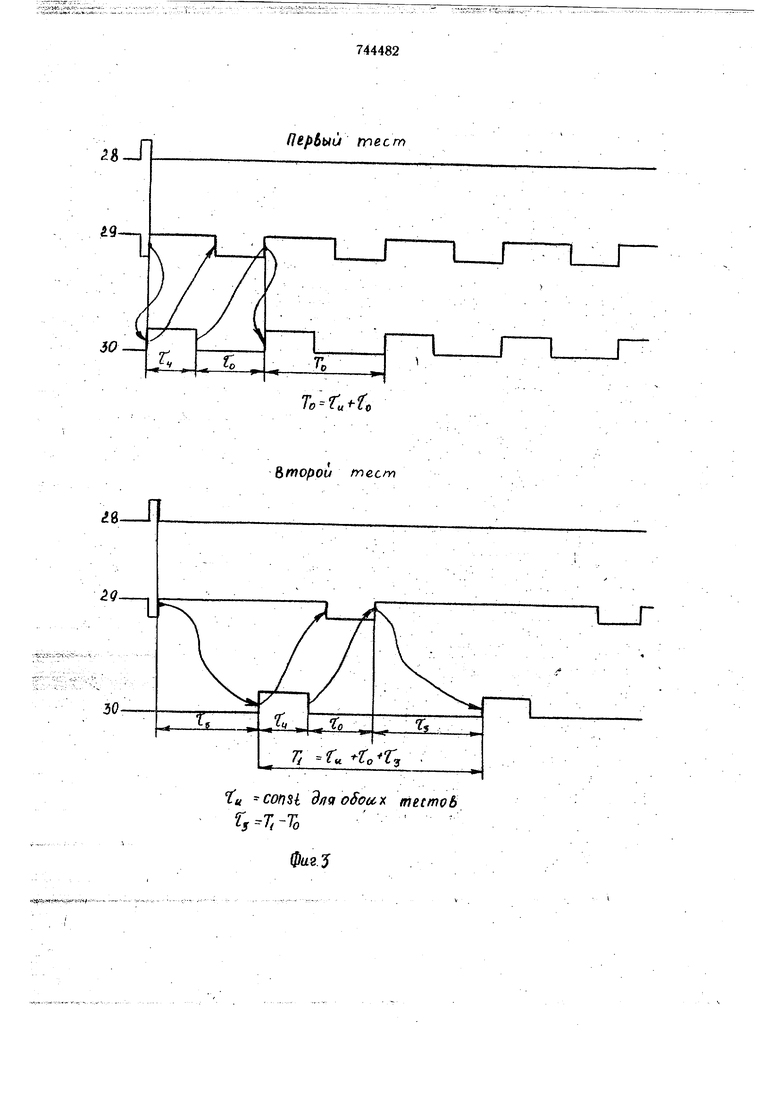

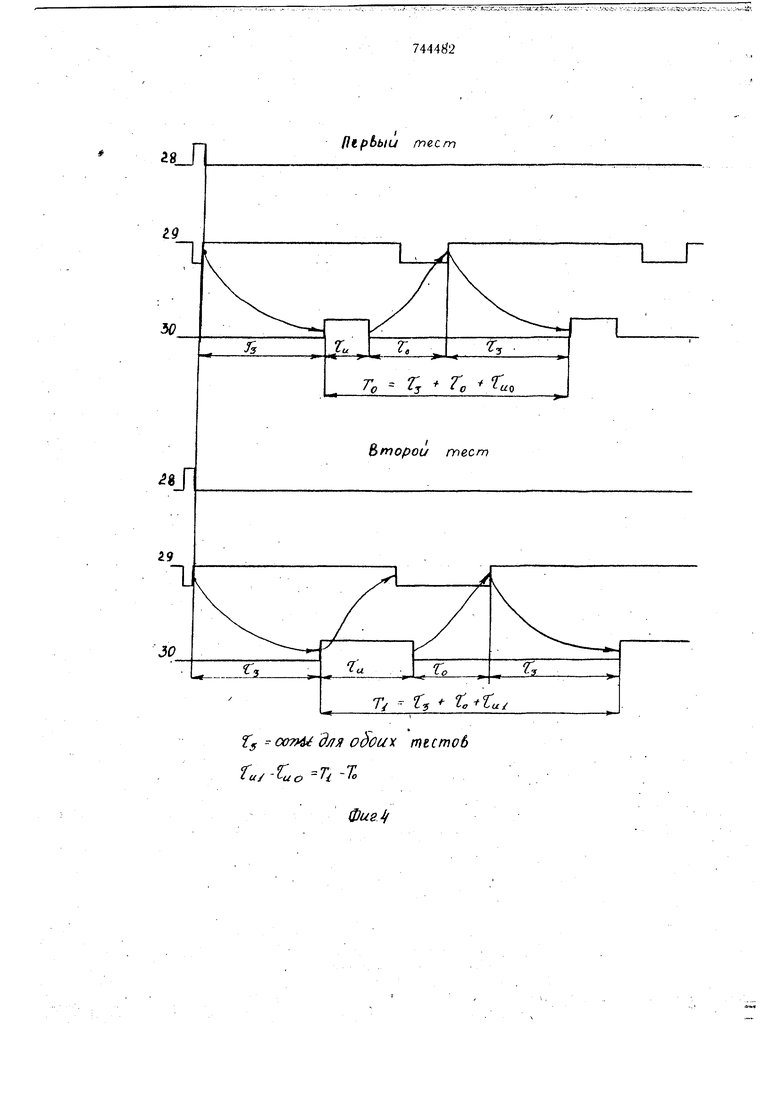

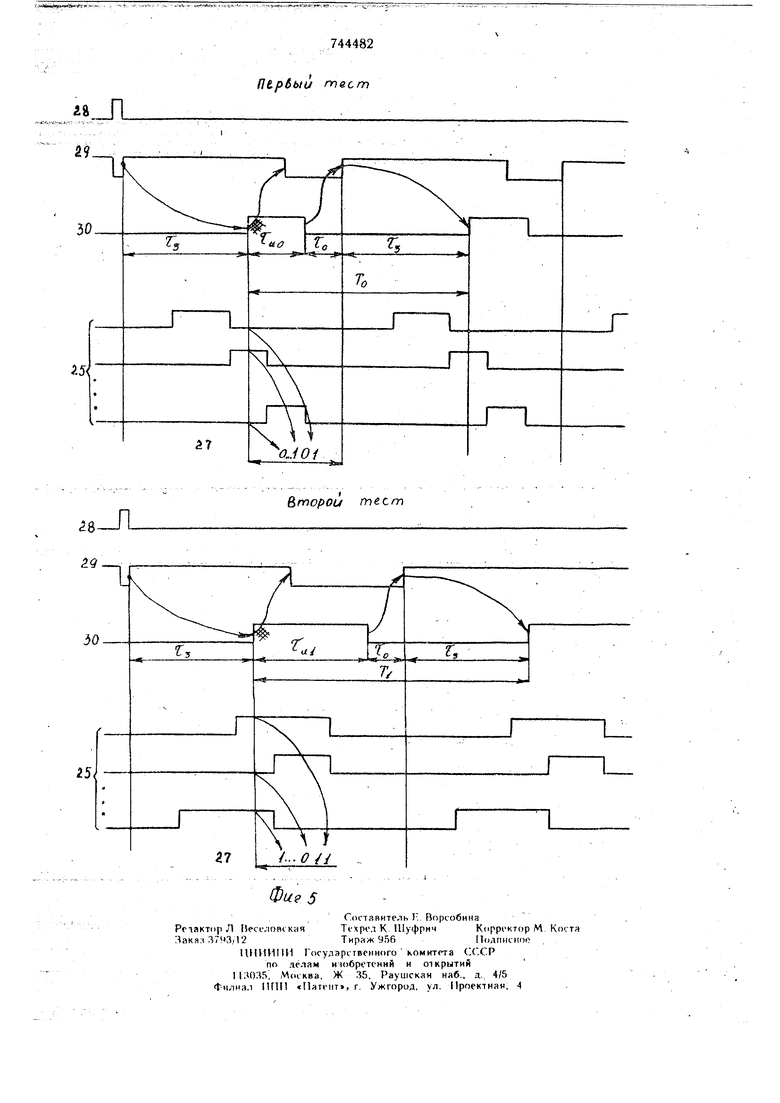

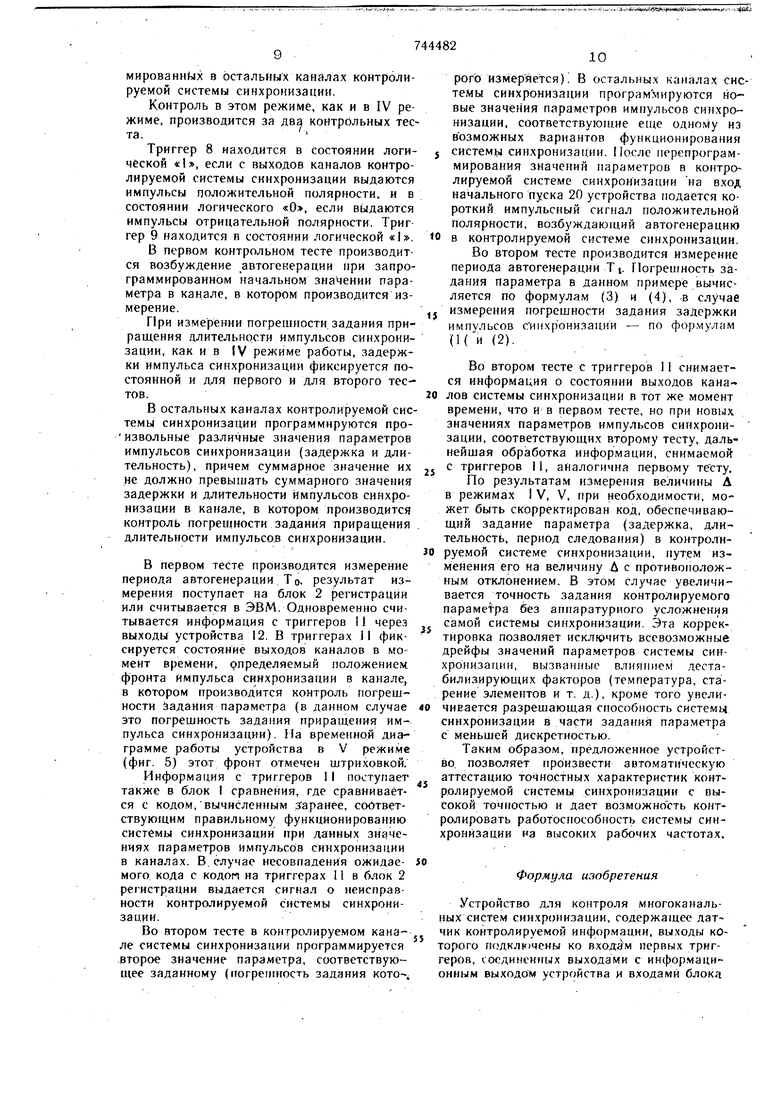

a Абсолютная погрешность задания программируемого параметра будет равна Д зя (2) гдеД -. абсолютная погрешность, Т,. программируемое значение задержки импульсов синхронизации. Так как класс точности таких приборов как измерители периода достаточно высок, то измерение значения задержки импульсов синхронизации пpoизвoдиtcя с точностью на несколько порядков более высокой, чем, например, при измерении осциллографическимй средствами. При измерении погрешности задания длительности импульсов синхронизации (фиг. 4) триггеры 8 и 9 находятся в том же состоянии, что и при измерении погрешности задания задержки импульсов синхронизации. В первом VecTe измеряется период автогенерации То, соответствующий начальному значению длительности импульсов синхронизации VUD Во втором тесте измеряется период автогенерации Т1, соответствующий запрограммированному значению длительности импульсов сиихронизации Тц . Тогда измеренное приращение длительности импульсов синхронизации (Ти1--тГцо)ц равно (TMI-t uo u TI-TO(3) Абсолютная погрещность задания приращения длительности импульсов синхронизации вычисляется по формуле А (Н1 -Ои - ()п- . (4) где (т„1 - 1г„о)п - программируемое значение приращения длительности импульсоо синхронизации. VКонтроль периода следования импульсов синхронизации на выходах каналов производится при состоянии «О управляющего триггера 9 на прямом выходе, триггер 8 может при этом находиться в любом из состояний. Период следования импульсов на выходах контролируемой системы синхронизации определяется периодом следования запускающих импульсов, поступающих на вход 21 внешнего запуска устройства. При помощи блока 17, занося соответствующую информацию в регистр 13, можно сигналы с любого из выходов каналов системы синхронизации подать через блок 17, элемент 5 И или б И, элемент 7 ИЛИ на вход измерителя Г6 периода. Измеритель 16 периода производит измерения периода следования импульсов синхронизации. Код, соответствующий результату измерения, поступает в блок 2 регистрации или для последую дего сравнения полученного результата с ожидаемым. В пятом режиме работы производится, контроль точностных характеристик задания параметров в одном из каналов контролируемой системы синхронизации при одновременном контроле временных соотношений импульсов синхронизации, запрограммированн(х в остальных канйлах контролируемой системы синхроршзации. Контроль в этом режиме, как и в IV режиме, производится за два контрольных тес та. Триггер 8 находится в состоянии логической «1, если с выходов каналов контролируемой системы синхронизации выдаются импульсы положительной полярности, и в состоянии логического «0, если выдаются импульсы отрицательной полярности. Триг гер 9 находится в состоянии логической «1. В первом контрольном тесте производится возбуждение автогекерации при запрограммированном начальном значении параметра в канале, в котором производится измерение. При измерении погрешности задания приращения длительности импульсов синхронизации, как ив IV режиме работы, задержки импульса синхронизации фиксируется постоянной и для первого и для второго тестов. В остальных каналах контролируемой сис темы синхронизации программируются произвольные различные значения параметров импульсов синхронизации (задержка и длительность), причем суммарное значение их не должно превышать суммарного значения задержки и длительности импульсов синхронизации в канале, в котором производится контроль погрешности задания приращения длительности импульсов синхронизации. В первом тесте производится измерение периода автогенеряции То, результат измерения поступает на блок 2 регистрации или считывается в ЭВМ. Одновременно считывается информация с триггеров 11 чере.э выходы устройства 12. В триггерах 11 фиксируется состояние выходов каналов в момент времени, рпределяемый положением фронта импульса синхронизации в канале, в котором производится контроль погрешности Задания параметра (в данном случае это погрешность задания приращения импульса синхронизации). На временной диаграмме работы устройства в V режиме (фиг. 5) этот фронт отмечен штриховкой. Информация с триггеров И поступает также в блок I сравнения, где сравнивается с кодом,вычисленным заранее, соответствующим правильному функционированию системы синхронизации при данных значениях параметров импульсов синхронизации в каналах. В, случае несовпадения ожидаемого кода с кодом на триггерах 11 в блок 2 регистрации выдается сигнал о неисправности контратируемой системы синхронизации. Во втором тесте в контролируемом канале системы синхронизации программируется второе значение параметра, соответствующее заданному (погрешность задания которого измеряется) В остальных каналах системы синхронизации программируются новые значения параметров импульсов синхронизации, соответствующие еще одному из возможных вариантов функционирования системы синхронизации. После перепрограммирования значений параметров в контролируемой системе синхронизации на вход начального пуска 20 устройства подается короткий импульсный сигнал положительной полярности, возбуждающий автогенерацию в контролируемой системе синхронизации. Во втором тесте производится измерение периода автогенерации ТI. Погрецгность задания параметра в данном примере вычисляется по формулам (3) и (4), в случае измерения погрешности задания задержки импульсов синхронизации - по формулам (К и (2). Во втором тесте с триггеров 11 снимается информация о состоянии выходов каналов системы синхронизации в тот же момент времени, что ив первом тесте, но при новых значениях параметров импульсов синхронизации, соответствующих второму тесту, дальнейшая обработка информации, снимаемой с триггеров II, аналогична первому тесту. По результатам измерения величины Л в режимах I V, V, при необходимости, может быть скорректирован код, обеспечивающий задание параметра (задержка, длительность, период cлeдoвaF ия) в контролируемой системе синхронизации, путем иЗ меиения его на величину Д с противоположным отклонением., В этом случае увеличивается точность задания контролируемого параметра без аппаратурного усложнения самой системы синхронизации. Эта корректировка позволяет исключить всевозможные дрейфы значений параметров системы синхронизации, вызванные влиянием дестабилизирующих факторов (температура, старение элементов и т. д.), кроме того увеличивается разрешающая способность системы синхронизации в части задания параметра с меньшей дискретностью. Таким образом, предложенное устройство, позволяет прбизвести авто.матнческую аттестацию точностных характеристик контролируемой системы синхронизации с высокой точностью и дает возможность контролировать работоспособность системы синхронизации на высоких рабочих частотах. Формула изобретения Устройство для контроля многоканальных систем синхронизации, содержащее датчик контролируемой информации, выходы кОорого подключены ко входам первых тригеров, сосдиясиных выходами с информаци-нным выходом устройства и входами блока

сравнения, выход которого подключен к первому входу блока регистрации, первый и второй элементы И, второй и третий триггеры, входы которых являются входами установки режимов контроля, а прямой и инверсный выходы третьего триггера соединены соответственно с первыми входами третьего и четвертого элементов И, выходы которых подключены ко входам первого элемента ИЛИ, соединенного выходом со входами синхронизации первых триггеров, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены задающий регистр, элемент ИЛИ-НЕ, второй элемент ИЛИ, измеритель периода, логический блок и элемент задержки, входом соединенный .со входом измерителя периода, выходы которого поД ключены ко вторым входам блока регистрации, и выходом первого элемента ИЛИ, выход элемента задержки подключен к первому входу второго элемента ИЛИ, второй вход которого является входом начального пуска устройства, а выход соединен со входом первого элемента И, ко второму входу которого подключен прямой выход второго триггера, инверсным выходом соединенного со входом второго элемента И, вторым входом подключемгюго ко входу внешнего запуска устройства, выходы первого и второго элемента ИЛИ-НЕ, выход которого является задающим выходом устрой-. ства, выходы датчика контролируемой ин формации подключены к информационным

входам логического блока, входы управления которого подключены к выходам задающего регистра, а прямой и инверсный выходы соединены соответственно со вторыми входами третьего и четвертого элементов И.

Источники информации, принятые во внимание при экспертизе

по заявке № 2340310/18-24, кл. G 05 В 23/02, 1976 (прототип).

Л

a

To rriecm

Г, Г« ГоГг

и -consi для met mob

Т -Т

I-S -1{ to

Фиг.З (llpbbiu

Второй тест тест

Ту сс7 для те.сто6

t и/ °

Фие1{

744482

ntp6bnj nnecm

«л

Авторы

Даты

1980-06-30—Публикация

1978-03-20—Подача