Os

О СП СО 00

Изобретение относится к вычислительной технике и может быть использовано в конвейерных процессорах электронных вычислительных машин.

Целью изобретения является повышение быстродействия устройства.

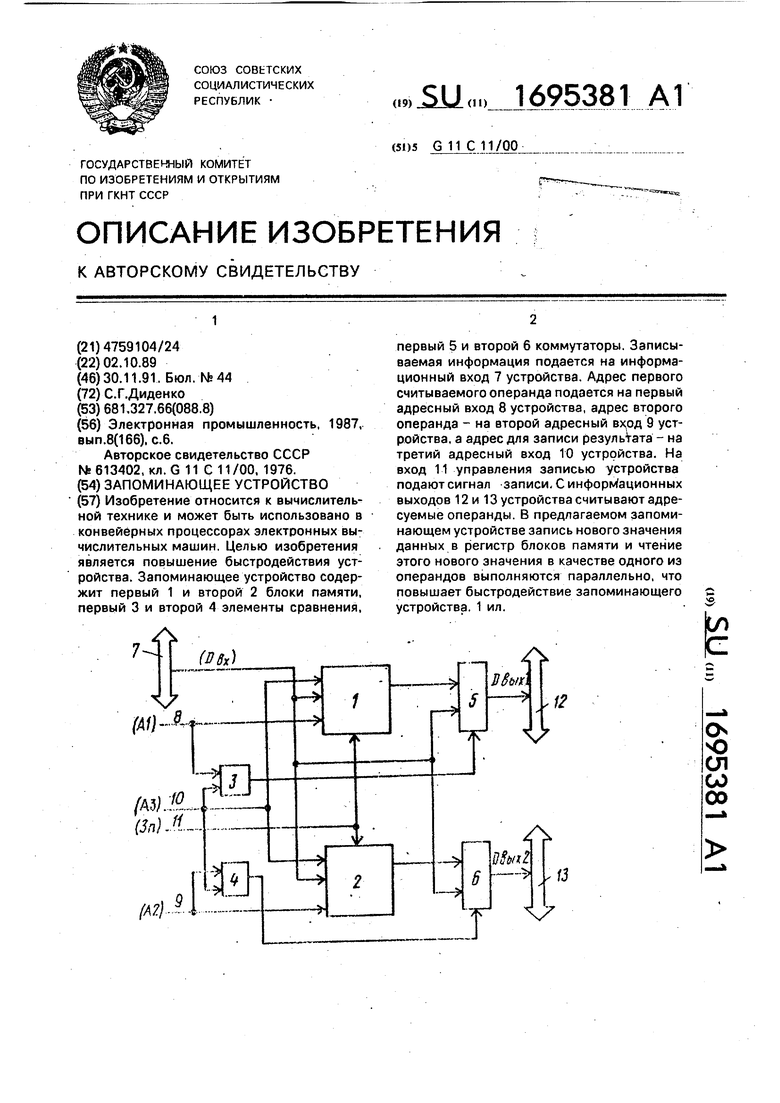

На чертеже приведена схема предлагаемого запоминающего устройства.

Запоминающее устройство содержит первый 1 и второй 2 блоки памяти, первый 3 и второй 4 элементы сравнения, первый 5 и второй 6 коммутаторы. Информационный вход 7 устройства соединен с информационными входами блоков 1 и 2 памяти и вторыми информационными входами первого и второго коммутаторов 5 и 6. Первый адресный вход 8 устройства соединен с первым входом элемента 3 сравнения и входом адреса чтения первого блока 1 памяти. Второй адресный вход 9 устройства соединен с первым входом элемента А сравнения и входом- адреса чтения второго блока 2 памяти. Третий адресный вход 10 устройства соединен с входами адреса записи блоков 1 и 2 памяти и вторыми входами элементов 3 и 4 сравнения. Сигнал записи подают на вход 11 Управления записью устройства. Выходы блоков 1 и 2 памяти подключены соответственно к первым входам-первого 5 и второго б коммутаторов, выходы которых являются соответственно первым 12 и вторым 13 информационными выходами устройства.

Запоминающее, устройство работает следующим образом.

Для выполнения конвейерной обработки данных необходимо во время каждого такта его работы извлечь из запоминающе- to устройства два операнда для текущей операции и записать в него результат обработки по предыдущей операции. Для этого На адресный вход 8 устройства подают адрес А1 чтения первого операнда, на адресный вход 9 - адрес А2 чтения второго операнда, а на адресный вход 10 - адрес A3 записи результата предыдуа1ей операции, Записываемая информация DBx поступает в устройство через информационный вход 7. Первый операнд Оьых.1 выводится через первый информационный выход 12 устройства, а второй операнд 0Вых.2 -через второй информационный выход 13 устройства. Запись информации происходит одновременно в блоках 1 и 2 памяти в регистры с одинаковым адресом по сш налу записи, поступающему на вход 11 управления записью устройства. Одновременно в операционном 5локе процессора (не показан) фиксируют считанные с выходов 12 и 13 запоминающе- о устройства значения операндов, устанав- чивают новые значения адресов А1 и А2

операндов, а операционный блок начинает вырабатывать на основе считанных операндов новый результат, который поступает на информационный вход 7 устройства и записывается в следующем такте. По окончании сигналу записи происходит установка нового значения адреса A3.

Если адрес записи A3 не совпадает ки с одним из адресов операндов А1 и А2, то

0 сигналы с выхода элементов 3 и 4 сравнения поступают на управляющие входы коммутаторов 5 и 6 и подключают выходы коммутаторов к их первым входам.

Если адрес записи A3 совпадает с од5 ним из адресов чтения, например адресом А1, то на выходе элемента 3 сравнения появляется сигнал, переключающий коммутатор 5 на прием информации с второго информационного входа. При этом макси0 мальная задержка выдачи первого операнда Овых.1 мала и равна сумме задержек элемента 3 сравнения и коммутатора 5. Поэтому первый операнд появляется на информационном выходе запоминающего

5 устройства одновременно с вторым.

Таким образом, в предлагаемом запоминающем устройстве запись нового значения данных в регистр блоков памяти и чтение этого нового значения в качестве

0 одного из операндов выполняются параллельно и одновременно, что.повышает быстродействие запоминающего устройства. Формула изобретения Запоминающее устройство, содержа5 щее первый и второй блоки памяти, информационные входы которых объединены и являются информационным входом устройства, и первый коммутатор, отличающееся тем, что, с целью повышения быстро0 действия устройства, в него введены первый и второй элементы сравнения и втррой коммутатор, причем вход адреса чтения первого блока памяти объединен с первым входом первого элемента сравнения и явля5 ется первым адресным входом устройства, вход адреса чтения второго блока памяти объединен с первым входом второго элемента сравнения и является вторым адрес- ным входом устройства, второй вход

0 первого элемента сравнения объединен с вторым входом второго элемента сравнения и входами адреса записи первого и второго блоков памяти и является третьим адресным входом устройства, выход первого

5 блока памяти подключен к первому информационному входу первого коммутатора, выход второго блока памяти - к первому информационному входу второго коммутатора, вторые информационные входы первого и второго коммутаторов объеди516953816

йены и подключены к информационному- онным выходом устройства, выход второго входу устройства, управляющий вход перво-, коммутатора - вторым информационным

го коммутатора подключен к выходу первоговыходом устройства, вход управления за- элемента сравнения, управляющий вход писью первого блока памяти объединен с второго коммутатора подключен к выходу 5 входом управления записью второго блока

второго элемента сравнения, выход первогопамяти и является входом управления закоммутатора является первым информаци-писью устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1988 |

|

SU1644224A1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Запоминающее устройство | 1976 |

|

SU613402A1 |

| Устройство для согласования потоков телеметрических отсчетов | 1987 |

|

SU1543561A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1988 |

|

SU1840538A1 |

| Устройство управления памятью | 1980 |

|

SU947866A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

Изобретение относится к вычислительной технике и может быть использовано в конвейерных процессорах электронных вычислительных машин. Целью изобретения является повышение быстродействия устройства. Запоминающее устройство содержит первый 1 и второй 2 блоки памяти, первый 3 и второй 4 элементы сравнения, / первый 5 и второй 6 коммутаторы. Записываемая информация подается на информационный вход 7 устройства. Адрес первого считываемого операнда подается на первый адресный вход 8 устройства, адрес второго операнда - на второй адресный вход 9 устройства, а адрес для записи результата - на третий адресный вход 10 устройства. На вход 11 управления записью устройства подают сигнал записи, С информационных выходов 12 и 13 устройства считывают адресуемые операнды. В предлагаемом запоминающем устройстве запись нового значения данных в регистр блоков памяти и чтение этого нового значения в качестве одного из операндов выполняются параллельно, что повышает быстродействие запоминающего устройства. 1 ил. Ё

| Электронная промышленность, 1987, вы п.8(166), с | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Запоминающее устройство | 1976 |

|

SU613402A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-11-30—Публикация

1989-10-02—Подача