Устройство относится к области передачи дискретной информации с применением методов кодирования и может быть использовано в телемеханике и вычислительной технике.

Известны устройства для преобразования разрядности двоичных кодов.

Предложенное устройство для преобразования п-значного двоичного кода в р-значный двоичный код содержит блок считывания информации с перфолент, преобразователь параллельного кода в последовательный, сдвигающий регистр, переключатели разрядности, выходное устройство и отличается тем, что выходы блока считывания информации с перфолент соединены со входами преобразователя параллельного кода в последовательный, выход которого соединен со входом сдвигающего регистра. Поразрядные выходы последнего соединены с выходным устройством, выход последнего (р-1) разряда соединен со входом схемы управления и переключателем разрядности /7-кода, а переключатель разрядности п-кода - с преобразователем параллельного кода в последовательный.

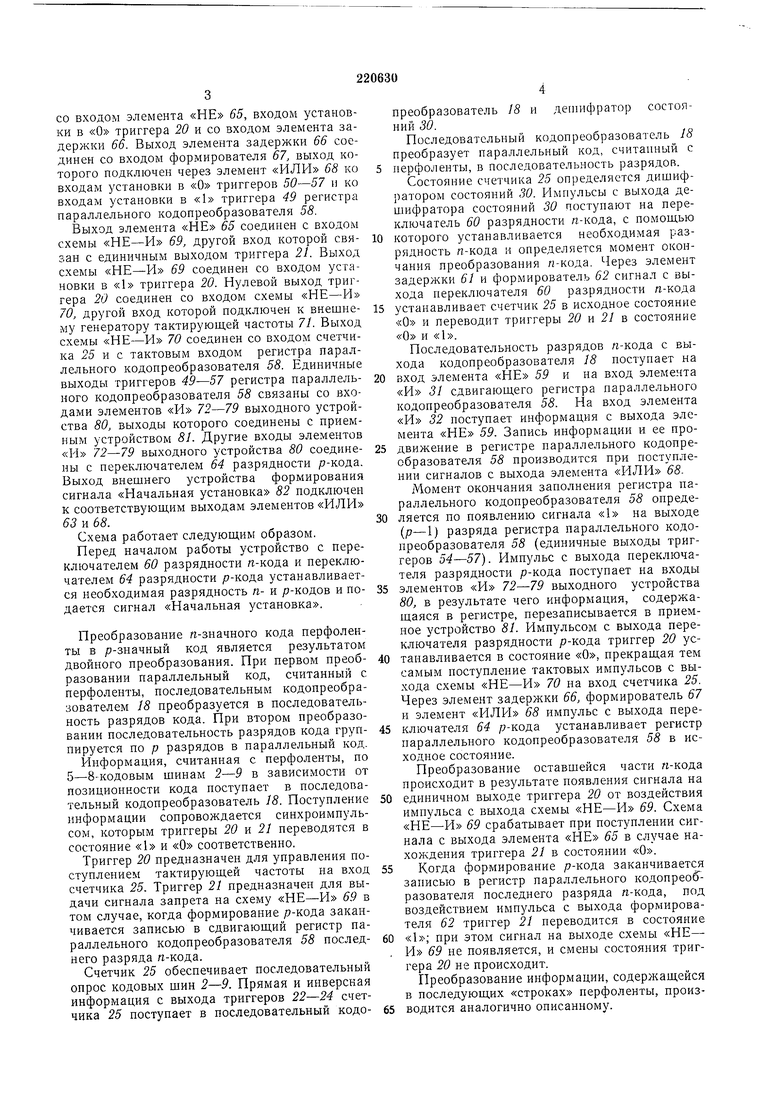

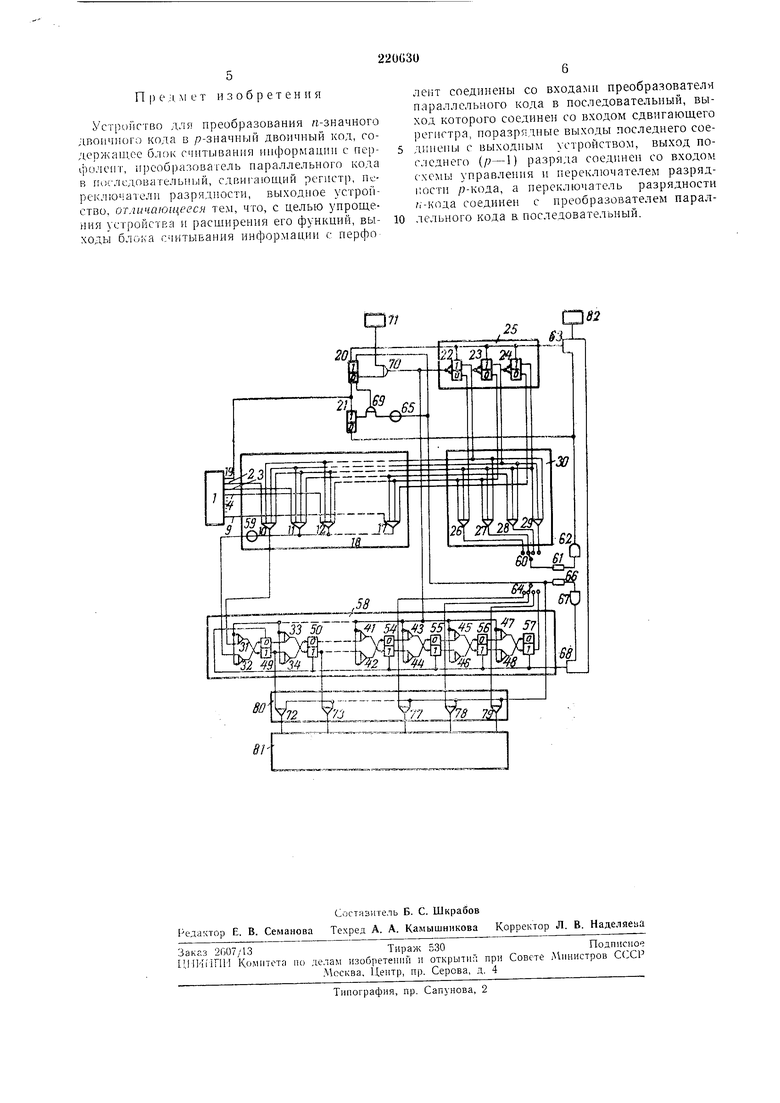

На чертеже приведена функциональная схема устройства прямого и обратного преобразования 5-8-зиачных двоичных кодов.

Считыватель 1 с перфоленты посредством кодовых шин 2-9 соединен со входами элементов «PI 10-17 последовательного кодопреобразователя 18, а шиной 19 синхронизации- со входом установки в «1 триггера 20 и входом установки в «О триггера 21 соответственно. Выходы триггеров 22-24 счетчика 25 подключаются к другим входам элементов «И 10-17 и ко входам элементов «И 26-29 дешифратора состояний 30. Элементы «И 31- 48 и триггеры 49-57 соединены между собой

таким образом, что образуют сдвигающий регистр параллельиого кодопреобразователя 58. Выходы элементов «И 10-17 последовательного кодопреобразователя 18 объединены и подключаются ко входу элемента «НЕ 5.9 и

ко входу элемента «И 31. Выход элемента «НЕ 55 соединен со входом элемента «Н 32. Выходы элементов «И 26-29 дешифратора состояний 30 соединены со входами переключателя 60 разрядности п-кода, выход которого

через элемент задержки 61, формирователь 62 и элемент «ПЛИ 63 соединен с шиной сброса на «О триггеров 20, 22, 23 и 24 и со входом установки в «1 триггера 21. Выходы триггеров 54-57 подключены к переключателю 64

со входом элемента «НЕ 65, входом установки в «О триггера 20 и со входом элемента задержки 66. Выход элемента задержки 66 соединен со входом формирователя 67, выход которого подключен через элемент «ИЛИ 68 ко входам установки в «О триггеров 50-57 и ко входам установки в «1 триггера 49 регистра параллельного кодопреобразователя 58.

Выход элемента «НЕ 65 соединен с входом схемы «НЕ-И 69, другой вход которой связан с единичным выходом триггера 21. Выход схемы «НЕ-И 69 соединен со входом установки в «1 триггера 20. Нулевой выход триггера 20 соединен со входом схемы «НЕ-И 70, другой вход которой подключен к внешнему генератору тактирующей частоты 7/. Выход схемы «НЕ-И 70 соединен со входом счетчика 25 и с тактовым входом регистра параллельного кодопреобразователя 58. Единичные выходы триггеров 49-57 регистра параллельного кодопреобразователя 58 связаны со входами элементов «И 72-79 выходного устройства 80, выходы которого соединены с приемным устройством 81. Другие входы элементов «И 72-79 выходного устройства 80 соединены с переключателем 64 разрядности р-кода. Выход внешнего устройства формирования сигнала «Начальная установка 82 подключен к соответствуюш,им выходам элементов «ИЛИ 63 и 68.

Схема работает следующим образом.

Перед началом работы устройство с переключателем 60 разрядности п-кода и переключателем 64 разрядности /5-кода устанавливается необходимая разрядность п- и р-кодов и подается сигнал «Начальная установка.

Преобразование п-значного кода перфоленты в / -значный код является результатом двойного преобразования. При первом преобразовании параллельный код, считанный с перфоленты, последовательным кодопреобразователем 18 преобразуется в последовательность разрядов кода. При втором преобразовании последовательность разрядов кода группируется по р разрядов в параллельный код.

Информация, считанная с перфоленты, по 5-8-кодовым шпнам 2-9 в зависимости от позиционности кода поступает в последовательный кодопреобразователь 18. Поступление информации сопровождается синхроимпульсом, которым триггеры 20 и 21 переводятся в состояние «1 и «О соответственно.

Триггер 20 предназначен для управления поступлением тактирующей частоты на вход счетчика 25. Триггер 21 предназначен для выдачи сигнала запрета на схему «НЕ-И 69 в том случае, когда формирование / -кода заканчивается записью в сдвигающий регистр параллельного кодопреобразователя 55 последнего разряда п-кода.

преобразователь 18 и депшфратор состояний 30.

Последовательный кодопреобразователь 18 преобразует параллельный код, считанный с перфоленты, в последовательность разрядов.

Состояние счетчика 25 определяется дишифратором состояний 30. Импульсы с выхода дешифратора состояний 30 поступают на переключатель 60 разрядности п-кода, с помощью

которого устанавливается необходимая разрядность п-кода и определяется момент окончания преобразования п-кода. Через элемент задержки 61 и формирователь 62 сигнал с выхода переключателя 60 разрядности п-кода

устанавливает счетчик 25 в исходное состояние «О и переводит триггеры 20 и 27 в состояние «О и «1.

Последовательность разрядов п-кода с выхода кодопреобразователя 18 поступает на

вход элемента «НЕ 59 и на вход элемента «И 31 сдвигающего регистра параллельного кодопреобразователя 58. На вход элемента «И 32 поступает информация с выхода элемента «НЕ 59. Запись информации и ее продвижение в регистре параллельного кодопреобразователя 58 производится при поступлении сигналов с выхода элемента «ИЛИ 68.

Момент окончания заполнения регистра параллельного кодопреобразователя 58 определяется по появлению сигнала «1 на выходе (р-1) разряда регистра параллельного кодопреобразователя 58 (единичные выходы триггеров 54-57). Импульс с выхода переключателя разрядности р-кода поступает на входы

элементов «И 72-79 выходного устройства 80, в результате чего информация, содержащаяся в регистре, перезаписывается в приемное устройство 81. Импульсом с выхода переключателя разрядности р-кода триггер 20 устанавливается в состояние «О, прекращая тем самым поступление тактовых импульсов с выхода схемы «НЕ-И 70 на вход счетчика 25. Через элемент задержки 66, формирователь 67 и элемент «ИЛИ 68 импульс с выхода переключателя 64 р-кода устанавливает регистр параллельного кодопреобразователя 58 в исходное состояние.

Преобразование оставшейся части п-кода происходит в результате появления сигнала на

единичном выходе триггера 20 от воздействия импульса с выхода схемы «НЕ-И 69. Схема «НЕ-И 69 срабатывает при поступлении сигнала с выхода элемента «НЕ 65 в случае нахождения триггера 21 в состоянии «О.

Когда формироваиие р-кода заканчивается записью в регистр параллельного кодопреобразователя последнего разряда п-кода, под воздействием импульса с выхода формирователя 62 триггер 21 переводится в состояние

при этом сигнал на выходе схемы «НЕ- И 69 не появляется, и смены состояния триггера 20 не происходит.

П |) е ,;i, мет изобретения

Устройство для преобразования а-значного двоичного кода в /7-значный двоичный код, содержащее блок считывания информации с перфолент, нреобразовагель параллельного кода в Последовательный, сдвигаюн 1,нй регист|), переключа1ел11 разряд1шсти, выходное уетропство, отличающееся тем, что, с целью упрощения устройства и расширения его функций, выходы блока считывания информации с перфо

лент соединены со входами преобразователя нараллельного кода в последовательный, выход которого соединен со входом сдвигающего регистра, иоразр5:диые выходы последнего соединены с выходным устройством, выход последнего (/;-1) разряда соединен со входом схемы управления и нереключателем разрядиостн /;-кода, а переключатель разрядности -кода соединен с преобразователем параллельного кода в последовательный.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь @ -значного двоичного кода в @ -значный | 1983 |

|

SU1156057A1 |

| Преобразователь @ -значного двоичного кода в @ -значный код | 1983 |

|

SU1087982A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Устройство для преобразования кодов в системе передачи данных | 1982 |

|

SU1086449A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь @ -значного двоичного кода в @ -значный | 1985 |

|

SU1256210A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

Даты

1968-01-01—Публикация