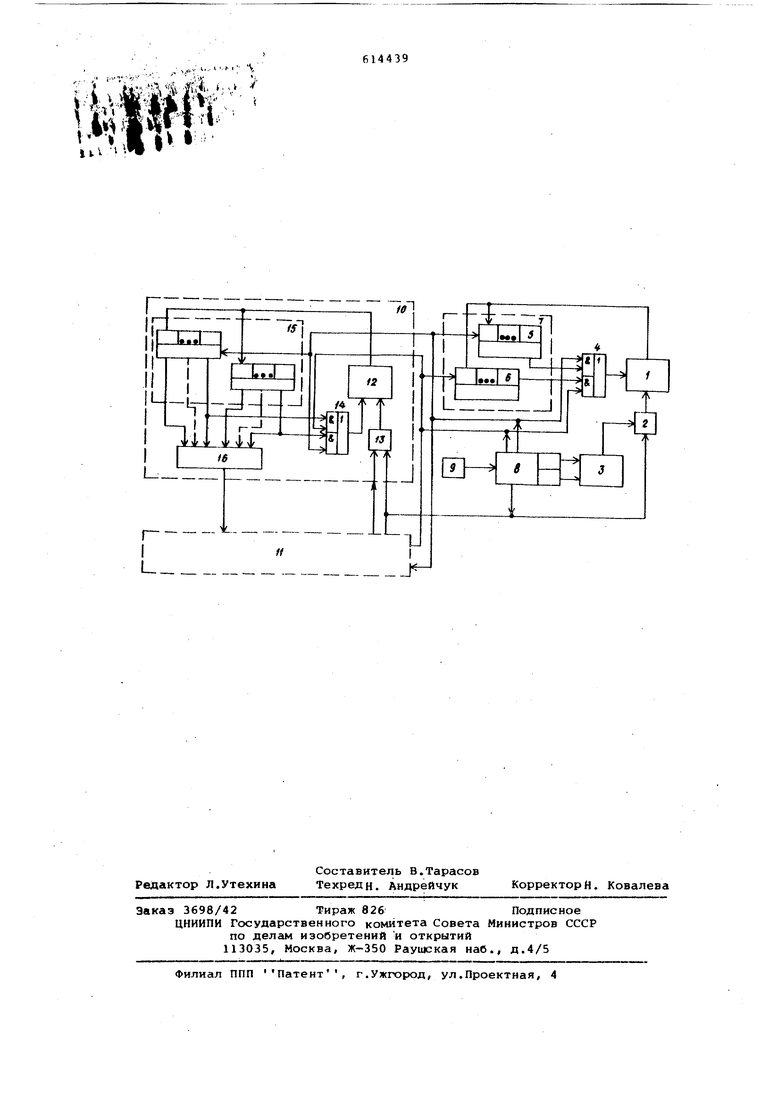

Изобретение относится к области вычислительной техники и используется как арифметическое устройство для решения функциональных зависимостей, которые возникают при повороте прямоугольных координат на плоскости, и преобразования прямоугольных коордииат в полярные. Известно устройство, содержащее сумматор- вычитатель на два входа, сум матор-вычитатель на три входа, три сдвигающих регистра, блок формирования приращений (ПЗУ) блок анализа зна ка и блок управления . Недостатком его является низкое быстродействие. Наиболее близким по технической су ности к изобретений является специализированный вычислитель 2, содержа щий сумматор адреса, элемент И, блок постоянной памяти, блок управления, задающий генератор, регистр адреса и два блока вычисления координат, .кажды из которых содержит регистр координат, сумматор координат, элемент ИЛИ и элемент И. Выход задающего генерато ра соединен со входом блока управления, первый и второй выходы которого подключены к соответствующим входам блока постоянной памяти, выход которого соединен с первым входом sjieMeHта И, второй вход которого соединен с выходом блока управления и первыми входами элементов И каждого блока вычисления координат. Выход элемента И блока вычисления координат подключен к первому входу сумматора координат. Выходы регистра координат соединены со входами элемента ИЛИ. Выход элемента ИЛИ первого блока вычисления координат подключен ко второму входу элемента И второго блока вычисления кординат, а выход элемента ИЛИ второго блока вычисления координат соединен со вторым входом элемента И первого блока вычисления координат . Недостатком известного устройства является низкое быстродействие. Целью изобретения является повышение скрости преобразования координат. Поставленная цель достигается тем, что в предложенное устройство введена группа элементов И-ИЛИ и в каждый блок вычисления координат - дополнительный элемент И-ИЛИ. Первый и второй входы элемента И-ИЛИ соединены соответственно с четными и нечетными выходами регистра адреса, третий и четвертый входы, - с четвертыми и пятыми выходами блока управления, управляющими входами регистра адреса и каждого из регистров координат и первыми и вторыми входами дополнительного элемента И-ИЛИ в каждом блоке вычисления координат. Выход элемента И-ИЛИ подключен ко второму входу сумматора адреса, выход которого соединен со вхо дами регистра адреса. Третий и четвертыя входы дополнительного элемента И-ИЛИ в каждом блоке вычисления координат подключены соответственно к выходу четной и нечетной групп разрядов регистра координаты, а выход - ко второму входу сумматора координат, выход которого соединен со входами регистра координат. Структурная схема устройства пред- ставлена на чертеже. Цифровой преобразователь координат состоит из сумматора адреса 1, первые входы которого через элемент И соединены , с выходом блока постоянной памяти 3, вторые входы через перву группу элементов И-ИЛИ 4 подключены к выходам последовательно соединенных разрядов выходных четнЬй 5 и нечетной б групп регистра адреса 7. Блок 3 сое динен с первым и вторым входами блока управления 8, вход которого соединен с выходом задающего генератора 9. Блоки вычисления координат 10 и 11 представляют собой идентичные устройства, каждое из которых содержит сумма тор координат 12, первый вход которого соединен с выходом элемента И 13, а второй выход подключен к выходу допо ительного элемента И-ИЛИ 14, выходы оторого соединены с выходами младих разрядов нечетной группы и выхоамн четной группы регистра координат 15 и элемент ИЛИ 16. Выходы сумматора координат 12 блоков 10,11 и сумматора адреса 1 соединены соответственно с входами регистров 15 и 7. Блок управления 8 соединен с .выходами элементов И 2 и 13 и входами регистров 7 и 15, Выходы четных и нечетных групп регистра 15 блока 10 соединены через элемент ИЛИ 16 с входами элемента И блока 11. Рассмотрим работу цифрового преобразователя координат за время одной итерации на примере суммирования чисел на сумматоре 1, так как процесс суммирования чисел, запись результата суммирования во входную группу регистра и сдвиг информации в нем происходят и в блоках 10 и 11 идентично. Пусть в регистре 7 в итерации записалось число при п«16 и №4 вида 1001 1101 1011 ОНО, которое распределяется в четных группах регистра как число 1101 ОНО, а в нечетных группах - как число 1001 ОНО, Информация на сумматор поступает младшими разрядами. Изменение информации по циклам в (t 1)-й итерации приведено в табл. 1. Каждый цикл представляет собой половин периода задающего генератора 9. таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Устройство для решения двумерныхзАдАч МАТЕМАТичЕСКОй физиКи | 1978 |

|

SU811272A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для вывода информации на экран электронно-лучевой трубки | 1977 |

|

SU1029177A1 |

| Устройство для вычисления координат | 1978 |

|

SU752350A1 |

| Линейно-круговой интерполятор | 1982 |

|

SU1149218A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

1001ЛОН1110.1101

1110

ни

1100 По сигналу блока управления 8 выдается часть числа ААа, например, в ({ +1)-й итерации эта часть равна 1000 и поступает на вход сумматора 1 через элемент И 2. В зависимости от сигнала с блока 8,соответствующего оператору поворотаgа, прюисходит суммирование или вычитание части числа из блока 3 со значением числа нечетной группы регистра, поступающего на входы элемента И-ИЛИ 4. Результат суммирования по концу им пульса периода задающего генератора 9 передается в регистр 7 содновременным сдвигом информации в этой линейке на группу. Сдвиг информации в четных группах регистра 7 и подключение на время действия импульса период задающего генератора 9 происходит так тирующим импульсом с выхода блока уп равления 8, По сигналу блока управления 8, который соответствует паузе периода задакндего генератора 9, в той же итерации, происходит суммирование другой части числа ЛAf с информацией выходной группы 6 регистра 7, Результат суммирования по окончании второго цикла записывается в peritcTp адреса 7 со сдвигом предыдущей информации его линейки на одну группу. Процесс вычис ления в данной итерации заканчивается через четыре цикла, процесс вычислени в других итерациях аналогичен. Таким образом, пауза задающего генераторй используется активно как импульс управления в цикле вычисления, и быстродействие цифрового преобразователя координат повышается в два раза. При заданном быстродействии вычисления и выше приведенной структуре вычислителя степень параллельности понижается в. два раза. При этом обработку информации можно вести груп пами, содержащими -В два ра эа мёньше разрядов, что.позволяет сократить количество оборудования на организацию сумматоров в два раза. Формула изобретения Цифровой преобразователь координат содержащий сумматор адреса, элемент И блок постоянной памяти, блок управления, задающий генератор, региртр адреса и два блока вычисления координат каждый из которых содержит регистр координат, сумматор координат, элемент ИЛИ и элемент И, причем выход задающего генератора соединен со входом блока управления, первый и второй выходы которого подключены к соответствуквдим входам блока постоянной памяти, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходов блока управления и первыми входами элементов И каждого из блоков вычисления координат, выход элемента И блока вычисления координат подключен к первому входу сумматора координат, выхода регистра координат соединены со входами элемента ИЛИ, выfiOR элемента ИЛИ первого блока вычисления координат подключен ко второму входу элемента И второго блока вычисления координат, а выход элемента ИЛИ второго блока вычисления координат соединен со вторым входом элемента И первого блока вычисления координат, отличающийся тем, что, с целью повышения скорости преобразования координат, в него введена группа элементов И-ИЛИ и в каждый блок вычисления координат введен дополнительный элемент И-ИЛИ; причем первый и второй входы элемента И-ИЛИ соединены соответственно с четными и нечетными выходами регистра адреса; третий и четвертый входы элемента И-ИЛИ соединены с четвертыми и пятыми выходами блока управления, управляющими входами регистра адреса и каждого из регистров координат и первым и вторым входами дополнительного элемента И-ИЛИ в каждом блоке вычисления координат; выход элемента И-ИЛИ подключен ко второму входу сумматора адреса, выход которого соединен со входом регистра адреса; третий и четвертый входы дополнительного элемента И-ИЛИ в каждом блоке вычисления координат подключены соответственно к выходу четной и нечетной групп разрядов регистра координаты, а выход - ко второму входу сумматора координат, выход Которого соединен со входами регистра координат. Источники информации, принятые во внимание при экспертизе 1.Вайков В.Д. и др. Аппаратурная реализация элементарных функций в ЦВМ. гл. 3, Вопросы структурной реализации вычислительных алгоритмов . Л., изд. Лениградского университета, 1975, с.67-71. 2.Парини Система Дивиак для решения сложных навигационных задач S.A.Pariwi Divic dives dweuvevs to compEex nabigalion piesiions p-p-105-v 112 Электротехника, l§66, № 18, c.30-38.

. i . -Ж.

ivv

I

Авторы

Даты

1978-07-05—Публикация

1974-04-11—Подача