1

Изобретение относится к вычислительной технике и может быть использовано для аппаратурной реализации функций синуса и косинуса в специализированных w универсальных быстродействующих цифровых вычислительных устройствах.

Известно устройство для вычисления тригонометрических функций 1, содержащее регистр сдвига, преобразователи кода, комбинационные сумматоры, счетчики, дещифратор, триггеры, элементы И, ИЛИ, схему сравнения, блоки памяти и управления. Однако оно не обеспечивает высокого быстродействия, так как вычисления осуществляются методом последовательных итераций.

Наиболее близким техническим решением к изобретению является устройство для вычисления функций синуса и косинуса, содержащее входной регистр, два блока памяти, блок умножения, сумматор и выходной регистр, причем выходы старших разрядов входного регистра подключены к адресным входам первого и второго блоков памяти, выходы младщих разрядов входного регистра - к первой группе входов блока умножения, вторая группа входов которого подсоединена к выходам второго блока памяти, выходы блока умножения подключены к первой группе входов сумматора, выход которого соединен с входом выходного регистра 2.

Недостаток такого устройства заключается в его сложности, обусловленной необходимостью использования блоков памяти больщой емкости.

Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что

устройство для вычисления функций синуса и косинуса содержит дополнительный блок памяти и дополнительный блок умножения, причем адресные входы дополнительного блока памяти подключепы к выходам старшей подгруппы младших разрядов входного регистра, выходы дополнительного блока памяти - к первой группе входов, а выходы первого блока памяти - к второй группе входов дополнительного блока умножения, выходы которого подсоединены к второй группе входов сумматора.

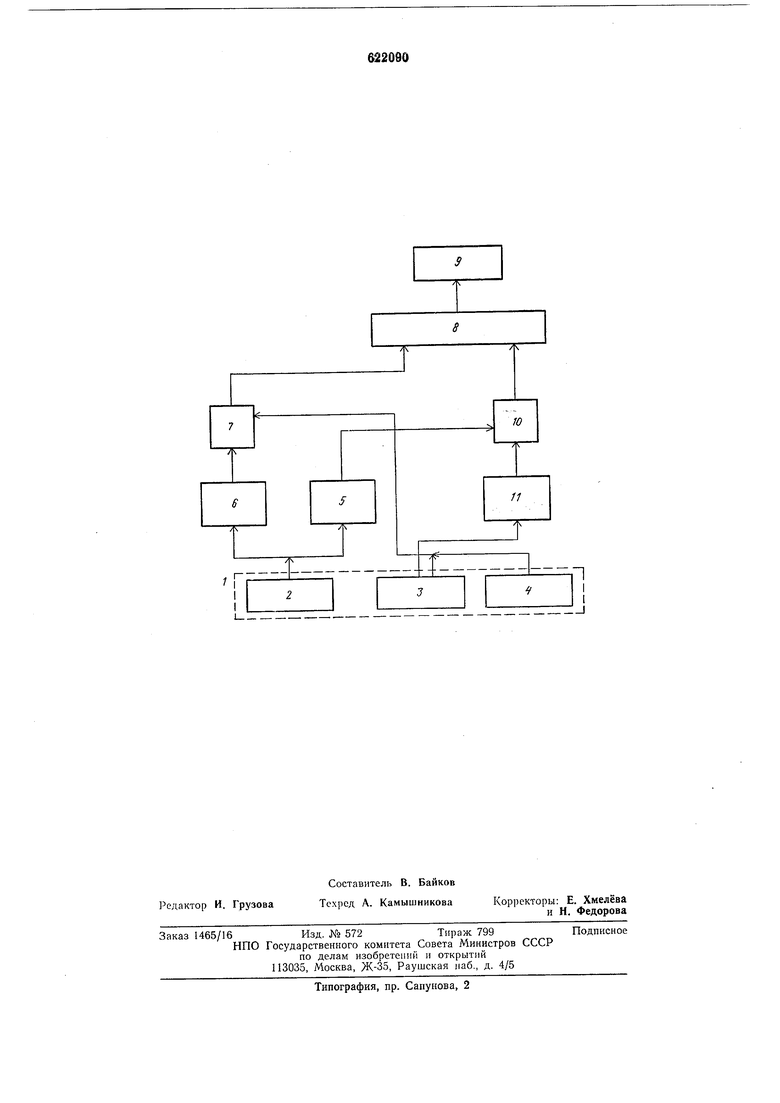

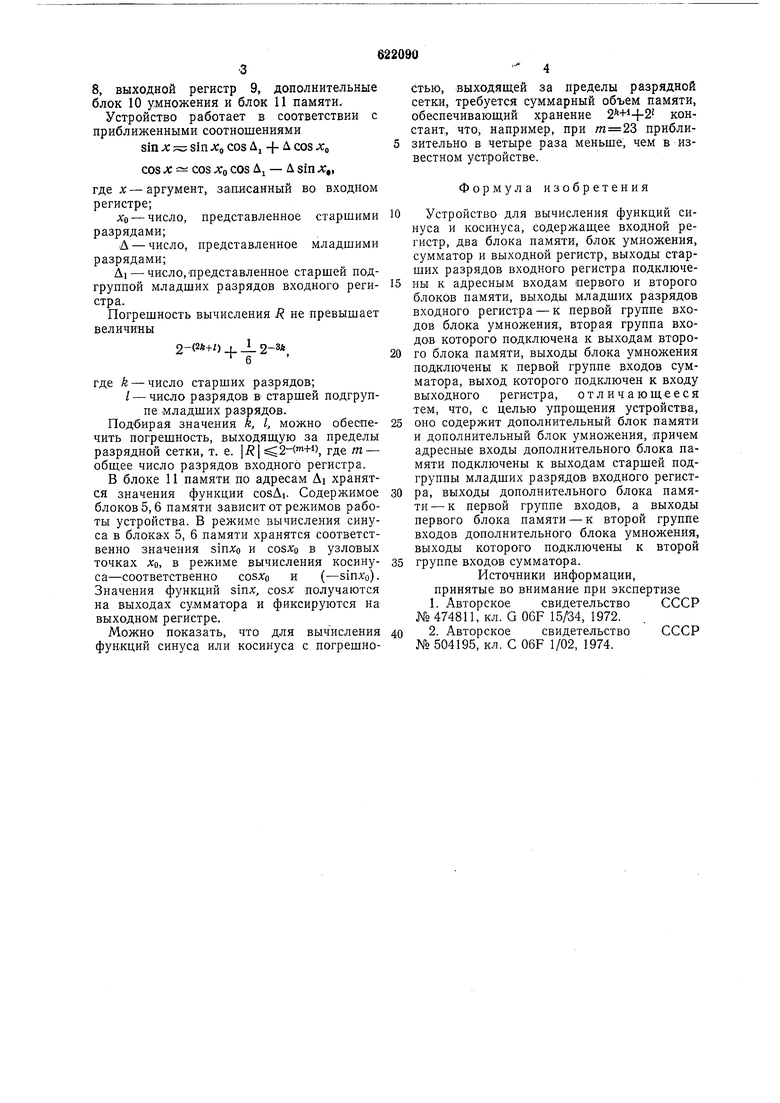

Функциональная схема устройства для вычисления функций синуса п косинуса показана на чертеже.

Она содержит входной регистр 1, представленный группой старших 2 и группой младших разрядов в виде старшей 3 и младшей 4 подгрупп, первый 5 н второй 6 блоки памятя, блок 7 умпоженпя, сумматор 8, выходной регистр 9, дополнительные блок 10 умножения и блок 11 памяти. Устройство работает в соответствии с приближенными соотношениями sin JC sin JCo COS Aj + А COS Xg COS X COS Xo COS Д1 - Д sin Xf, где X-аргумент, записанный во входном регистре; Хо - число, представленное старшими разрядами; Д - число, представленное младшими разрядами; AI - число, представленное старшей подгруппой младших разрядов входного регистра. Погрешность вычисления R не превышает величины 2-(2ft+o t JL 2-3 6 где k - число старших разрядов; / - число разрядов В старшей подгруппе младших разрядов. Подбирая значения k, I, можно обеспечить погрешность, выходящую за пределы разрядной сетки, т. е. R 2-(), где т - обшее число разрядов входного регистра. В блоке И памяти по адресам Д хранятся значения функции созДь Содержимое блоков 5,6 памяти зависит от режимов работы устройства. В режиме вычисления синуса в блока-х 5, 6 памяти хранятся соответственно значения sinxo и со8л:о в узловых точках Хй, в режиме вычисления косинуса-соответственно cosxo и (-sinxo). Значения функций ,тх, созд; получаются на выходах сумматора и фиксируются на выходном регистре. Можно показать, что для вычисления функций синуса или косинуса с погрешностью, выходящей за пределы разрядной сетки, требуется суммарный объем памяти, обеспечивающий хранение констант, что, например, при приблизительно в четыре раза меньше, чем в известном устройстве. Формула изобретения Устройство для вычисления функций синуса и косинуса, содержащее входной регистр, два блока памяти, блок умножения, сумматор и выходной регистр, выходы старших разрядов входного регистра подключены к адресным входам первого и второго блоков памяти, выходы младших разрядов входного регистра - к первой группе входов блока умножения, вторая группа входов которого подключена к выходам второго блока памяти, выходы блока умножения подключены к первой группе входов сумматора, выход которого подключен к входу выходного регистра, отличающееся тем, что, с целью упрощения устройства, оно содержит дополнительный блок памяти и дополнительный блок умножения, причем адресные входы дополнительного блока памяти подключены к выходам старщей подгруппы младших разрядов входного регистра, выходы дополнительного блока памяти - к первой группе входов, а выходы первого блока памяти - к второй группе входов дополнительного блока умножения, выходы которого подключены к второй группе входов сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 474811, кл. G 06F 15/34, 1972. 2.Авторское свидетельство СССР № 504195, кл. С 06F 1/02, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU907546A1 |

| Устройство для вычисления функций SIN х и coS х | 1981 |

|

SU974371A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

| Цифровой вычислитель функций синуса и косинуса | 1976 |

|

SU622087A1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

| Устройство для вычисления синуса и косинуса угла табличным методом | 1986 |

|

SU1348830A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Устройство для воспроизведения тригонометрических функций синуса и косинуса | 1989 |

|

SU1661800A1 |

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU922734A1 |

Авторы

Даты

1978-08-30—Публикация

1977-04-22—Подача