1

Изобретение относится к области вычислительной техники и предназначено для воспроизведения функциональных зависимостей в управляющих системах и специализированных вычислительных машинах.

Известно цифровое устройство для вычисления элементарных функций, содержащее реверсивный счетчик, дешифратор, делитель частоты с переменным коэффициентом деления, коммутатор коэффициентов деления, собирательные схемы и триггер знака, задающий режим работы счетчика 1. В устройстве реализуется метод линейной аппроксимации кривых элементарных функций в дискретной форме, причем количество линейных участков аппроксимации зависит от требуемой точности воспроизведения функции. Недостатком этого устройства являются большие аппаратурные затраты, обусловленные слол ностью таких блоков, как управляемый делитель, коммутатор и дешифратор, так как в устройстве реализуются сложные операции определения момента времени перехода с одного участка аппроксимации на другой и ввода в этот момент времени в управляющий делитель соответствующих угловых коэффициентов.

Иаиболее близким к изобретению является цифровой вычислитель функций синуса и косинуса, содержащий три группы элементов И, блок управления и регистр, выход которого соединен через первую группу элементов И с первым входом сумматора, второй вход которого подключен к выходу второй группы элементов И, вход вычислителя соединен со входом блока управления, первый, второй и третий выходы которого подключены соответственно к управляющим входам элементов И первой, второй и третьей групп 2.

Недостатком этого устройства является большое количество аппаратуры, так как для реализации искомых функций используются по два сумматора, регистра и счетчика, четыре блока управления, четыре группы элементов И, а также генератор импульсов. Кроме того, устройство обладает низким быстродействием (два такта суммирования в сумматорах и один такт сложения в регистрах, а также дополнительный цикл коррекции через каждый 21 цикл интегрирования) .

Целью изобретения является упрощение вычислителя и повышение его быстродействия. Эта цель достигается тем, что выходы сумматора соединены с информационными входами элементов И второй группы, а через элементы И третьей группы - со входами регистра, четвертый выход блока управЛенин соединен с третьим входом сумматора.

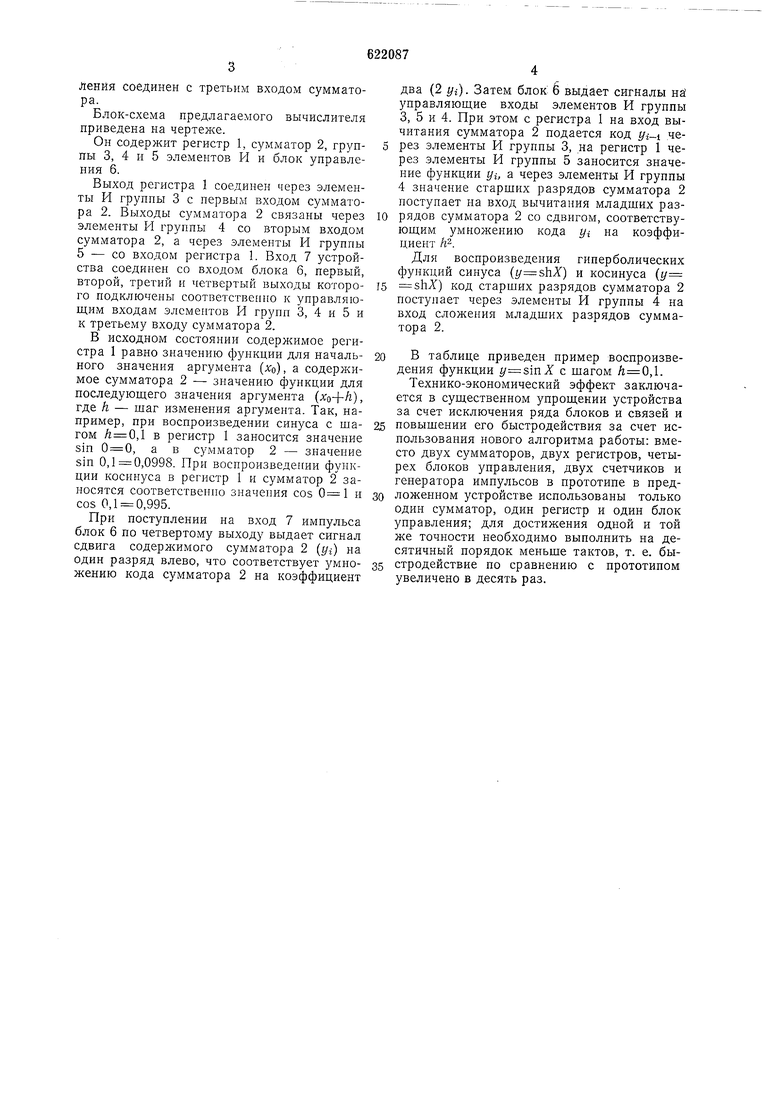

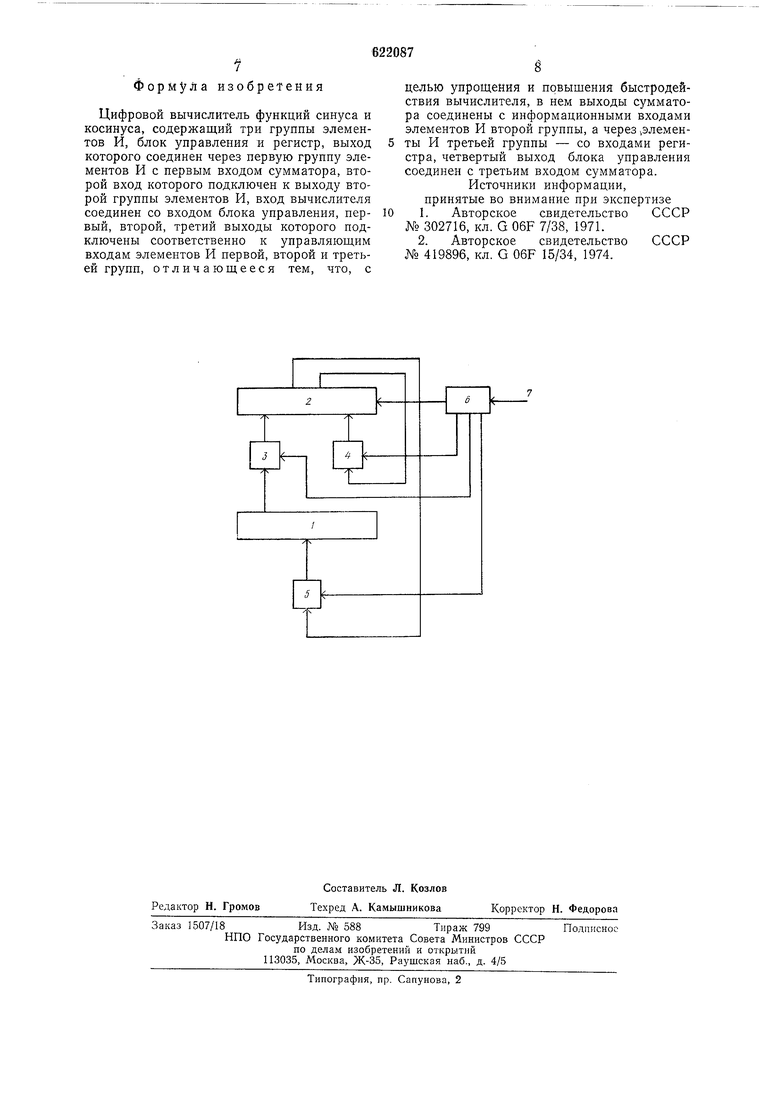

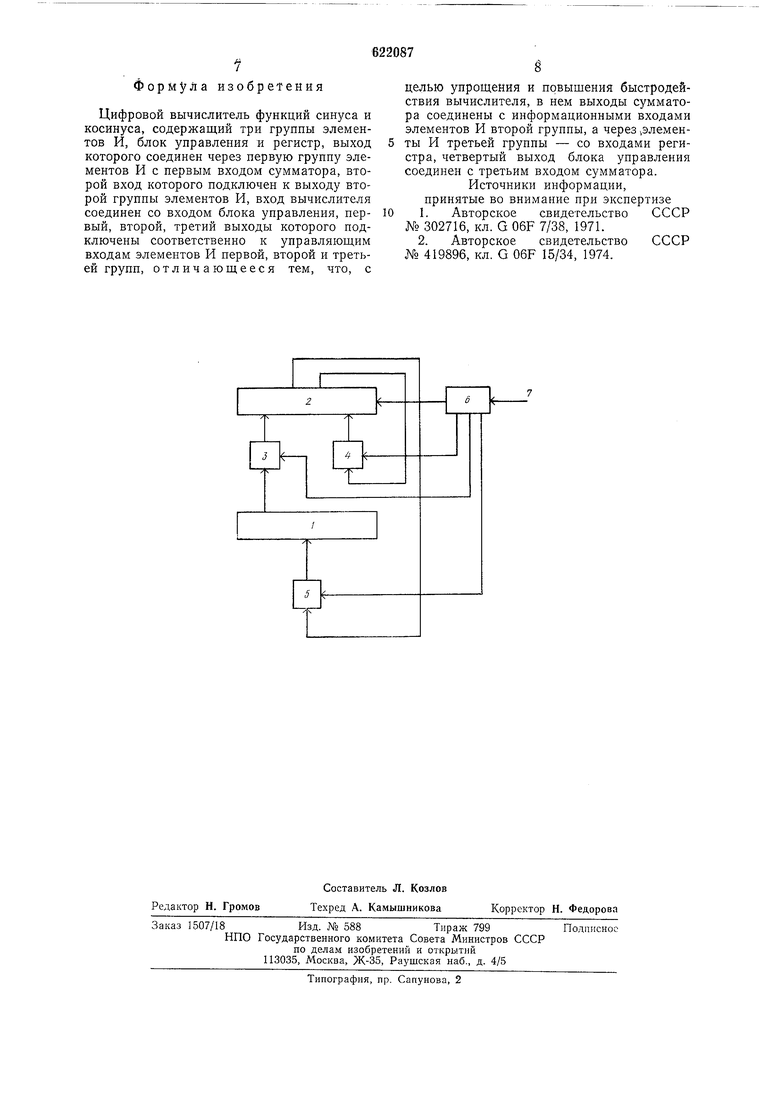

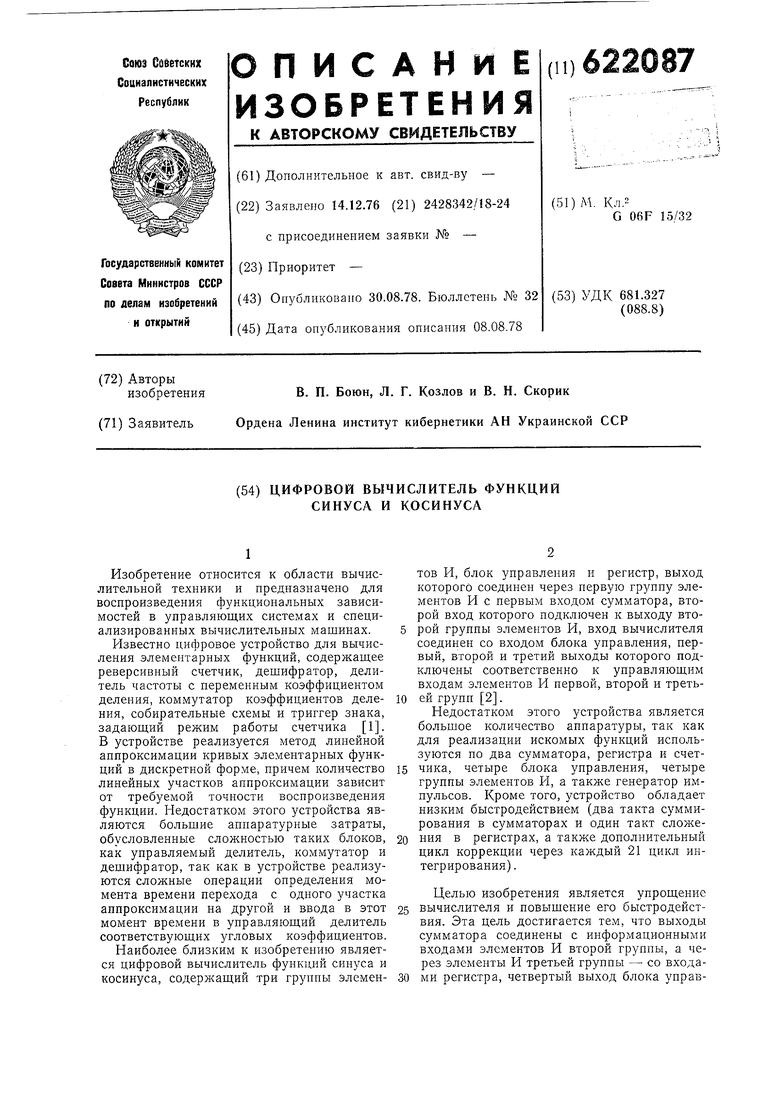

Блок-схема предлагаемого вычислителя приведена на чертеже.

Он содержит регистр 1, сумматор 2, группы 3, 4 и 5 элементов И и блок управления 6.

Выход регистра 1 соединен через элементы И группы 3 с первым входом сумматора 2. Выходы сумматора 2 связаны через элементы И группы 4 со вторым входом сумматора 2, а через элементы И группы 5 - со входом регистра 1. Вход 7 устройства соединен со входом блока 6, первый, второй, третий и четвертый выходы которого подключены соответственно к управляющим входам элементов И групп 3, 4 и 5 и к третьему входу сумматора 2.

В исходном состоянии содержимое регистра 1 равно значению функнии для начального значения аргумента (хо), а содержимое сумматора 2 - значению функции для последующего значения аргумента (xo+h), где h - шаг изменения аргумента. Так, например, при воспроизведении синуса с шагом ,1 в регистр 1 заносится значение sin , а в сумматор 2 - значение sin 0,1 0,0998. При воспроизведении функции косинуса в регистр 1 н сумматор 2 заносятся соответственно значения cos 0 1 и cos 0,1: 0,995.

При поступлении на вход 7 импульса блок 6 по четвертому выходу выдает сигнал сдвига содержимого сумматора 2 (у) на один разряд влево, что соответствует )множению кода сумматора 2 на коэффициент

два (2 г/г). Затем блок ё выдает сигналы ни управляющие входы элементов И группы 3, 5 и 4. При этом с регистра 1 на вход вычитания сумматора 2 подается код t/i-i через элементы И группы 3, на регистр 1 через элементы И группы 5 заносится значение функции Уг, а через элементы И группы 4 значение старших разрядов сумматора 2 поступает на вход вычитания младших разрядов сумматора 2 со сдвигом, соответствующим умножению кода г/, на коэффициент h.

Для воспроизведения гиперболических функций синуса () и косинуса (у

:shX) код старших разрядов сумматора 2 поступает через элементы И группы 4 на вход сложения младших разрядов сумматора 2.

В таблице приведен пример воспроизведения функции с шагом .

Технико-экономический эффект заключается в существенном упрощении устройства за счет исключения ряда блоков и связей и

повышении его быстродействия за счет использования нового алгоритма работы: вместо двух сумматоров, двух регистров, четырех блоков управления, двух счетчиков и генератора импульсов в прототипе в предложенном устройстве использованы только один сумматор, один регистр и один блок управления; для достижения одной и той же точности необходимо выполнить на десятичный порядок меньше тактов, т. е. быстродействие по сравнению с прототипом увеличено в десять раз.

т абл ицй

Формула изобретения

Цифровой вычислитель фуикций синуса и косинуса, содержащий три групны элементов И, блок управления и регистр, выход которого соединен через первую группу элементов И с первым входом сумматора, второй вход которого подключен к выходу второй группы элементов И, вход вычислителя соединен со входом блока управления, первый, второй, третий выходы которого подключены соответственно к управляющим входам элементов И первой, второй и третьей групп, отличающееся тем, что, с

целью упрощения и повыщения быстродействия вычислителя, в нем выходы сумматора соединены с информационными входами элементов И второй группы, а через (Элементы И третьей группы - со входами регистра, четвертый выход блока управления соединен с третьим входом сумматора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 302716, кл. G 06F 7/38, 1971.

2.Авторское свидетельство СССР № 419896, кл. G 06F 15/34, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой генератор гармонических колебаний | 1976 |

|

SU640283A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003081A1 |

| Цифровой вычислитель функций синуса и косинуса | 1976 |

|

SU781817A1 |

| Цифровой вычислитель функций | 1986 |

|

SU1354187A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1166103A1 |

| Цифровой генератор гармонических сигналов | 2015 |

|

RU2616877C1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU622090A1 |

Авторы

Даты

1978-08-30—Публикация

1976-12-14—Подача