старших разрядов аргумента, выход первого промежуточного регистра соединен с входом второго промежуточного регистра, подключенного через третий блок памяти к входу третьего промежуточного регистра, выходом соединенного с входом четвертого промежуточного регистра, выхрд которого подключен к первому входу первого сумматора, второй вход которого через пятый промежуточный регистр соединен с выходом сдвигателя, первый вход которого соединен с выходом шестого промежуточного регистра, подключенного через четвертый блок памяти к выходу седьмого промежуточного регистра, вход которого соединен с выходом второго сумматора, второй вход сдвигателя соединен с выходом восьмого промежуточного регистра, вход которого подключен к выходу дешифратора, вход которого соединен с выходом седьмого -промежуточного регистра,, выход второго блока памяти соединен с входом девятого промежуточного регистра, выход которого соединен с первым .входом второго сумматора, второй вход которого соединен с выходом десятого промежуточного регистра, вход которого соединен с выходом первого блока памяти, управляющие входы регистров старших и младших разрядов соединены с первым тактовым входом устройства, управляющие входы первого, девятого и десятого промежуточных регистров соединены с вторым тактовым входом устройства, управляющие входы второго и седьмого промежуточных регистров соединены с-третьим тактовым входом устройства, управляющие входы третьего, шестого и восьмого промежуточных регистров соединены с четвертым тактовым входом устройства, пятый тактовый вход которого соединен с управлякзщими входами четвертого и пятого промежуточных регистров, управляющий вход выходного регистра соединен-с шестым тактовым входом устройства.

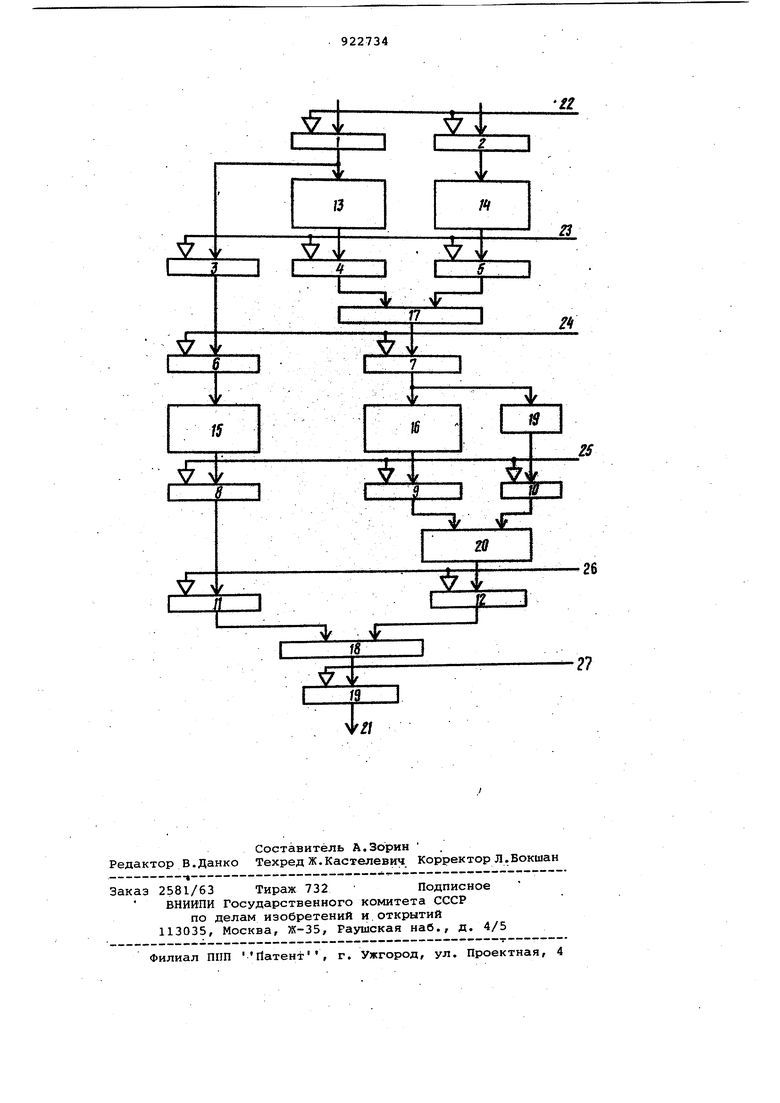

На чертеже представлена блок-схема устройства.

Устройство содержит регистр 1 старших разрядов аргумента, регистр 2 младших разрядов аргумента , промежуточные регистры 3 - 12, блоки 13 16 постоянной памяти, сумматоры 17 и 18, дешифратор 19, сдвигатель 20, выходной регистр 21, тактовые входы 22 - 27 устройства.

Тактовые импульсы, поступающие на регистры устройства, вырабатываются в генераторе тактовых импульсов (не показан). Изменение содержимого регистров происходит по переднему фронту каждого импульса записи. Для исключения гонок импульсы смещены с помо111ью элементов задержки в каж-

дои ступени на время t. Разбивка устройства регистрами позволяет работать всем ступеням независимо, поэтому сразу после освобождения первой ступени в нее загружается новый операнд, а во второй ступени уже обрабатывается операнд, прошедший первую ступень и т.д. Последовательност операций, выполняемых над операндами при прохождении всех ступеней, определяет выполнение операции вычислени синуса или косинуса. Производительность конвейерных устройств при условии обработки массивов, в которых количество операндов существенно больше числа ступеней конвейера, характеризуется длительностью такта Т продвижения данных по конвейеру Длительность такта Т определяется максимальной задержкой распростране7 НИН сигнала, которой обладают комбинационные схе№а некоторой ступени конвейера, в данном случае ступени, содержащей сумматор.

Блок 13 памяти.предназначен для хранения таблицы значений 2одг созХ в случае вычисления функции синуса и таблицы значений tog sin Xg в случае вьгаисления функции косинуса, блок 14 памяти обеспечивает таО личное преобразование величины дх в значение Вод л х; блок 15 памяти хранит таблицу значений sin Xg в случае вычисления синуса и cos XQ в случае .вычисления косинуса, блок 16 памяти выполняет преобразование вида Z - 2.

Промежуточные регистры 3-12 предназначены для хранения результатов промежуточных вычислений и для обеспечения конвейерного способа обработки.

Устройство производит вычисления на основе таблично-алгоритмического метода. Значение функций синуса и, косинуса достаточно находить в пределах изменения аргумента от О до , так как значения этих функций для произвольного значения .аргумента в силу их периодичности можно получить из значений .функций в интервале 0, путем дополнительной операции типа сложения или изменения знака.

.Вычисление функций sin х я cos х .от аргумента у.{0 х . ) производится в устройстве на основе следующих соотношений.

Пусть хо число, образованное старшими разрядами аргумента, А х число, образованное младшими разрядами аргумента.То есть разбиваем аргумент ,х ,Xg,.. .Хр на сумму узловой точки ,x-,,X|j, . . .X,, и приращение лх х - х. Тогда для фу дни синуса имеем соотношение 4sin X sin(Xo+ дх)- sin хо 2 sin - 2cos(xo+ а для функции косинуса соотношение UCOS X cos (х (J + йх)- сов X 5 -2 sin-2 sin(X(5+ ):-дх. sin выполняемые с погрешностью Е 2 которая может быть сделана выходящ за пределы разрядной сетки надлежа щим выбором параметра k. Для вычисления значений синуса косийуса получаем выражения 5Jn)(sSiTiXQ+uSin%sSinX + l,eo({ un+eo(55 tosKo) , . И ult+eoif Sinx) COSX COSXQ-fiCOSX COS) 2 Y где параметр k должен удовлетворят условию k . Устройство работает следующим образом. Значение XQ хранится в регистр старших разрядов аргумента 1, значение дх - в регистре младших раз рядов аргумента 2. В первом такте работы устройства в блоке 13 памят по значению XQ, поступающему из регистра 1,, формируется значение Sogij cos XQ при вычислении синуса и 2. sin XQ при вычислении косинуса. В блоке 14 по значению дх формируется значение gogij ax. Во втором такте эти значения записываются соответственно в промежуточ ные регистры 4 и 5, а значение х из регистра 1 записывается в промежуточный регистр 3. На сумматоре 17 формируется выражение, равное су ме содержимого регистров 4 и 5, ко торое в третьем такте записывается в прог }ежуточныйрегистр. 7, а в .прО межуточный регистр 6 записывается значение регистра 3. По значению Х поступающему из регистра б, в блоке 15 памяти, формируется значение sin при вычислении синуса и cos х Q при вычислении косинуса, а по содержимо му регистра 7 в блоке 16 постоянной памяти формируется значение j(.eoqfiui(4i°osXo) , при вычислении синуса и значение (8ос{,дх+ео1{ 5дт,Уо) р обратном коде при вычислении косинуса, то есть в блоке 16 производится преобразование z 2 Поскольку при потенцировании появля ется характеристика, то в устройств введен дешифратор 19, который, ангш зируя содержимое регистра 7, выраба тывает код, который указывает, на сколько необходимо сдвинуть значение с выхода блока 16, чтобы учесть характеристику. В четвертом такте содержимое блоков 15 и 16 и дешифратора 1$ записывается соответственно в промежуточные регистры 8 - 10.В сдвигателе 20 осуществляется указанный сдвиг, и с его выхода полученное значение записывается в пятом такте в промежуточный регистр 12, а в регистр 11 записывается содержимое регистра 8. На сумматоре 18 суммируются содержимое промежуточного регистра 11 и содержимое промежуточного регистра 12, т.е. формируется результат вычисления, который в шестом такте записывается в выходной регистр. Суммарный объем постоянной памяти для синуса и косинуса определяется выражением Q 4n-2n+64-S)(3(n-k+l) +г) , где S . Kogij k; г eogi Cn-k+l) . Используя это выражение, можно соответствующим выбором параметра k получить устройство, обеспечивающее требуемую точность вычислений с минимальным суммарным объемом постоянной памяти. Для. имеем Q 329 k. Устройство работает по конвейерному принципу. В каждом такте в него можно вводить новый операнд. По истечении первых шести тактов на выходе устройства получим первый результат, и дальше с каждым тактомна выходе устройства появляется новый результат, то есть быстродействие устройства определяется длительностью такта. Длительность, же -такта в предлагаемом устройстве определяется задержкой в наиболее времяемком узле, которым является сумматор, поэтому Быстродействие же известного устройства не превышает Т/1 2tQbi6 2t(4,, + tc .. Поскольку обычно t 5,(,:5 try а СДЬ то быстродействие предлагаемого устройства выше, чем известного в .. 5 (раз). Формула изобретения Устройство для вычисления функций синуса и косинуса, содержащее регистры старших и младших разрядов аргумента, четыре блока памяти, сумматор, сдвигатель, дешифратор, выходной регистр, причем выход регистра старших разрядов аргумента соединен с выходом первого блока памяти, выход сумматора соединен с входом выходного регистра, отличающ е е с я тем, что, с целью повышения быстродействия, в устройство введены десять рромежуточньи регистров и второй су1 1матор, причем вход первого промежуточного регистра соединен с выходом регистра старших разрядов аргумента, выход первого промежуточного регистра соединен с входом второго промежуточного регистра, подключенного через третий блок памяти к входу третьего промежуточного регистра, выходом соединенного с входом четвертого промежуточного регистра, выход которого подключен к первому входу первого сумматора, второй вход которого через пятый промежуточный регистр соединен с выходом сдвигателя, первый вход которого соединен с .выходом шестого промежуточного регистра, подключенного через четвертый блок памяти к выходу седьмого промежуточного регистра, вход которого соединен с выходом второго сумматора, второй вход сдвигателя соединен с выходом восьмого промежуточного регистра, вход которого подключён к выходу дешифратора, вход которого соединен с выходом седьмого промежуточного регистра, выход второго блока памяти соединен с девятого промежуточного регистра, выход которого соединен с первым входом второго сумматора, второй вход которого соеди нен с выходом десятого промежуточного регистра, вход которого соединен с выходом первого блока памяти, управляющие входы регистров старших

и младших разрядов соединены с первым т.актовым входом устройства, управляющие входы первого, девятого и десятого промежуточных регистров соединены с вторым тактовым входом

устройства, управляющие входы второго и седьмого промежуточных регистров соединены с третьим тактовым входом устройства, управляющие входы третьего, шестого и восьмого промежуточных

регистров соединены с четвертым тактовйм входом устройства, пятый тактовый вход которого соединен с управляющими входами четвертого и пятого промежуточных регистров, управлянвдий вход выходного регистра соединен с шестым тактовым входом уст- .. ройства.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 591857, кл.б Об Р 7/38, 1978.

2. Потапов В.И., Нестерук В.Р., Флоренсов А.Н. Быстродействующие арифметико-логические устройства . ЦВМ, Новосибирск, 1978, с. 29 - .32 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций @ @ @ @ и @ @ @ @ | 1990 |

|

SU1732342A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Цифровой функциональный преобразователь | 1982 |

|

SU1027732A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU907546A1 |

| Устройство для вычисления тригонометрических функций | 1985 |

|

SU1257639A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

Авторы

Даты

1982-04-23—Публикация

1980-02-18—Подача