Иэобрегение относится к вычислигепьной технике и может быть применено при построении специапизированных вычислитепьных устройств и функциональных преобразователей информации.

Известно устройство цля возведения двоичного числа в четвертую степень, содержащее элементы зацержки, двоичный счетчик, выходы которого через первую |грулпу элементов И соединены со входаРИМ первого сумматора, выходы которого через вторую и третью группы элементов И лоцключены ко входам второго сумматора, выходы которого через четвертую группу элементов И соединены со входами третьего сумматора. Оно имеет низкое быстродействие, так как исходное число представляется в вице поспецоватепъг,ности импульсов, для обработки каждого из которых в устройстве затрачивается четыретакта. Наиболее близким-к изобретению техническим решением является усфойство для возведения двоичного числа в степень, содержащее г/ - разрядный регистр числа и три суммато -

ра, причем выход каждого - го разряда регистра числа соединен со входом ( +1)-го разряда первого сумматора, шина сдвига устройствасоединена со-входами сдвига регистра числа, первого и третьего сумматоров, первый информационный вход устройства соединен со входом младшего разряда регистра чиспа. Это известное устройство характеризуется большим объемом оборудования и ни КИМ быстродействием, вызванным последовательным характером передачи информации через длинную цепочку последовательно соединенных блоков.

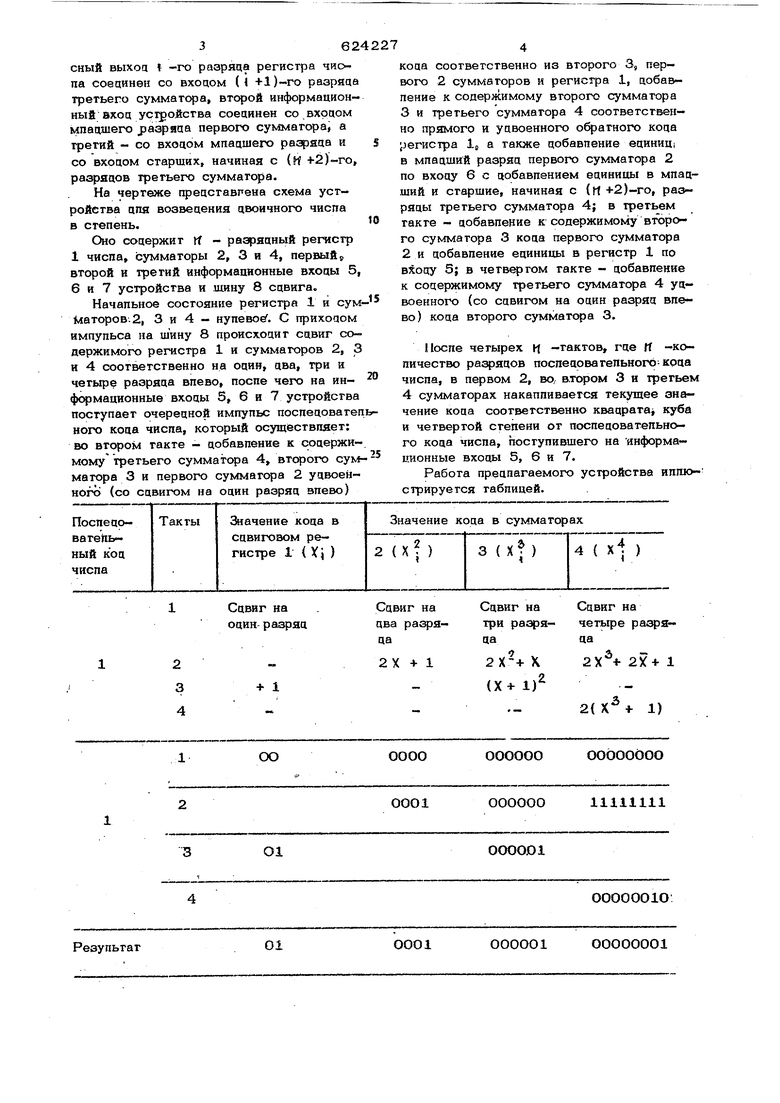

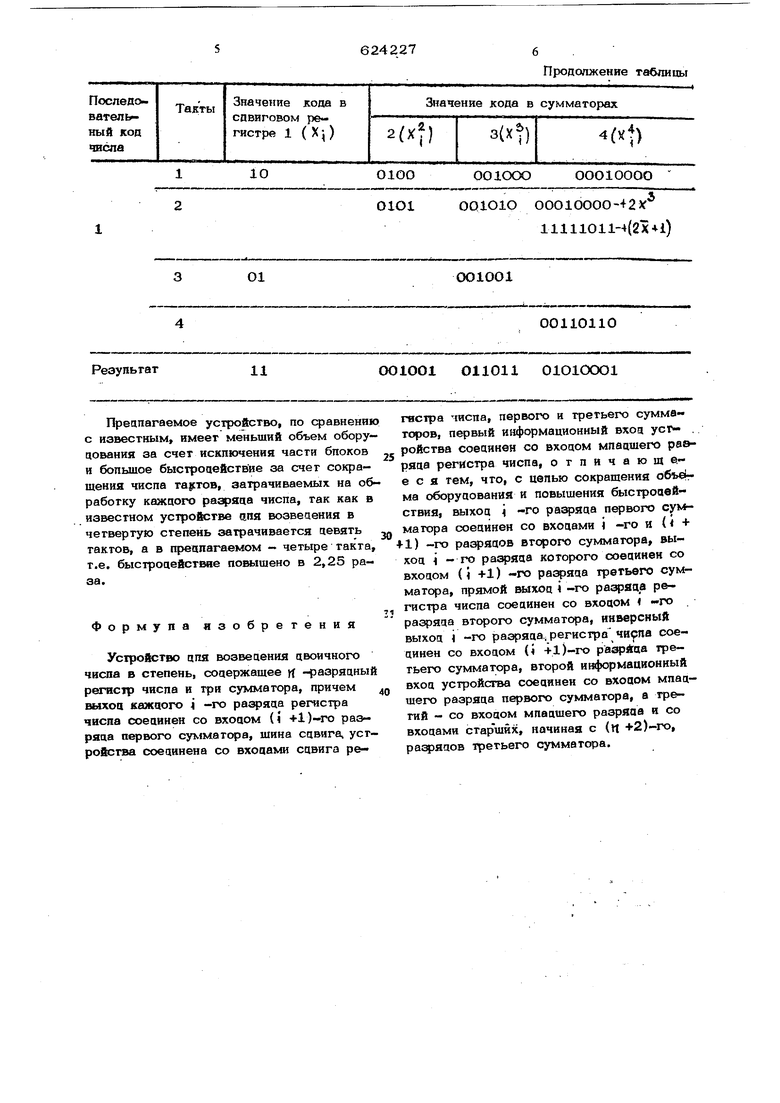

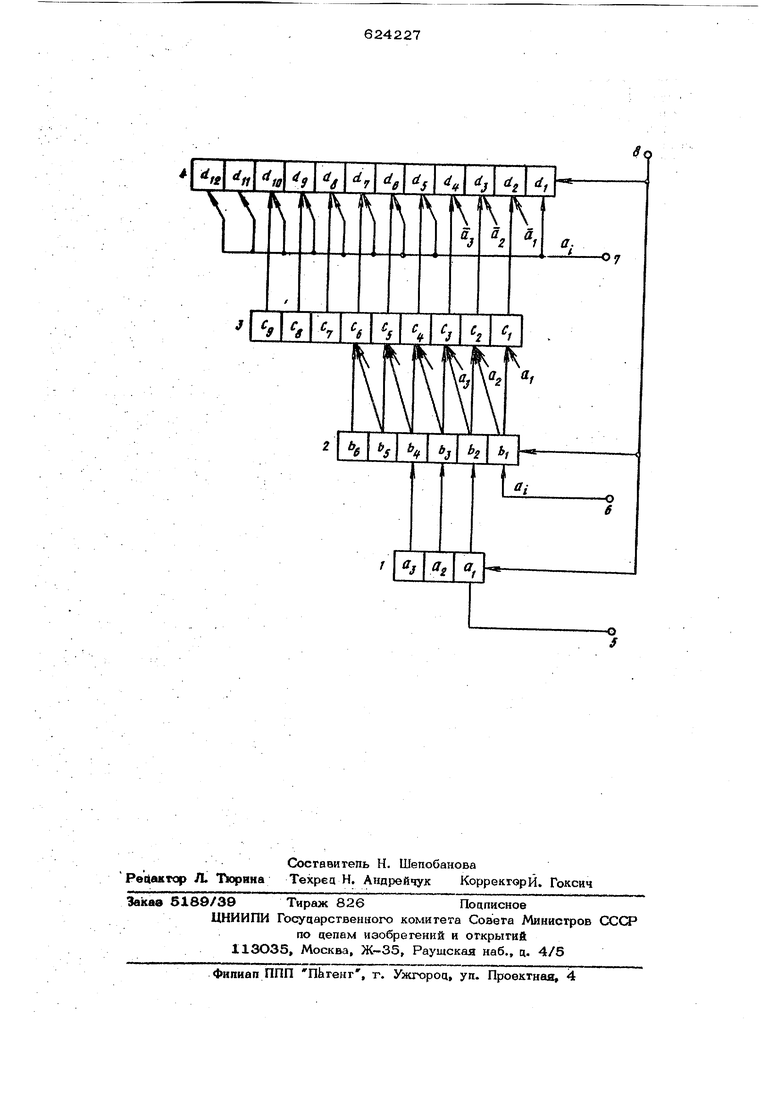

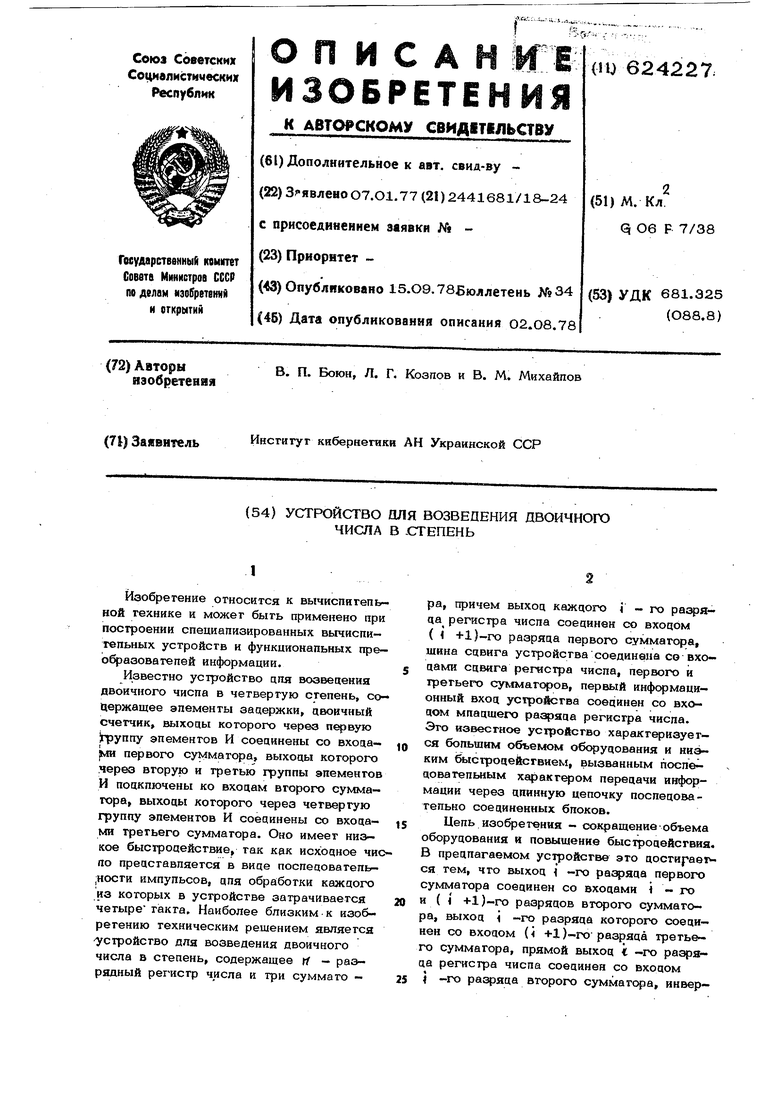

Цель изобретения - сокращение объема оборудования и повышение быстродействия В предлагаемом устройстве это достирается тем, что выход -го первого сумматора соединен со входами - го и ( +1)-го разрядов второго сумматора, выход -го разряда которого соединен со входом ( +1 )-го разряда третьего сумматора, прямой выход -го разряда регистра числа соединен со входом 4 -го разряда второго сумматора, инвер- 362 сный выхоц I -го рааряца регистра числа соецинен со вхоцом ( i +1 )-го разряда третьего сумматора, второй информацион ный вхоц устройства соецинен со входом мпацшего jiaapaaa первого сумматора, а третий - со вхоцом мпацшего рааряца и со вхоцом старших, начиная с (Н ь2)-го, рааряцов третьего сумматора. На чертеже прецставпена схема устройства цпя воавецения цвоичного чиспа в степень. Оно соцержит tf - рааряцный регистр 1 чиспа, сумматоры 2, 3 и 4, первый, второй и третий информационные вхоцы 5, 6 и 7 устройства и шину 8 сцвига. Начальное состояние регистра 1 и сум Маторов.2, 3 и 4 - нулевое. С приходом импульса на шину 8 происходит сцвиг содержимого регистра 1 и сумматоров 2, 3 и 4 соответственно на оцин, цва, три и четьфе раэряца влево, после чего на информационные вхоцы 5, 6 и 7 устройства поступает очерецной импульс послецовател ного коца чиспа, который осущ ествляет: во втором такте - цобавление к содержимомутретьего сумматора 4 второго сум матора 3 и первого сумматора 2 уцвоенного (со сдвигом на оцин разряд влево) коца соответственно из второго 3, первого 2 сумматоров и регистра 1, добавление к содержимому второго сумматора 3и третьего сумматора 4 соответственно прямого и уцвоенного обратного коца регистра Ij а также цобавпение ециниц; в млацший разряц первого сумматора 2 по вхоцу б с добавлением ециницы в младший и старшие, начиная с (rt +2)-го, разряцы третьего сумматора 4; в третьем такте - цобавление к содержимому второго сумматора 3 коца первого сумматора 2 и цобавление ециницы в регистр 1 по 5; в четвертом такте - добавление к содержимому третьего сумматора 4 уц- военного (со сцвигом на оцин разряд влево) коца второго сумматора 3. После четырех ц -тактов, гце f -количество рааряцов поспецовательного-коца числа, в первом 2, во, в.тором 3 и третьем 4сумматорах накапливается текущее значение кода соответственно квадрата куба и четвертой степени от последовательного коца числа, поступившего на информационные вхоцы 5, 6 и 7. Работа прецпагаемого устройства иллюстрируется таблицей.

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое логарифмирующее устройство | 1976 |

|

SU624233A1 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040604A2 |

| Цифроаналоговый преобразователь со степенной характеристикой | 1980 |

|

SU907562A1 |

| Устройство для обработки информации | 1973 |

|

SU624232A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1982 |

|

SU1037266A1 |

| Сигнатурный анализатор | 1981 |

|

SU1048475A1 |

| Устройство для умножения | 1983 |

|

SU1080136A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Цифровой интегратор | 1981 |

|

SU1035605A1 |

10

Ol

Реэупьгаг

11 Предлагаемое устройство, по сравнению с известным имеет меньший объем оборудования за счет исключения части блоков и большое быстроцействие за счет сокращения числа тактов, затрачиваемых на обработку каждого разряда числа, так как в известном устройстве аия возвецения в четвертую степень затрачивается девять тактов, а в предлагаемом - четыре такта, т.е. быстродействие поы 1шено в 2,25 раза. Формула изобретения Устройство для возведения двоичного чиспа в степень, содержащее -разрядный регистр числа и три сумматора, причем выхоа каждого j -го разряда регистра числа соединен со входом ({ +1)-го разряда первого сумматора, шина сдвига, устройства соединена со входами сдвига реО1ОО

ООО10ООО

ОО1ООО

01О1 OQ1O10 00010000-4 2 Y

lH11011-4(2X+i)

OOlOOl

00110110

OOlOOl OllOll OlOlOOOl гистра числа, первого и третьего сумма-« торов, первый информационный вход усг«- , ройства соединен со входом младшего ра&ряда регистра числа, отличающееся тем, что, с целью сокращения объеи ма оборудования и повышения быстродействия, выход -го разряда первого сук матора соединен со входами i -го и (1 + ) -го разрядов второго сумматора, выход i - го разряда которого соединен со входом (i +1) -го рагряда третьего сумматора, прямой выход -го разраав регистра числа соединен со входом -го разряда второго сумматора, инверсный выход i -го разряда, регистра чирпа соединен со входом ( +1)-го разрАца третьего сумматора, второй информационный вход устройства соединен со входом младшего разряда первого сумматора, а третий - со входом младшего разряда и со входами старшйх, начиная с (ц +2)-го, третьего сумматора. l4 //K/d

Авторы

Даты

1978-09-15—Публикация

1977-01-07—Подача