Изобретение относится к цифровой вычисли те пьной технике.

Изьестно устройство цпя обработки информации, соцержашве бпок микропрограммного управления, операционные блоки, шины номера операционного блока, шины информации от внешних устройств, шины уп|эавпяюших сигналов, шины выхоцной инфорИацин и шины освецомнтельных сигналов от внешних устройств flj . Наиболее близ Ким к изобретению техническим решением является устройство аля обработки информации, содержащее блок микропрограммно1го управления, выхоц которого соединен с Ьцннм вхоцом блока управления магистралью, второй вхоа подключен ко входной |магнсгралнь а выход соединен с выходной магистралью, которая соединена с магнс ральными входами операционных блоков, магистральные выходы которых соединены со входной магистралью, шина номера операционного блока и шина информации от внешних ус тройств, соединены с одноименными входами соответствующих операционных блоков шина управляющих сигналов

подключена ко входам слова микрокомана информации от внешних устройств к осве доми тельных сигналов от внешних уст ройсгв ус тройства для обработки информации И соединена с одноименными вхоцамн операционных блоков, а шина выходной информации соединена с выходами адреса микрокоманд, ииформации к внешним устройствам, адреса к внешним устройствам в управляющих сигналов устройства апя обработки информации и подключена к одноименным выходам соответствующих операционных блоков. Для сокращенна аппаратурных затрат и улучшения эксппуатацнонных характеристик в нем входы и выхо ды операционных блоков соединены с BXOQной и выходной магистралями . . С анако это известное устройство при изменении алгоритма требует значительных ear- pa т для изменения программного обеспечения а его блоки - больших аппаратурных затрат для их изготовления.

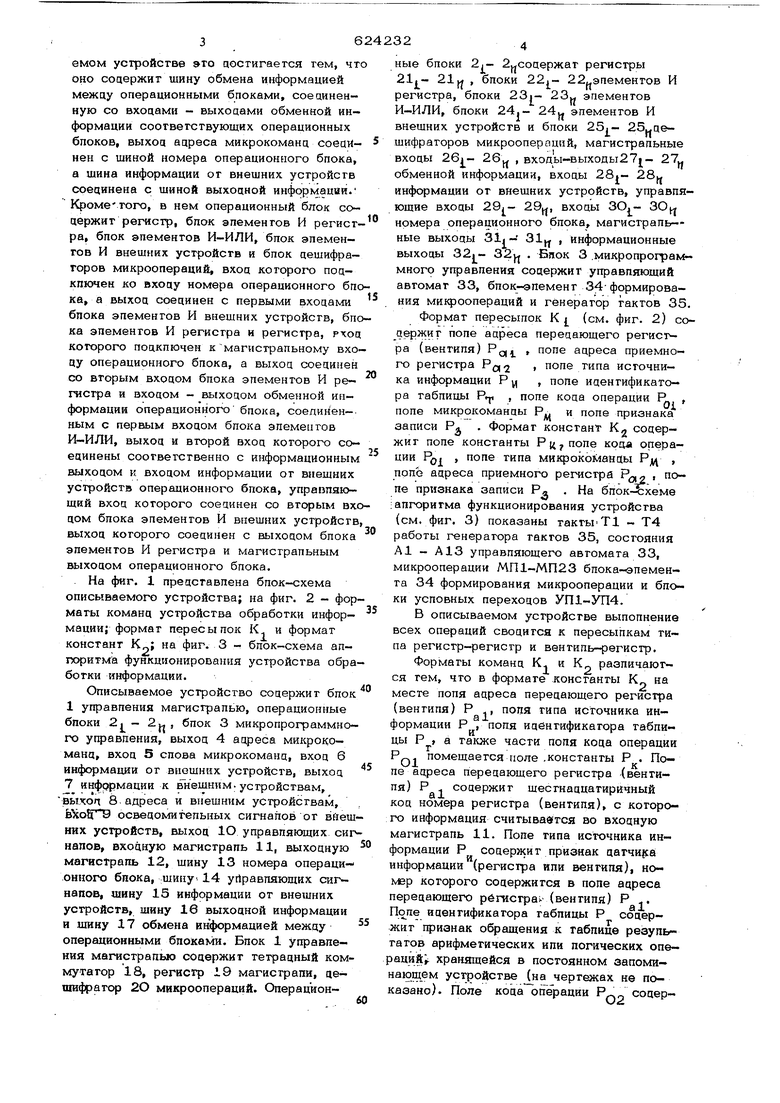

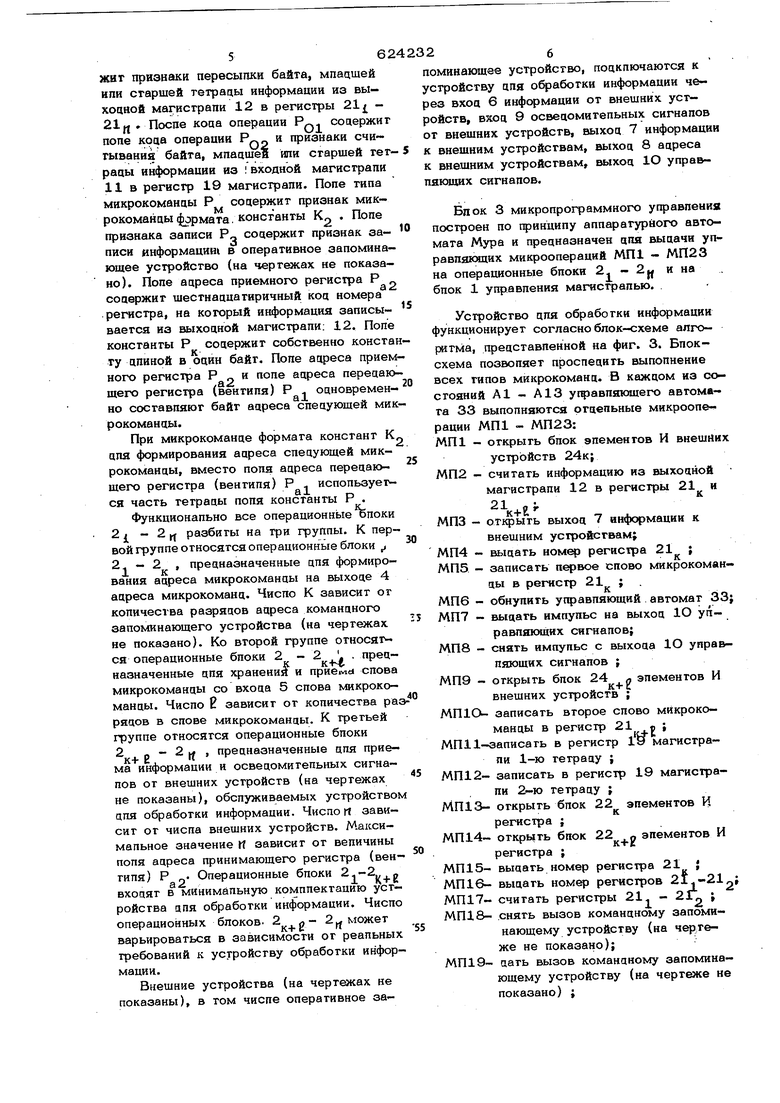

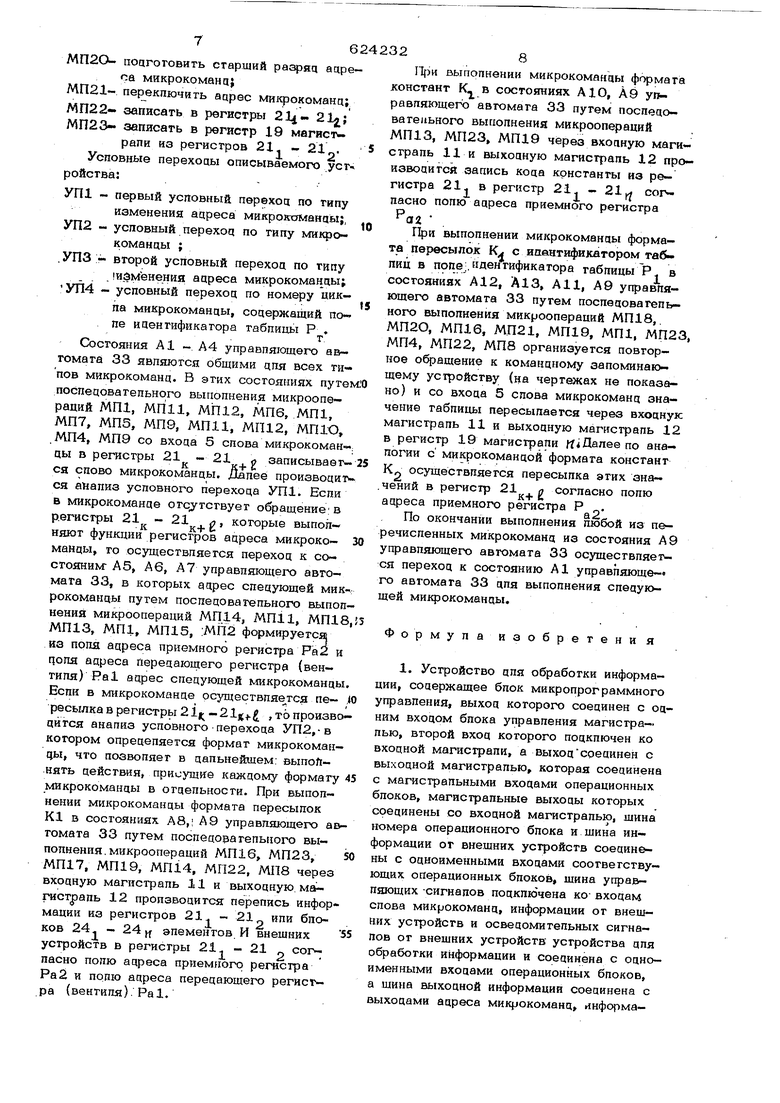

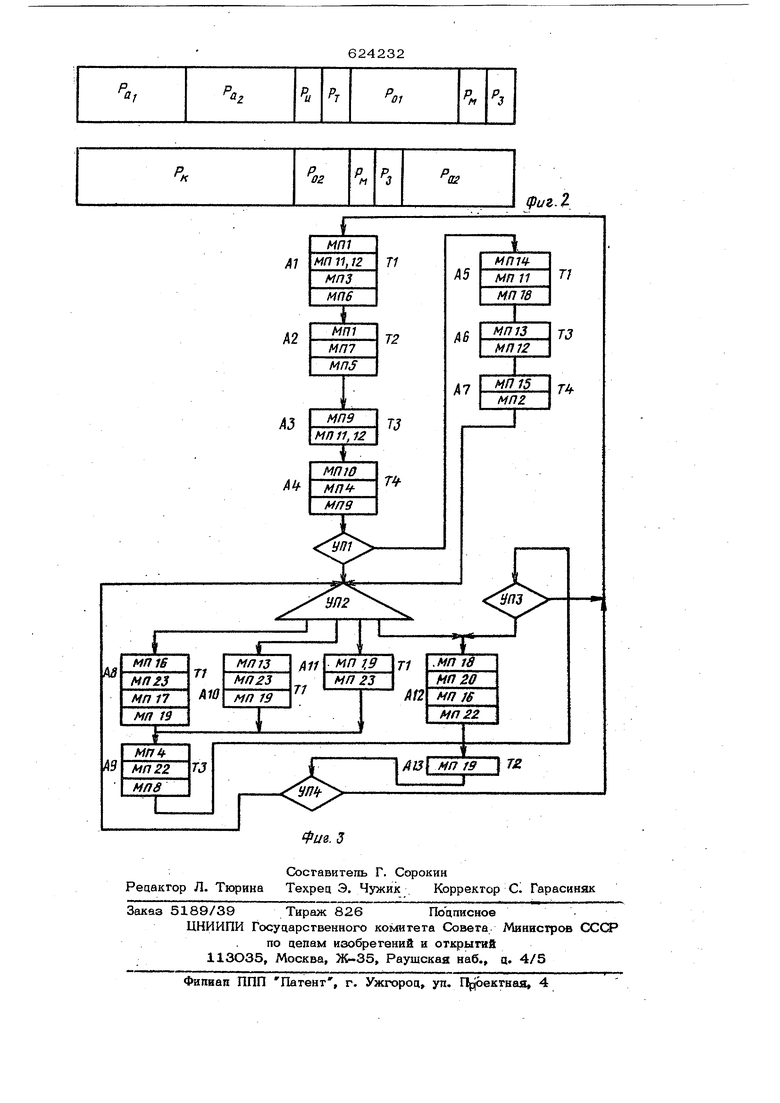

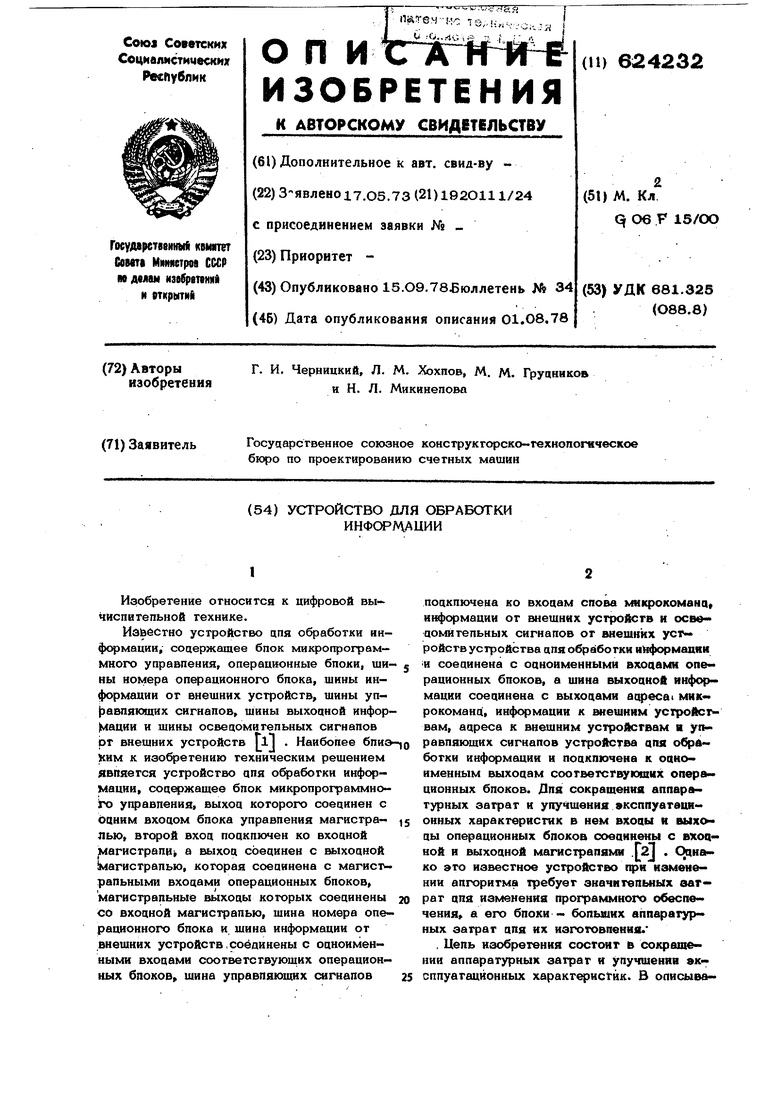

, Цель изобретения состоит ь сокращении аппаратурных затрат н улучшении аксплуатационных характ нстйк. В описыва- емом устройстве эго досгигается тем, чт оно соцержит шину обмена информацией между операционными бпоками, соециненную со входами - выходами обменной информации соогвегствующих операционных бпоков, выход адреса микрокоманд соединен с шиной номера операционного бпока, а шина информации or внешних у сгройсгв соединена с шиной выходной информации. Кроме того, в нем операционный блок содержит регистр, бпок эпеменгов И регист ра, бпок эпементов И-ИЛИ, блок эпеменгов И внешних устройств и бпок дешифраторов микроопераций, вход которого подключен ко входу номера операционного бп ка, а выход соединен с первыми входами бпока эпеменгов И внешних устройств, бп ка эпементов И регистра и регистра, рход которого подключен к магистральному вхо ду операционного бпока, а выход соединен со вторым входом бпока эпементов И регистра и входом - выходом обменной информации операционного бпока, соединенным с первым входом бпока эпеменгов И-ИЛИ, выход и второй вход которого соединены соответственно с информационным выходом и. входом информации от внешних устройств операционного бпока, управпяющнй вход которого соединен со вторым вх дом бпока эпеменгов И внешних устройств выход которого соединен с выходом бпока эпементов И регистра и магистральным выходом операционного бпока. . На фиг. 1 представлена бпок-схема описываемого устройства; на фиг. 2 - фор маты команд устройства обработки информации; формат пересыпок К. и формат констант на фиг. 3 - бпок-схема апгуэритма функционирования устройства обра ботки информации. Описываемое устройство содержит бпок 1 управпения магистралью, операционные бпоки 2. - 2vj , бпок 3 микропрограммного управпения, выход 4 адреса микрокоманд, вход 5 слова микрокоманд, вход 6 информации от внешних устройств, выход 7 информации к внешним-ус тройствам, выхот 8, адреса и внешним устройствам, B oSb осведоми гепьных сигналов от внеш них устройств, выход 1О управляющих сиг напов, входную магистраль 11, выходную магистраль 12, шину 13 номера операци- онного бпока, шину 14 уйравляющих сигналов, шину 15 информации от внешних устройств, шину 16 выходной информации и шину 17 обмена информацией между операциониыми блоками. Бпок 1 управпения магистралью содержит тетрадный коммутатор 18, регистр 19 магистрали, аещифратор 2О микроопераций. Операцион1,- 2 содержат регистры ные бпоки 2 22i- 22.,эпементов 21t- 21„. бпоки 23р 23„ регистра, бпоки 2cJi- - эпементов И-ИЛИ, блоки 24,- 24. эпементов И внешних устройств и бпоки 25| дешифраторов микроопераций, магистральные входы 26i- 26. , входы-выходы27j- 27„ обменной информации, входы 28fj информации от внешних устройств, управпяющие входы 29, входы ЗО номера операционного бпока, магистраль-ные выходы 31i- 31 , информационные выходы 32у . Бпок 3 .микропрограммного управления содержит управляющий автомат 33, блок-элемент 34-формирования микроопераций и генератор тактов 35. Формат пересыпок К (см. фиг. 2) содержит попе адреса передающего регис ра (вентипя) РОЦ. попе адреса приемного регистра Рд попе типа источника информации Ру , попе идентификатора таблицы Pff поле кода операции R , поле микрокоманды Р и поле признака записи Рд . Формат констант К содержит поле константы кода операции Рл| , попе типа микрокоманцы Р попе адреса приемного регистра , поле признака записи Р . На бпок-схеме ; алгоритма функционирования устройства (см. фиг. 3) показаны тактыТ - Т4 работы генератора тактов 35, состояния А1 - А13 управпяюшего автомата 33, микрооперации МП1-МП23 блока-элемента 34 формирования микрооперации и блоки условных переходов УП1-ЗТ14. В описываемом устройстве выполнение всех операций сводится к пересылкам типа регистр-регистр и вентиль-регистр. Форматы команд К и К„ различаются тем, что в формате константы К„ на месте поля адреса передающего регистра (вентиля) Р ., поля типа источника информации Р , поля идентификатора таблицы Р , а также части поля кода операции Р„. помешается поле .константы Р . Поле адреса передающего регистра -(венти- пя) Р содержит шестнадцатиричный код номера регистра (вентиля), с которого информация считывается во входную магистраль 11. Поле типа источника информации Р содержит признак дагчи|са информации (регистра или вентипя), ноivep которого содержится в попе адреса передающего регистра - (вентиля) Р . идентификатора таблицы Р содержит признак обращения к таблице результатов арифметических или логических one- раций. хранящейся в постоянном запоминающем устройстве на чертежах не показано). Поле кода операции Р, содержит признаки пересыпки байта, мпацшей ипи старшей тетрацы информации из вы- хоцной магистрали 12 в регистры 21 21 л После кода операции PQ-, содержит попе Koqa операции PQO признаки счи тывания байта, мпацшеи ипи старшей тет рацы информации из входной магистрали 11 в регистр 19 магистрали. Попе типа микрокоманцы Р соцержит признак микрокоманды формата, константы Кр . Попе признака записи Р содержит признак записи информации в оперативное запоминающее устройство (на чер тетках не показано). Попе адреса приемного регистра Р содержит шестнадцатиричный код номера регистра, на который информация записывается из выходной магистрапи; 12, Попе константы Р содержит собственно конста ту длиной в оцин байт, Поле адреса прием ного регистра Р и попе адреса передаю щего регистра (вентиля) Р одновременно составляют байт адреса следующей ми рокоманды. При микрокоманде формата констант K для формирования адреса следующей микрокоманды, вместо поля адреса передак щего регистра (вентипя) Р используется часть тетрады поля константы Р , Функционально все операционные олоки 2 - 2. Y( разбиты на три группы, К первой группе относятся операционные блоки 2 - 2 , предназначенные для формирования адреса микрокоманды на выходе 4 адреса микрокоманд. Число К зависит от количества разрядов адреса командного запоминающего устройства (на чертежах не показано). Ко второй группе относят ся операционные блоки 2 - 2 /. . пред- иачЗначенные для хранения и приема слова микрокоманды со входа 5 слова микрокоманды. Число В зависит от количества ра рядов в слове микрокоманды. К третьей группе относятся операционные блоки 2 Р - 2 ( , предназначенные для приема информации и осведомительных сигналов от внешних устройств (на чертежах не показаны), обслуживаемых устройством цля обработки информации. Чиспо п зависит от числа внешних устройств. Максимальное значение rt зависит от величины поля адреса принимающего регистра 1вен- тиля) Р „. Операционные блоки 2,-2 входят в минимальную комплектацию устройства для обработки информации. Число операционных блоков. 2 ., - 2 может К+ варьироваться в зависимости от реальных требований к устройству обработки информации. Внешние устройства (на чертежах не показаны), в том числе оперативное за/оминающее устройство, подключаются к стройству для обработки информации чеез вход 6 информации от внешних устойств, вход 9 осведомительных сигналов т внешних устройств, выход 7 информации внешним устройствам, выход 8 адреса внешним устройствам, выход 1О управяющих сигналов. Блок 3 микропрограммного управления построен по принципу аппаратурного автомата Мура и предназначен для выдачи управлякмцих микроопераций МП1 - МП23 на операционные блоки 2 - 2jj и на блок 1 управпения магистралью. Устройство для обработки информации функционирует согласно блок-схеме алгоритма, представленной на фиг, 3, Блоксхема позволяет проследить выполнение всех типов микрокоманд. В кажцом из состояний А1 - А13 управляющего автомата 33 выполняются отдельные микрооперации МП1 - МП23: МП1 - открыть блок элементов И внешних устройств 24к; МП2 - считать информацию из выходной магистрали 12 в регистры 21 и +1 МПЗ - открыть выход 7 информации к внешним устройствам; МП4 - ном регистра 21 ; МПЗ. - записать первое слово микрокоманды в регистр 21 ; МП6 - обнулить управляющий автомат 33} МП7 - выдать импульс на выход Ю управляющих сигналов; МП8 - снять импульс с выхода Ю управляющих сигналов ; МП9 - открыть блок 24 элементов И внешних устройств ; МП1О- записать второе слово мйкрокоманды в регистр 2 « Itf МП -записать в регистр 9 магистра- 19 Mai ли 1-ю тетраду ; записать в регистр 19 магистрали 2-ю тетраду ; МП 13- открыть блок 22 элементов И регистра ; МП 14- открыть блок 22 « элементов И регистра ; МП 15- выдать номер регистра 21 J МП16- выдать номер регистров 2Ij -2l2i МП17- считать регистры 21 - 21 МП 8- снять вызов командному запоминающему устройству (на чертеже не показано); МП 9- цать вызов командному запоминающему устройству (на чертеже не показано) ; МПЗСХ- поцгоговить старший разряд ацре- оа микрокоманд} МП21- переключить ацрес микрокоманц; МП22- записать в регистры 21i- МП23- записать в регистр 19 мвгистрапи из регистров 21- - 21 . Условные перехоцы описываемого усг-« ройства: УГН - первый условный переход по типу изменения ацреса микрокоманды;, УП2 - условный перехоц по типу микрокоманды ; .УПЗ - второй условный перехоц по типу . . изменения ацреса микрокоманды; УП4 условный перехоц по номеру иикла микрокоманды, содержащий поле идентификатора таблицы Р . Состояния А1 - А4 управляющего автомата 33 являются общими цпя всех ти, пов микрокоманд. В этих состояниях путе поспецовательного выполнения микроопераций МП1, МПИ, МП12, МП6, МП1, МП7, МПЗ, МП9, МП 11, МП 12, МПЮ, МП4, МП9 со входа 5 спова микрокоманцы в регистры 21 - 21 записываетк -к+ 2 ся слово микрокоманды, jutanee производит ся анализ условного перехода УП1. Если в микрокоманде отсутствует обращение: в р.егистры 21 - 21 д, которые выпол, кКт tняют функции регистров ацреса микрокоманцы, то осуществляется переход к состояние А5, А6, А управляющего автомата 33, в которых адрес следующей мик рокоманды путем последовательного выпол нений микроопераций МП14, МП11, МП18 МП13, МП1, МП15, :МП2 формируется из ПОЛЯ ацреса приемного регистра Ра2 и поля ацреса передающего регистра (вентиля) Pal ацрес слецующей микрокоманды Если в микрокоманде осуществляется пе- ,10 ресылка в регистры 2ij -21jj;.g , то производится анализ условного Перехода УП2,-в котором определяется формат микрокоманды, что позволяет в дальнейшем: выпойнять действия, присущие каждому формату 45 с микрокоманды в отдельности. При выполнении микрокоманды формата пересылок К1 в состояниях А8, А9 управляющего а томата 33 путем последовательного выполнения, микроопераций МП16, МП23, МП17, МП19, МП14, МП22, МП8 через входную магистраль 11 и выходную магистраль 12 производится перепись инфор мации из регистров 21 - 21 или блоков 24- - 24ц элементов И внешних устройств в регистры 21- - 21 „ сог ласно полю адреса приемного регистра Ра 2 и попю адреса передающего регистра (вентиля). Pal. ITfjH выполнении микрокоманды формата констант К- в состояниях А10, Л9 управляющего автомата 33 путем послеаоватеаьного выполнения микроопераций МП13, МП23, МП19 через входную магис траль 11 и выходную магистраль 12 про- иавоцитсй запись коца константы из регистра 21j в регистр 21 - 21, согласно полю адреса приемного регистра ТЬрк выполнении микрокоманды формата пересылок Kj с ипантификатором таблиц в npnej.идентификатора таблицы Р. в состояниях А12, А13, All, А9 уфавпяющего автомата 33 путем послецовательного выполнения микроопераций МП 18,. МП2О, МП16, МП21, МП19, МП1, МП23, МП4, МП22, МП8 организуется повторное обращение к команцгюму запоминающему устройству (на чертежах не показа„) „ „ „ 5 „ микрокоманд значение таблицы пересылается через вхоцнук магистраль 11 и выходную магистраль 12 в регистр 19 магистрали /fi Далее по аналогии с микрокомандой формата констант j осуществляется пересылка этих значений в регистр 21 а согласно полю К+ ft. ацреса приемного регистра Р „. По окончании выполнения любой из перечисленных микрокоманд из состояния А 9 управляющего автомата 33 осуществляешься переход к состоянию А1 управпяюще-« го автомата 33 для выполнения следук щей микрокоманды. Формулаизобретени я 1. Устройство для обработки информации, содержащее блок микропрограммного управления, выход которого соецинен с одним входом блока управления магистралью, второй вход которого подключен ко входной магисфали, а выходсоединен с выходной магистралью, которая соединена магистральными входами операционных блоков, магистральные выходы которых соединены со входной магистралью, шина номера операционного блока и щина информации от внешних устройств соецин&ны с одноименными входами соответствующих операционных блоков, щина управляющих -сигналов подключена ко входам слова микрокоманд, информации от внешних устройств и осведомительных сигналов от внешних устройств устройства для обработки информации и соединена с одноименными входами операционных блоков, а щина выходной информации соединена с выходами адреса микрокоманд, информа- цин к внешним устройствам, ацреса к внешним устройствам и управляющих сиг- напов устройства цпя обработки информации и аоцкпючена к оцноименным выходам соогвётсгвующих операционных блоков, огпичающ.ееся тем, что, с це- пью сокращения аппаратурных затрат и улучшения эксппуагаиионньсх характеристи оно соаержит шину обмена информацией межцу операционными блоками, соединенную со входами-выходами обменной инфор мации соответствующих операционных бло ков, выход адреса микрокоманд соединен с шиной номера операционного блока, а шина информации от внешних устройств соединена с шиной выходной информации. 2, Устройство по п. 1, о т п и ч а е е с я тем, что операционный блок со держит регистр, блок элементов И регист ра, блок элементов И-ИЛИ, блок эпемен-ч тов И внешних устройств и блок дешифраторов микроопераций, вход которого подключен ко входу номера операционного блока, а выход соединен с первыми входами блока элементов И внешних уст- ройств, блока элементов И регистра и регистра, вход которого подключен к магистральному входу операционного блока, а выход соединена со вторым входом блока, элементов и регистра и входом-выходом обменной информации операционного блока, соединенным с первым входом блока элементов И-ИЛИ, выход и второй; вход которого соединены соответственно с информационным №1ходом и входом информации от внешних устройств операционного блока, управляющий вход KOTopoixj соединен со вторым входом блока элементов И внешних устройств, выход которого соединен с выходом блока элементов И регистра и магистральным выходом операционного блока. Источники информации, принятые во внимание при экспертизе: 1.Патент США № 3665421, кл. 340-172. 5, 1972. . 2.Эскизный проект средств связи локальных информационнб« управляющих си -i стем (ЛИУС), НМ-2387, ИАТ АН СССР, М., 1967.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU1015384A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1989 |

|

SU1658166A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для контроля микропрограммного блока управления | 1984 |

|

SU1203526A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1019449A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

Авторы

Даты

1978-09-15—Публикация

1973-05-17—Подача